www.ti.com

SRIO Registers

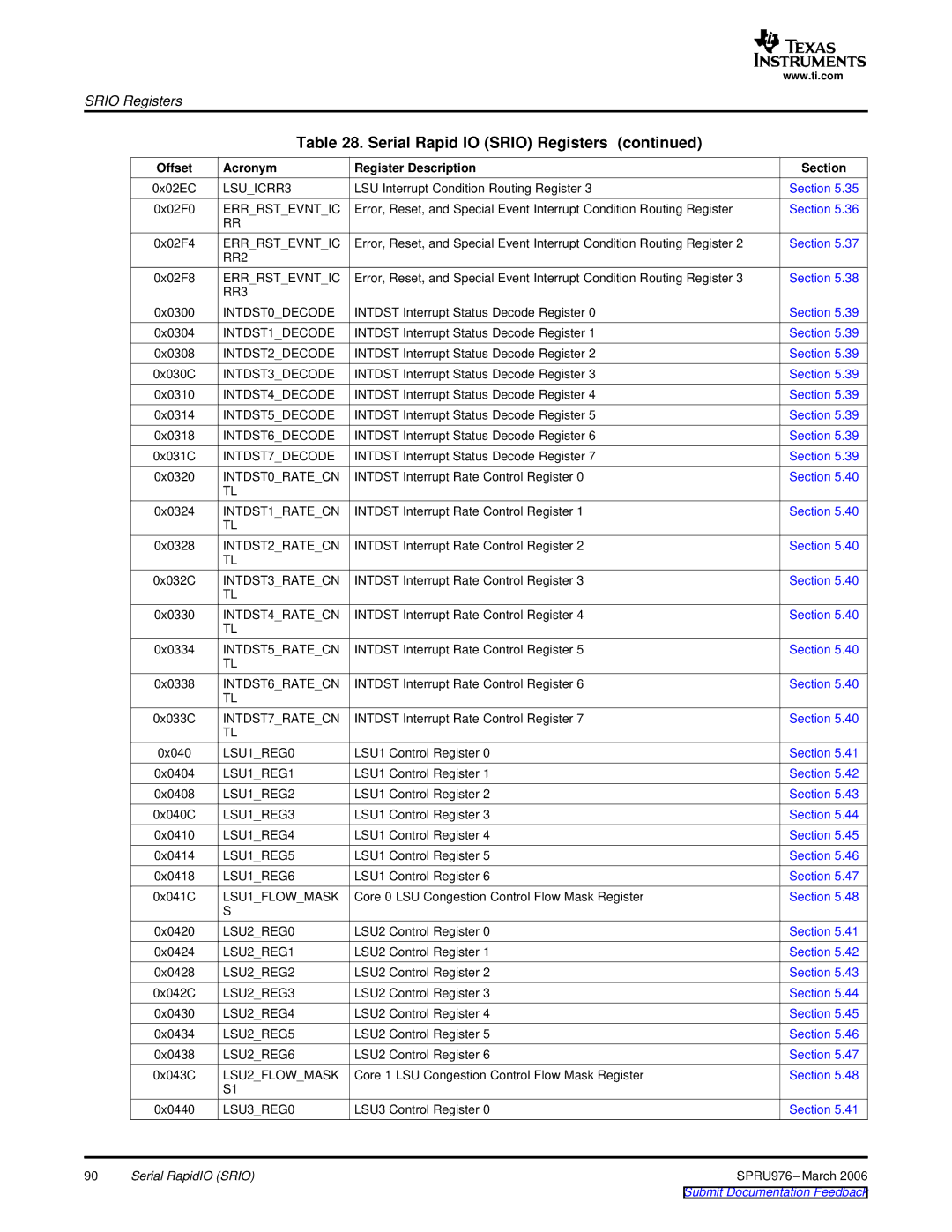

Table 28. Serial Rapid IO (SRIO) Registers (continued)

| Offset | Acronym | Register Description | Section |

| 0x02EC | LSU_ICRR3 | LSU Interrupt Condition Routing Register 3 | Section 5.35 |

| 0x02F0 | ERR_RST_EVNT_IC | Error, Reset, and Special Event Interrupt Condition Routing Register | Section 5.36 |

|

| RR |

|

|

| 0x02F4 | ERR_RST_EVNT_IC | Error, Reset, and Special Event Interrupt Condition Routing Register 2 | Section 5.37 |

|

| RR2 |

|

|

| 0x02F8 | ERR_RST_EVNT_IC | Error, Reset, and Special Event Interrupt Condition Routing Register 3 | Section 5.38 |

|

| RR3 |

|

|

| 0x0300 | INTDST0_DECODE | INTDST Interrupt Status Decode Register 0 | Section 5.39 |

| 0x0304 | INTDST1_DECODE | INTDST Interrupt Status Decode Register 1 | Section 5.39 |

| 0x0308 | INTDST2_DECODE | INTDST Interrupt Status Decode Register 2 | Section 5.39 |

| 0x030C | INTDST3_DECODE | INTDST Interrupt Status Decode Register 3 | Section 5.39 |

| 0x0310 | INTDST4_DECODE | INTDST Interrupt Status Decode Register 4 | Section 5.39 |

| 0x0314 | INTDST5_DECODE | INTDST Interrupt Status Decode Register 5 | Section 5.39 |

| 0x0318 | INTDST6_DECODE | INTDST Interrupt Status Decode Register 6 | Section 5.39 |

| 0x031C | INTDST7_DECODE | INTDST Interrupt Status Decode Register 7 | Section 5.39 |

| 0x0320 | INTDST0_RATE_CN | INTDST Interrupt Rate Control Register 0 | Section 5.40 |

|

| TL |

|

|

| 0x0324 | INTDST1_RATE_CN | INTDST Interrupt Rate Control Register 1 | Section 5.40 |

|

| TL |

|

|

| 0x0328 | INTDST2_RATE_CN | INTDST Interrupt Rate Control Register 2 | Section 5.40 |

|

| TL |

|

|

| 0x032C | INTDST3_RATE_CN | INTDST Interrupt Rate Control Register 3 | Section 5.40 |

|

| TL |

|

|

| 0x0330 | INTDST4_RATE_CN | INTDST Interrupt Rate Control Register 4 | Section 5.40 |

|

| TL |

|

|

| 0x0334 | INTDST5_RATE_CN | INTDST Interrupt Rate Control Register 5 | Section 5.40 |

|

| TL |

|

|

| 0x0338 | INTDST6_RATE_CN | INTDST Interrupt Rate Control Register 6 | Section 5.40 |

|

| TL |

|

|

| 0x033C | INTDST7_RATE_CN | INTDST Interrupt Rate Control Register 7 | Section 5.40 |

|

| TL |

|

|

| 0x040 | LSU1_REG0 | LSU1 Control Register 0 | Section 5.41 |

| 0x0404 | LSU1_REG1 | LSU1 Control Register 1 | Section 5.42 |

| 0x0408 | LSU1_REG2 | LSU1 Control Register 2 | Section 5.43 |

| 0x040C | LSU1_REG3 | LSU1 Control Register 3 | Section 5.44 |

| 0x0410 | LSU1_REG4 | LSU1 Control Register 4 | Section 5.45 |

| 0x0414 | LSU1_REG5 | LSU1 Control Register 5 | Section 5.46 |

| 0x0418 | LSU1_REG6 | LSU1 Control Register 6 | Section 5.47 |

| 0x041C | LSU1_FLOW_MASK | Core 0 LSU Congestion Control Flow Mask Register | Section 5.48 |

|

| S |

|

|

| 0x0420 | LSU2_REG0 | LSU2 Control Register 0 | Section 5.41 |

| 0x0424 | LSU2_REG1 | LSU2 Control Register 1 | Section 5.42 |

| 0x0428 | LSU2_REG2 | LSU2 Control Register 2 | Section 5.43 |

| 0x042C | LSU2_REG3 | LSU2 Control Register 3 | Section 5.44 |

| 0x0430 | LSU2_REG4 | LSU2 Control Register 4 | Section 5.45 |

| 0x0434 | LSU2_REG5 | LSU2 Control Register 5 | Section 5.46 |

| 0x0438 | LSU2_REG6 | LSU2 Control Register 6 | Section 5.47 |

| 0x043C | LSU2_FLOW_MASK | Core 1 LSU Congestion Control Flow Mask Register | Section 5.48 |

|

| S1 |

|

|

| 0x0440 | LSU3_REG0 | LSU3 Control Register 0 | Section 5.41 |

90 | Serial RapidIO (SRIO) | SPRU976 | ||

|

|

| Submit Documentation Feedback | |