www.ti.com

Logical/Transport Error Handling and Logging

3Logical/Transport Error Handling and Logging

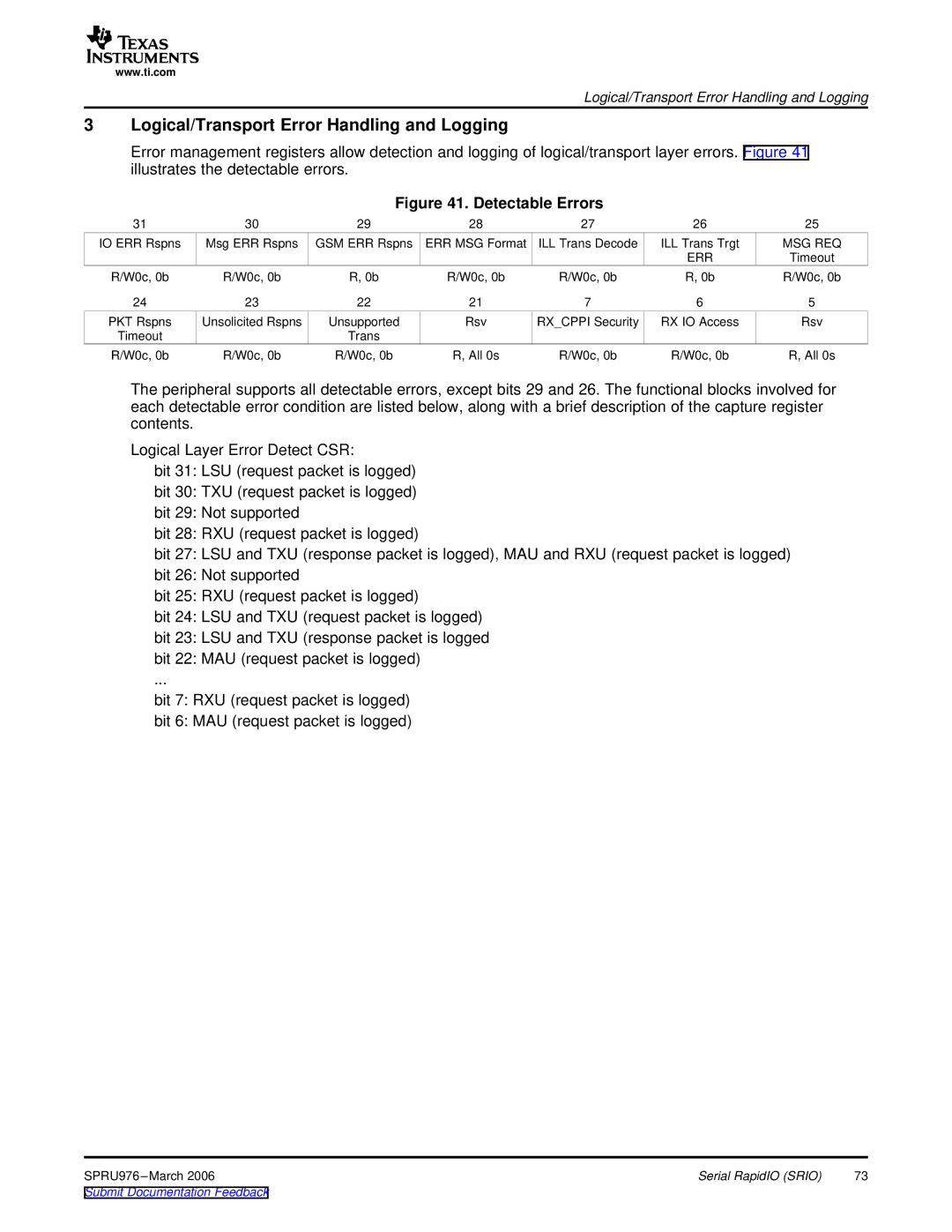

Error management registers allow detection and logging of logical/transport layer errors. Figure 41 illustrates the detectable errors.

Figure 41. Detectable Errors

31 | 30 | 29 | 28 | 27 | 26 | 25 |

IO ERR Rspns | Msg ERR Rspns | GSM ERR Rspns | ERR MSG Format | ILL Trans Decode | ILL Trans Trgt | MSG REQ |

|

|

|

|

| ERR | Timeout |

R/W0c, 0b | R/W0c, 0b | R, 0b | R/W0c, 0b | R/W0c, 0b | R, 0b | R/W0c, 0b |

24 | 23 | 22 | 21 | 7 | 6 | 5 |

PKT Rspns | Unsolicited Rspns | Unsupported | Rsv | RX_CPPI Security | RX IO Access | Rsv |

Timeout |

| Trans |

|

|

|

|

R/W0c, 0b | R/W0c, 0b | R/W0c, 0b | R, All 0s | R/W0c, 0b | R/W0c, 0b | R, All 0s |

The peripheral supports all detectable errors, except bits 29 and 26. The functional blocks involved for each detectable error condition are listed below, along with a brief description of the capture register contents.

Logical Layer Error Detect CSR:

bit 31: LSU (request packet is logged)

bit 30: TXU (request packet is logged)

bit 29: Not supported

bit 28: RXU (request packet is logged)

bit 27: LSU and TXU (response packet is logged), MAU and RXU (request packet is logged)

bit 26: Not supported

bit 25: RXU (request packet is logged)

bit 24: LSU and TXU (request packet is logged)

bit 23: LSU and TXU (response packet is logged

bit 22: MAU (request packet is logged)

...

bit 7: RXU (request packet is logged)

bit 6: MAU (request packet is logged)

SPRU976 | Serial RapidIO (SRIO) | 73 |