www.ti.com

SRIO Registers

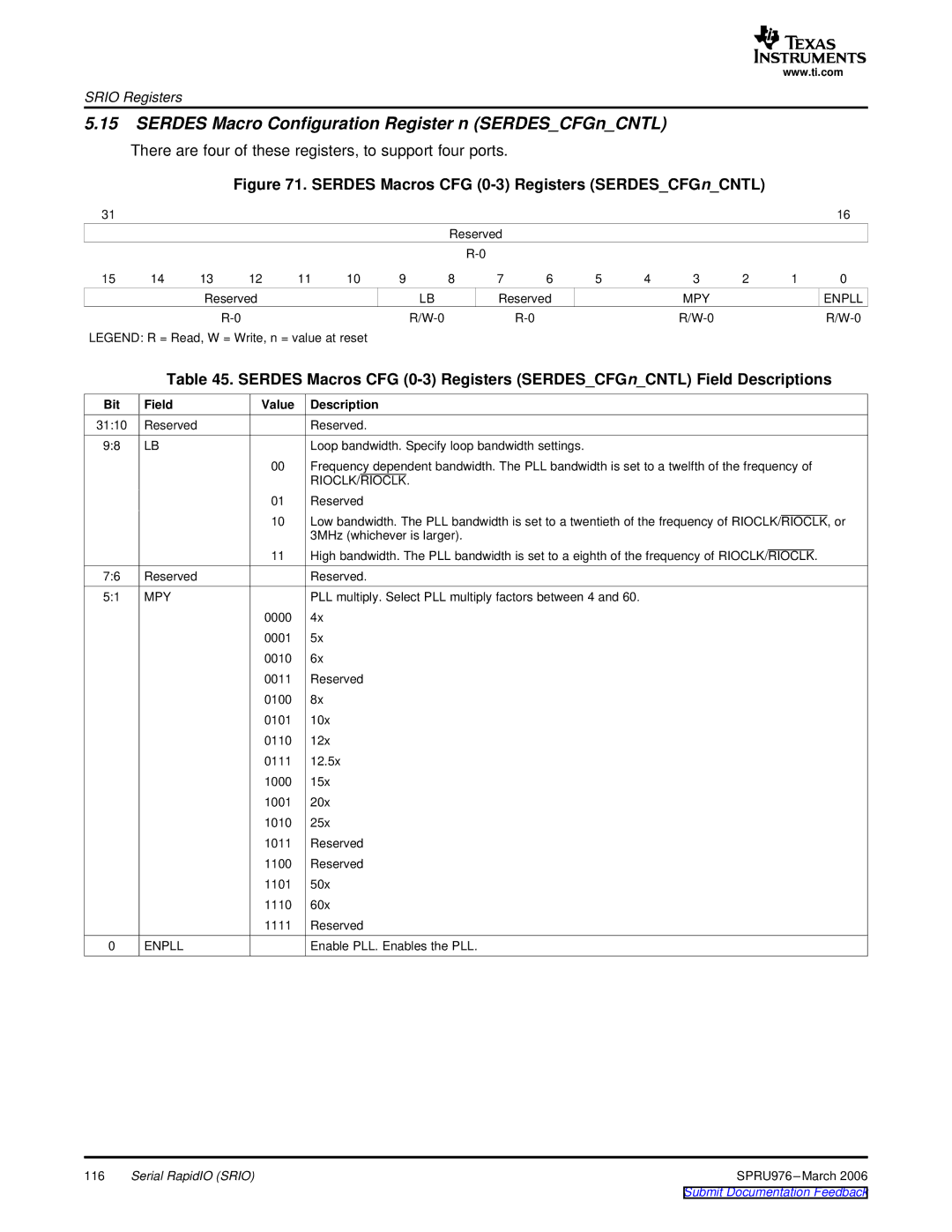

5.15SERDES Macro Configuration Register n (SERDES_CFGn_CNTL)

There are four of these registers, to support four ports.

Figure 71. SERDES Macros CFG (0-3) Registers (SERDES_CFGn_CNTL)

31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 16 |

|

|

|

|

|

|

| Reserved |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

| Reserved |

|

| LB |

| Reserved |

|

| MPY |

|

| ENPLL | ||

|

|

|

|

|

|

|

|

|

|

| |||||

LEGEND: R = Read, W = Write, n = value at reset

Table 45. SERDES Macros CFG

Bit | Field | Value | Description |

31:10 | Reserved |

| Reserved. |

9:8 | LB |

| Loop bandwidth. Specify loop bandwidth settings. |

|

| 00 | Frequency dependent bandwidth. The PLL bandwidth is set to a twelfth of the frequency of |

|

|

| RIOCLK/RIOCLK. |

|

| 01 | Reserved |

|

| 10 | Low bandwidth. The PLL bandwidth is set to a twentieth of the frequency of RIOCLK/RIOCLK, or |

|

|

| 3MHz (whichever is larger). |

|

| 11 | High bandwidth. The PLL bandwidth is set to a eighth of the frequency of RIOCLK/RIOCLK. |

7:6 | Reserved |

| Reserved. |

5:1 | MPY |

| PLL multiply. Select PLL multiply factors between 4 and 60. |

|

| 0000 | 4x |

|

| 0001 | 5x |

|

| 0010 | 6x |

|

| 0011 | Reserved |

|

| 0100 | 8x |

|

| 0101 | 10x |

|

| 0110 | 12x |

|

| 0111 | 12.5x |

|

| 1000 | 15x |

|

| 1001 | 20x |

|

| 1010 | 25x |

|

| 1011 | Reserved |

|

| 1100 | Reserved |

|

| 1101 | 50x |

|

| 1110 | 60x |

|

| 1111 | Reserved |

0 | ENPLL |

| Enable PLL. Enables the PLL. |

116 | Serial RapidIO (SRIO) | SPRU976 |

|

| Submit Documentation Feedback |