90000847C Release date 10 April

NS9215 Hardware Reference

Page

Page

Page

Contents

A p t e r 3 W o r k i n g w i t h t h e C P U

102

105

A p t e r 4 S y s t e m C o n t r o l M o d u l e 137

141

A p t e r 5 M e m o r y C o n t r o l l e r 203

Sram

Bit wide configuration 228 229

Hardware Reference NS9215

HT1

315

A p t e r 7 E x t e r n a l D M a 339

Hardware Reference NS9215

A p t e r 9 I / O H u b M o d u l e 363

Hardware Reference NS9215

A p t e r 1 1 S e r i a l C o n t r o l D u l e H D L C 415

Hardware Reference NS9215

A p t e r 1 4 R e a l T i m e C l o c k M o d u l e 459

A p t e r 1 6 T i m i n g 479

A p t e r 1 7 P a c k a g i n g 513

Hardware Reference NS9215

Heading Description

Pinout

M o r y b u s i n t e r f a c e

Pin Signal Description

N O U T 2 6

H e r n e t i n t e r f a c e M a C

Pin Signal

Sdram RAS

Sdram CAS

N e r a l p u r p o s e I / O G P I O

CTS Uart a

DCD Uart a

DSR Uart a

RXD Uart a

CTS Uart C

DCD / TXC Uart C

I2C SCL

Picdbgdataini

CTS Uart B

DCD Uart B

DSR Uart B

RXD Uart B

RXD Uart D

DSR Uart D

RI Uart D

TXC / DTR Uart D

Pin Signal Description

PIC1CLKO

PIC1CLKI

Pin Signal Description

PIC0CLKO

PIC0CLKI

Pin Signal Description

Pin Signal Description

Pin Signal Description

I/O OD

S t e m c l o c k

System clock drawing

S t e m m o d e

RTC clock and battery backup drawing

Sysmode2 Sysmode1 Sysmode0 Description

SPI YES

S t e m r e s e t

A G T e s t

Adcvss

POR VSS

R a n d b a t t e r y b a c k e d l o g i c

GND

W e r a n d g r o u n d

Power and ground

N t r o l a n d S t a t u s r e g i s t e r s

Address Description Access Reset value

System memory bus I/O control

Register address Map

Control and Status registers

I O C o n f i g u r a t i o n r e g i s t e r s

Gpio configuration options

Bits Mnemonic Description

Configuration Register #1

Configuration Register #0

Bits Access Mnemonic Reset Description

Address A0902000

Configuration Register #3

Configuration Register #2

Address A0902008

Address A090200C

Configuration Register #5

Configuration Register #4

Address A0902010

Address A0902014

Configuration Register #7

Configuration Register #6

Address A0902018

Address A090201C

Configuration Register #9

Configuration Register #8

Address A0902020

Address A0902024

Configuration Register #11

Configuration Register #10

Address A0902028

Address A090202C

Configuration Register #13

Configuration Register #12

Address A0902030

Address A0902034

Configuration Register #15

Configuration Register #14

Address A0902038

Address A090203C

Configuration Register #17

Configuration Register #16

Address A0902040

Address A0902044

Configuration Register #19

Configuration Register #18

Address A0902048

Address A090204C

Configuration Register #21

Configuration Register #20

Address A0902050

Address A0902054

Configuration Register #23

Configuration Register #22

Address A0902058

Address A090205C

Configuration Register #25

Configuration Register #24

Address A0902060

GPIOAddress A0902064

Address A0902068

Configuration Register #26

Gpio Control

I O C o n t r o l r e g i s t e r s

Address A090206C

Address A0902070

Address A0902074

Address A0902078

Gpio Status

I O S t a t u s r e g i s t e r s

Address A0902080

Address A0902084

Address A0902088

M o r y B u s C o n f i g u r a t i o n r e g i s t e r

Address A090208C

CS1

CS0

CS2

CS3

High data bus pullup control

Apudis

Memory Bus Configuration register

About the processor

Working with the CPU

S t r u c t i o n s e t s

Process block Diagram

Arm926EJ-S

ARM instruction set Thumb instruction set

Java instruction set

Accessing CP15 registers

ARM926EJ-S system addresses Address manipulation example

Mnemonics for these instructions are

Terms and abbreviations

Term Abbreviation Description

For reads

Register summary

Be ZERO, does not cause any physical damage to the chip

Register Reads Writes

TLB

Writing to register R0 is Unpredictable

This is the contents of the ID code register

R0 ID code

Any value other than 1 or 2. Note this example

Dsize and Isize fields

Cache type register and field description

Field contains these bits

Field Description

Size field Cache size

O n t r o l r e g i s t e r

Assoc field Associativity

Len field Cache line length

Bit functionality

Control register

Bits Name Function

DCache behavior

ICache

Cache

Behavior

Access permissions and instructions

CRm and opcode2 fields should be Zero when writing to R2

R a n s l a t i o n T a b l e B a s e r e g i s t e r

O m a i n a c c e s s C o n t r o l r e g i s t e r

Access instructions

Fault S t a t u s r e g i s t e r s

E g i s t e r

Register bits

Status and domain fields

Fault a d d r e s s r e g i s t e r

Priority Source Size Status Domain

Function Description

A c h e O p e r a t i o n s r e g i s t e r

Function/operation Data format Instruction

Cache operation functions

MVA

Modified virtual address format MVA Set/Way format

Set/Way example Test and clean DCache instructions

L B O p e r a t i o n s r e g i s t e r

Test, clean, and invalidate DCache instruction

Unpredictable

Operation Data Instruction

Modified virtual address format MVA

A c h e L o c k d o w n r e g i s t e r

Cache ways

That allows you to control each cache way independently

Instruction or data lockdown register

Access

Instructions

Modifying the Cache Lockdown register Register format

For each of the cache lines to be locked down in cache way

0 T L B L o c k d o w n r e g i s t e r

Cache unlock procedure

Bit

Which region the TLB entry is placed

3 P r o c e s s I D r e g i s t e r

1 a n d R 1 2 r e g i s t e r s

Programming instructions Sample code sequence

Use these instructions to program the TLB Lockdown register

Performing a fast context switch

Fcse PID register Access instructions

Register format This is the format of the Fcse PID register

Function Data ARM instruction

Accessing reading or writing this register is reserved

Context ID register Access instructions

4 r e g i s t e r

5 T e s t a n d d e b u g r e g i s t e r

M o r y M a n a g e m e n t U n i t M M U

MMU Features

State space servo control

Protection scheme

Access permissions and domains Translated entries

Register Bits Description

MMU program accessible registers Address translation

TTB register Format

Translation table base

First-level fetch

Table walk process

First-level descriptor

First-level fetch concatenation and address

Table descriptors

Bits Section Coarse Fine Description

Section descriptor Format

Value Meaning Description

Fine page table

Section descriptor Bit description

Descriptor

Bits Description

113

Second-level descriptor pages

Second-level descriptor Second-level descriptor format

Second-level descriptor least significant bits

Second-level descriptor bit assignments

Bits Large Small Tiny Description

Translation sequence for large page references

Translating sequence for small page references

References

Translation Sequence for tiny

Level descriptor

More information

U Fault s a n d C P U a b o r t s

Domain Fault Address register

Priority encoding table Fault Address register FAR

FAR values for Multi-word

Transfers

Specifying access permissions

Compatibility issues

Interpreting access permission bits

M a i n a c c e s s c o n t r o l

Privileged permissions User permissions

Fault c h e c k i n g s e q u e n c e

No access 00 Reserved Check domain status

Fault checking sequence

A b l i n g a n d d i s a b l i n g t h e M M U

T e r n a l a b o r t s

Enabling

Disabling

B s t r u c t u r e

C h e s a n d w r i t e b u f f e r

Cache features

Write buffer Enabling the caches

Settings

Bit settings

R1 register C and M bits for DCache

DCache

Description ARM926EJ-S behavior Table C Table B Bit

C h e M V a a n d S e t / W a y f o r m a t s

Generic, virtually indexed, virtually addressed cache

Cache format

ARM926EJ-S

This figure

N c a c h a b l e i n s t r u c t i o n f e t c h e s

For example, with a 4-way cache a =

Self-modifying code

AHB behavior Instruction Memory Barrier

Sample IMB sequences

Noncachable instruction fetches

S i n t e r c o n n e c t i o n

Features

S t e m b u s a r b i t e r

Until the transaction completes

Ownership

Master will not occupy the system bus

Locked bus sequence Relinquishing the bus

Split transfers Arbiter configuration example

Address range Size System functions

D r e s s d e c o d i n g

O g r a m m a b l e t i m e r s

Software watchdog timer

Master Name Hmaster30 assignment

N e r a l p u r p o s e t i m e r s / c o u n t e r s

Gptc characteristics Control field

Source clock frequency

S i c P W M f u n c t i o n

Bit mode options

A d r a t u r e d e code r f u n c t i o n

H a n c e d P W M f u n c t i o n

Sample enhanced PWM waveform

NC No change CW Clockwise CCW Counter clockwise Err Error

Input signals

Quadrature Encoding truth

CCW

Timer support

Testing signals

Monitors how far the encoder has moved Typical application

Digital filter

FIQ interrupts

T e r r u p t c o n t r o l l e r

IRQ interrupts

Vector

IRQ FIQ

IRQ characteristics Interrupt sources

Interrupt ID Interrupt source

Interrupt sources are assigned as shown

L c o n f i g u r a t i o n

N f i g u r a b l e s y s t e m a t t r i b u t e s

Configuring the powerup settings

PLL configuration and control system block diagram

O t s t r a p i n i t i a l i z a t i o n

Pin name Configuration bits

Offset 3124 2316 158

S t e m c o n f i g u r a t i o n r e g i s t e r s

155

Isaddr

System Memory Chip Select 0 Dynamic Memory Mask

C 0 , B R C 1 , B R C 2 , a n d B R C 3 r e g i s t e r s

N e r a l a r b i t e r C o n t r o l r e g i s t e r

Address A090

Register

Channel enable bit

B Error D e t e c t S t a t u s

Channel allocation Register Register bit assignment

This is how the channels are assigned in the four registers

EDS1

Address A090 001C

Not reset CPU data error

Not reset CPU instruction error

Not reset AHB error response

Transaction type write or read

AHB Slave Error Response Detect Config

AHB Error Interrupt Clear

M e r M a s t e r C o n t r o l r e g i s t e r

EIC

Timer 9 low step enable

Timer 9 reload step enable

Timer 9 high step enable

Timer 8 reload step enable

Addresses A090 0190 / 0194 / 0198 / 019C / 01A0

M e r 0 4 C o n t r o l r e g i s t e r s

Capture and compare mode functions

Timer enable

Debug mode

Timer clock select

Address A090 01A4

M e r 5 C o n t r o l r e g i s t e r

TM2

Reload mode

Addresses A090 01A8 / 01AC / 01B0 / 01B4

M e r 6 9 C o n t r o l r e g i s t e r s

D3118 Reserved D1716

M e r 6 9 H i g h r e g i s t e r s

M e r 6 9 L o w r e g i s t e r s

M e r 6 9 R e l o a d S t e p r e g i s t e r s

M e r 6 9 H i g h a n d L o w S t e p r e g i s t e r s

High step direction

High step

Reload step

Reload step direction

M e r 0 9 R e a d a n d C a p t u r e r e g i s t e r

Interrupt Vector Address register

Individual register mapping

Register 3124 2316 1508 0700

A D D R r e g i s t e r

Interrupt enable

Invert

Interrupt type

T e r r u p t S t a t u s a c t i v e

Interrupt service routine address

Interrupt status active

ISA

F t w a r e W a t c h d o g C o n f i g u r a t i o n

T e r r u p t S t a t u s R a w

Address A090 016C

Israw

Software watchdog timer clock select

Software watchdog enable

F t w a r e W a t c h d o g T i m e r

Software watchdog interrupt clear

O c k C o n f i g u r a t i o n r e g i s t e r

Watchdog timer

Address A090 017C

Max clock scale control

Clock scale control

CPU clock select

Memory clock out

IO hub

D u l e R e s e t r e g i s t e r

Ethernet MAC

Reset status

Module Reset register resets each module on the AHB bus

RST Stat

I2C

Miscellaneous System Configuration and Status register

Endian mode

Boot mode

Misaligned bus address response mode

Internal register access mode bit

PLL frequency formula Register Register bit assignment

L C o n f i g u r a t i o n r e g i s t e r

PLL bypass

Address A090 018C

W e r M a n a g e m e n t

Intid

Interrupt ID

New designs should not use this bit

Deprecated Chip sleep enable

Hardware clock scale control

Sdram self refresh control

RTC wakeup

CPU wake interrupt clear

I2C wakeup

SPI wakeup

Address A090 022C

B B u s a c t i v i t y S t a t u s

Addresses A090 01D0 / 01D4

Registers

Chip select 0 disable

Addresses A090 01D8 / 01DC

Chip select 0 base

Addresses A090 01E0 / 01E4

Chip select 1disable

Chip select 1 base

Addresses A090 01E8 / 01EC

Chip select 2 disable

Chip select 2 base

Addresses A090 01F0 / 01F4

Chip select 3 disable

Chip select 3 base

Chip select 0 mask

Addresses A09001F8 / 01FC

Addresses A090 0200

Chip select 1 disable

Addresses A090 0208 / 020C

N I D r e g i s t e r

STS

Genid

Status

CLR

C M o d u l e C o n t r o l r e g i s t e r

RTC standby mode status

RTC Module Control register controls the RTC module

Polarity

RTC clock ready interrupt status

RTC standby mode

RTC module interrupt status

RTC clock ready interrupt clear

RTC Module Control register

With and without asynchronous page mode

Memory controller provides these features

Static memory features, such as

Amba 32-bit AHB compliancy

W p o w e r o p e r a t i o n

M o r y m a p

Power-on reset memory map

Example Boot from flash Sdram remapped after boot

A t i c m e m o r y c o n t r o l l e r

Device Write protect Mode Buffer

ROM

Sram

Be aware

Write protection Extended wait transfers

A t i c m e m o r y i n i t i a l i z a t i o n

Access sequencing and memory width Wait state generation

Memory mapped peripherals

Output enable programmable delay

Programmable enable

A t i c m e m o r y r e a d c o n t r o l

ROM, SRAM, and Flash

External memory read transfer with two wait states

External memory read transfer with zero wait states

Timing parameter Value

WAITRD2 WAITOEN0 WAITPAGEN/A WAITWRN/A

WAITENN/A WAITTURNN/A

External memory read transfers with zero wait states

Burst of two wait states with fixed length

Burst of zero wait states with fixed length

Y n c h r o n o u s p a g e m o d e r e a d

External memory page mode read transfer

WAITRD2 WAITOEN0 WAITPAGE1 WAITWRN/A WAITWENN/A WAITTURNN/A

External memory 32-bit burst read from 8-bit memory

Timing parameters Value

WAITRD0 WAITOEN0 WAITPAGE0 WAITWRN/A WAITWENN/A WAITTURNN/A

A t i c m e m o r y w r i t e c o n t r o l

Write enable programming delay

Wait states added between external read and write transfers

External memory write transfer with zero wait states

External memory write transfer with two wait states

WAITRDN/A WAITOENN/A WAITPAGEN/A WAITWR0 WAITWEN0 WAITTURN0

S t u r n a r o u n d T i m i n g a n d p a r a m e t e r s

S t u r n a r o u n d

Read followed by write with no turnaround

WAITRD0 WAITOEN0 WAITPAGEN/A WAITWR0 WAITWEN0 WAITTURN0

Read followed by a write with two turnaround cycles

Write followed by a read with no turnaround

WAITRD0 WAITOEN0 WAITPAGEN/A WAITWR0 WAITWEN0 WAITTURN2

T e l a n e c o n t r o l

D r e s s c o n n e c t i v i t y

Memory banks constructed from 16-bit memory

Memory banks constructed from 16-or 32-bit memory devices

2Mx32 ROM

N a m i c m e m o r y c o n t r o l l e r

Access sequencing and memory width

R a M I n i t i a l i z a t i o n

Left-shift value -bit wide data bus Sdram RBC

Device size Configuration Load Mode register left shift

Bit Parameter Parameter description

256M 8M x 16M x 32M x 512M 64M x

Signal 16M device 64M device 128M 256M 512M

Bit wide Configuration

Device Signal

Left-shift value -bit wide data bus Sdram BRC

BA1

BA0

Register map

G i s t e r s

Only. Bursting is not allowed

Address Register Description

TRWL, tRDL

N t r o l r e g i s t e r

Reset values

Address A070

Low-power mode

Bits Access Mnemonic Description

Memory controller enable

Address mirror

N f i g u r a t i o n r e g i s t e r

A t u s r e g i s t e r

Self-refresh acknowledge Srefack

Write buffer status

END

N a m i c M e m o r y C o n t r o l r e g i s t e r

Dynamic memory clock enable

Sync/Flash reset/power down signal dypwrn

Sdram initialization

Self-refresh request Srefreq

Refresh

Refresh timer

Read data strategy

Active to precharge command period tRAS

Precharge command period tRP

RAS

Srex

Address A070 003C

Self-refresh exit time tSREX

APR

Last-data-out to active command time tAPR

DAL

Data-in to active command tDAL or tAPW

Address A070 004C

Active to active command period tRC

RFC

Auto-refresh period and auto-refresh to active command

Period

XSR

Exit self-refresh to active time command

RRD

Load mode register to Active Command Time

Active Bank a to Active Bank B

MRD

A t i c M e m o r y E x t e n d e d W a i t r e g i s t e r

External wait timeout

Example

Address A070 0100 / 0120 / 0140

Bdmc

Write protect

Address mapping

AM1

Address mapping

Memory Configuration

For the Dynamic

119 Description

For a chip select connected to Select this mapping

Address A070 0104 / 0124 / 0144

CAS

RAS latency active to read/write delay

CAS latency

Do not modify

Psmc

Buffer enable

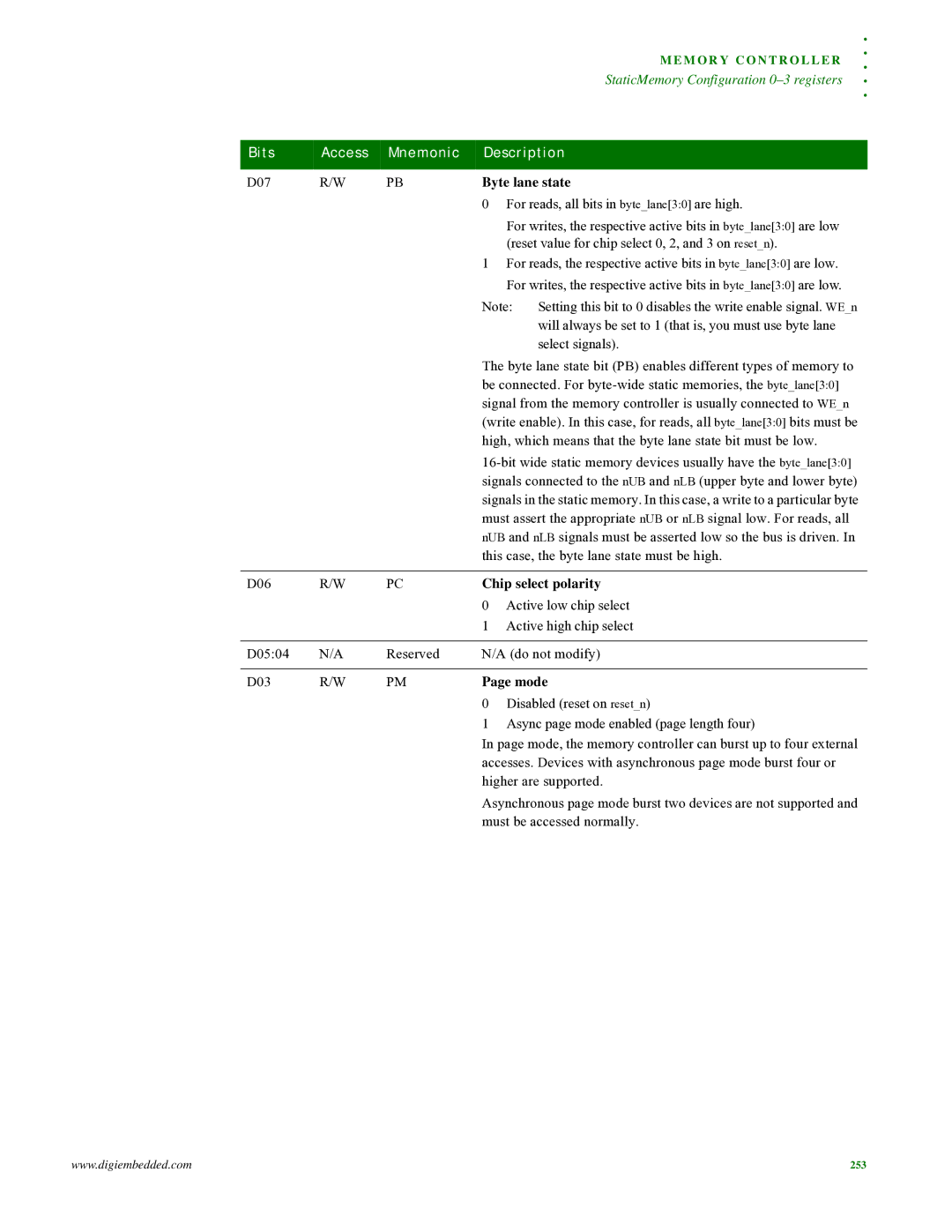

Bsmc

Extended wait

Chip select polarity

Byte lane state

Mode

Bmode

Burst mode

Memory width

Wait output enable Waitoen

Wait write enable Waitwen

Address A070 0208 / 0228 / 0248

Wwen

Read first access wait state Waitrd

Nonpage mode read wait states or asynchronous page mode

A t i c M e m o r y R e a d D e l a y 0 3 r e g i s t e r s

Wtrd

Wtpg

Asynchronous page mode read after the first wait state

Wtwr

Address A070 0218 / 0238 / 0258

Write wait states Waitwr

Bus turnaround cycles Waitturn

Wttn

StaticMemory Turn Round Delay 0-3 registers

Ethernet Communication Module

Features Common acronyms

Ethernet communications module

H e r n e t M a C

Feature Description

MAC module block diagram Features

PHY interface mappings

A t i o n a d d r e s s l o g i c S a L

Station address logic

Media Independent Interface

MAC receiver

A t i s t i c s m o d u l e

Ethernet front- end module EFE

H e r n e t f r o n t e n d m o d u l e

Receive packet processor

Transmit packet processor

C e i v e p a c k e t p r o c e s s o r

Receive buffer descriptor format

Transferring a frame to system memory

Receive buffer descriptor format description

Receive buffer descriptor field definitions

A n s m i t p a c k e t p r o c e s s o r

Transmit buffer Descriptor field

Transmit buffer descriptor format

Definitions

Transmitting a frame

Transmitted

Frame

Successfully

Unsuccessfully

T e r r u p t s

H e r n e t s l a v e i n t e r f a c e

Interrupt condition Description

S e t s

Bit field Register Active Default Modules reset State

Status bits

Filter entries

L t i c a s t a d d r e s s f i l t e r i n g

Multicast address Filter registers

Multicast address filtering example

Multicast address

O c k s y n c h r o n i z a t i o n

Filtering example

Writing to other registers

Register address Filter

Eintr

Rxdptr

Eintren

Txptr

Address A060

H e r n e t G e n e r a l C o n t r o l R e g i s t e r #

Enable receive DMA

Enable RX packet processing

Enable TX packet processing

Accept short 64 receive frames

Enable initialization of RX buffer descriptors

Enable transmit DMA

Etxdma

Erxinit

RX Fifo RAM access

MAC host interface soft reset

Align RX data

Insert transmit source address

H e r n e t G e n e r a l S t a t u s r e g i s t e r

Rxinit

H e r n e t T r a n s m i t S t a t u s r e g i s t e r

RX initialization complete

Broadcast frame transmitted

Frame transmitted OK

Multicast frame transmitted

TX abort late collision

Address A060 001C

H e r n e t R e c e i v e S t a t u s r e g i s t e r

Receive frame OK

Receive frame size in bytes

Receive broadcast frame

Receive multicast frame

C C o n f i g u r a t i o n R e g i s t e r #

Bits Access Mnemonic Reset Definition

Receive enable

Internal loopback

Excess deferral

Vlan pad enable

Auto detect pad enable

Pad/CRC enable

CRC enable

PAD operation Table for transmit

C k t o B a c k I n t e r P a c k e t G a p r e g i s t e r

Frames

Type

Half-duplex mode

Full-duplex mode

Address A060 040C

Back-to-back inter-packet-gap

Address A060

L l i s i o n W i n d o w / R e t r y r e g i s t e r

IPGR1

Non back-to-back inter-packet-gap part

Cwin

X i m u m F r a m e r e g i s t e r

Collision window

Retx

Maximum frame length

Reset MII management block

Rmiim

I M a n a g e m e n t C o m m a n d r e g i s t e r

Clocks field Settings

Clock select

Suppress preamble

Register bit

I M a n a g e m e n t a d d r e s s r e g i s t e r

If both Scan and Read are set, Scan takes precedence

Automatically scan for read data

I M a n a g e m e n t R e a d D a t a r e g i s t e r

I M a n a g e m e n t W r i t e D a t a r e g i s t e r

Address A060 042C

MII read data

I M a n a g e m e n t I n d i c a t o r s r e g i s t e r

Miilf

MII link failure

Read data not valid

A t i o n a d d r e s s r e g i s t e r s

Nvalid

Automatically scan for read data in progress

Register bit assignments for all three registers

A t i o n a d d r e s s F i l t e r r e g i s t e r

Station Address Register #1

Station Address Register #2

PRO

G i s t e r H a s h T a b l e s

PRM

PRA

Address Register Transmit and receive counters

A t i s t i c s r e g i s t e r s

TR1K

Receive byte counter A060 069C

Receive statistics Counters address

Receive packet counter A060 06A0

Address Register Receive counters

Receive multicast packet counter A060 06A8

Receive FCS error counter A060 06A4

Receive broadcast packet counter A060 06AC

Rbuo

Receive code error counter A060 06C4

Receive alignment error counter A060 06BC

Receive carrier sense error counter A060 06C8

Receive undersize packet counter A060 06CC

Transmit statistics counters address map

Receive jabber counter A060 06D8

Transmit byte counter A060 06E0

Address Register Transmit counters

Transmit packet counter A060 06E4

Transmit excessive collision packet counter A060

Transmit undersize frame counter A060

Transmit oversize frame counter A060

These are the General Statistics registers

Carry Register

C1MGV

C1MAX

C1RBY

C1RPK

Mask register

M1RBY

M1MGV

M1RPK

M1RFC

Mask register Register

Address A060 073C

0x00000000 RXA Buffer Descriptor Pointer

Address A060 0A04

RXB Buffer Descriptor Pointer

Address A060 0A0C

Address A060 0A08

RXC Buffer Descriptor Pointer

RXD Buffer Descriptor Pointer

Address A060 0A10

H e r n e t I n t e r r u p t S t a t u s r e g i s t e r

Rxovflstat

Rxbufc

Rxdonec

Rxdoneb

Rxdoned

Rxnobuf

Address A060 0A14

H e r n e t I n t e r r u p t E n a b l e r e g i s t e r

Address A060 0A18

Address A060 0A20

Address A060 0A1C

Address A060 0A24

Address A060 0A28

Address A060 0A30

Address A060 0A2C

Address A060 0A38

Address A060 0A34

Address A060 0A3C

F r e e B u f f e r r e g i s t e r

Rxfreed

Rxfreec

L t i c a s t a d d r e s s F i l t e r r e g i s t e r s

Address A060 0A5C

Address A060 0A58

Address A060 0A60

Address A060 0A64

L t i c a s t a d d r e s s M a s k r e g i s t e r s

Address A060 0A94

Address A060 0A90

Address A060 0A98

Address A060 0A9C

Address A060 0AB8

Address A060 0AB4

Address A060 0ABC

Address A060 0AC0

Offset+0

B u f f e r D e s c r i p t o r R a M

Offset+8

Offset+4

Offset+C

Address A060 2000 512 locations

M p l e h a s h t a b l e code

Pointer to buffer to store hash table

Pointer to hash table

337

Sample hash table code

A t r a n s f e r s

External DMA

A b u f f e r d e s c r i p t o r

DMA buffer descriptor diagram

Source address pointer Buffer length

Destination

S c r i p t o r l i s t p r o c e s s i n g

R i p h e r a l D M a r e a d a c c e s s

Use this equation to compute total access time

Determining the width of Pden Equation variables

Variable Definition

Peripheral DMA burst read access

Peripheral DMA single read access

R i p h e r a l D M a w r i t e a c c e s s

REQ signal

Peripheral DMA burst write access

REQ signal

Logic remains paused until the REQ signal is reasserted

Static ram chip select configuration

Done signal Special circumstances

A t i c R a M c h i p s e l e c t c o n f i g u r a t i o n

Register name Field Value Comment

A B u f f e r D e s c r i p t o r P o i n t e r

A C o n t r o l r e g i s t e r

Channel go

Channel enable

Source width

Destination width

Destination burst

Fly-by mode

Source address increment

State

Reset

Index

Normal completion interrupt pending

Error completion interrupt pending

Buffer not ready interrupt pending

Channel abort interrupt pending

A P e r i p h e r a l C h i p S e l e c t r e g i s t e r

Chip select

SEL

DMA Peripheral Chip Select register

Processes 32 bits at a time

AES

Is programmable for 128-, 192-, or 256-bit key lengths

Supports ECB, CBC, OFB, CTR, and CCM cipher modes

Key size Characteristic 128 192 256

Block diagram

S D M a b u f f e r d e s c r i p t o r

Data blocks

Source address pointer

AES buffer descriptor diagram

Source buffer length

Destination buffer length

Interrupt I bit Last L bit Full F bit

AES op code

B p r o c e s s i n g

C r y p t i o n

C , C F B , O F B , a n d C T R p r o c e s s i n g

CCM mode does not require an initialization vector

M m o d e

Nonce buffer

Contents

Bits

CCM mode

Hub Module

AHB slave

A c o n t r o l l e r

Interface

Servicing RX and FIFOs

Control14

Source address pointer Buffer length Control15 W

Control13 L

Control12 F

Status150

Control110

Not applicable

A n s m i t D M a e x a m p l e

Process

Pointer and Index

System Memory

Visual example

Uart a register Address map

Reserved

Uart B register Address map

Register Offset Description

Uart D register Address map

Uart C register Address map

AD register Address map

SPI register Address map

Reserved

I2C register Address map

IO Hardware Assist register

RTC register Address map

IO register Address map

Normal completion interrupt pending RX

Error completion interrupt pending RX

Buffer not ready interrupt pending RX

Channel abort interrupt pending RX

Error completion interrupt pending TX

RX Fifo service request interrupt pending

TX Fifo service request interrupt pending

RX Fifo overflow interrupt pending

D u l e D M a R X C o n t r o l

Flex I/O

Channel abort

Direct

Rxthrs

Rxbdp

RX Fifo threshold

D u l e D i r e c t M o d e R X S t a t u s F I F O

Full flag

D u l e D i r e c t M o d e R X D a t a F I F O

Indexen

D u l e D M a T X C o n t r o l

Txbdp

TX Fifo threshold

D u l e D i r e c t M o d e T X D a t a F I F O

TXD

D u l e D i r e c t M o d e T X D a t a L a s t F I F O

Txdl

384

Receive error conditions

Modem control signal support

Character gap timeout

DMA transfers to and from system memory

R m a l m o d e o p e r a t i o n

Example configuration

Uart module structure

Control register Field Value Comment

Baud rates

U d r a t e g e n e r a t o r

This table shows the baud rates achieved with CLKref set to

Divisor Baud rate

R c e d c h a r a c t e r t r a n s m i s s i o n

R d w a r e b a s e d f l o w c o n t r o l

M w a k e u p o n c h a r a c t e r r e c o g n i t i o n

Force character transmission procedure Collecting feedback

Address Register

A p p e r C o n t r o l a n d S t a t u s r e g i s t e r s

DLAB=0

DLAB=1

Rtsen

A p p e r C o n f i g u r a t i o n r e g i s t e r

RTS

Dtren

Receive character-based flow control

Software

Remote loopback

RTS control

T e r r u p t E n a b l e r e g i s t e r

Enable force complete

RS485 transceiver deassertion control

RS485 transceiver assertion control

Enable parity error

Enable overflow error

Enable frame error

Enable line break

T e r r u p t S t a t u s r e g i s t e r

Frame error

Parity error

Uart interrupt

Force complete

Character match3

Ring indicator

Character match2

Character match1

Transmit idle

Enable receive character gap timer

Receive idle

Write this field to

C e i v e B u f f e r G a P C o n t r o l r e g i s t e r

Enable transmit bit rate generation

Mask

Enable character match

Data

Flowstate

Flow control enable

Flow control state

FLOW4

FLOW2

M W a k e u p C o n t r o l r e g i s t e r

Force transmit enable

Read-only busy

Char

A n s m i t B y t e C o u n t

Enable

Address 90011034 / 90019034 / 90021034

Txcount

R T T r a n s m i t B u f f e r

R T R e c e i v e B u f f e r

Rbuff

R T B a u d R a t e D i v i s o r M S B

R T B a u d R a t e D i v i s o r L S B

Tbuff

Brdl

R T I n t e r r u p t E n a b l e r e g i s t e r

Enables modem status interrupt

Brdm

Edssi

Enables transmit holding register empty interrupt

Enables receive line status interrupt

Enables receive data available interrupt

Interrupt identification

R T F I F O C o n t r o l r e g i s t e r

Enable the TX and RX Fifo

R T L i n e C o n t r o l r e g i s t e r

Clear all bytes in the TX Fifo

Parity enable

Divisor latch access bit

Set break, if set TX data is set to

Stick parity, operates as follows

R T M o d e m C o n t r o l r e g i s t e r

Local loopback enable bit

R T L i n e S t a t u s r e g i s t e r

Automatic flow control

R T M o d e m S t a t u s r e g i s t e r

Trailing edge of RI indicator

Delta DCD indicator

Delta DSR indicator

Delta CTS indicator

Uart Modem Status register

Hdlc module structure

C e i v e a n d t r a n s m i t o p e r a t i o n s

T s

O c k i n g

Transmit operation

Transmitter underflow

Last byte bit Pattern table

T a e n c o d i n g

Encoding examples

Last byte bit pattern Valid data

Transitions

Dpll operation Adjustment ranges and output clocks

NRZ and Nrzi encoding Biphase-Level encoding

CLK

Address

Received or a buffer close event occurs, such as end

Enable invalid CRC

Enable Hdlc interrupt

Enable valid CRC

Local loopback

Rabort

Enable receive abort error

Hdlc interrupt

Receive abort error

Invalid CRC

Valid CRC

Hdata

L C D a t a R e g i s t e r

Hdata

Hmode

L C C o n t r o l R e g i s t e r

Clock source

L C C l o c k D i v i d e r L o w

Address 9002911C

L C C l o c k D i v i d e r H i g h

Divl

Divh

Clock enable

Programmable SPI mode 0, 1, 2, or

Four-wire interface RXD, TXD, CLK, CS

Master mode internal diagnostic loopback

Interface SPI module

SPI module structure

I c o n t r o l l e r

SPI mode SPI CLK Idle

Timing modes Clocking mode diagrams

I c l o c k i n g m o d e s

Capture edge Drive edge

I c l o c k g e n e r a t i o n

SPI master mode SPI slave mode

S t e m b o o t o v e r S P I o p e r a t i o n

Clock generation samples

Available Strapping options

Bootmode10 Address width

EEPROM/FLASH header

Entry Name

Entry Name Description

Time to completion

This is the primary SPI Configuration register

Configuration registers for the SPI module are located at

Enable master loopback mode

I C o n t r o l a n d S t a t u s r e g i s t e r s

Slave enable

SPI mode

O c k G e n e r a t i o n r e g i s t e r

Discard bytes

Enable clock generation

Bits Access Mnemonic Reset Divisor

Register programming steps

Use this register to define the data rate of the interface

D3102 Not used Write this field to D01

SPI master timing Parameters

I t i m i n g c h a r a c t e r i s t i c s

Parm Description Min Max Unit

SPI master timing diagram SPI slave timing parameters

SPI slave timing diagram

SPI timing characteristics

Y s i c a l I 2 C b u s

Interface timing, data structure, and error handling

I2C bus

Overview

Slave Description Addres Bit

E x t e r n a l a d d r e s s e s

C o m m a n d i n t e r f a c e

Command Name Description

M m a n d T r a n s m i t D a t a r e g i s t e r

R e g i s t e r s

Address 9005

RegisterDescription

2C Dlen port iicdlen

A t u s R e c e i v e D a t a r e g i s t e r

Provide new transmit data

Scmdl

S t e r a d d r e s s r e g i s t e r

Mcmdl

Irqcd

A v e a d d r e s s r e g i s t e r

Timing parameter for fast-mode Register

Address 9005 000C

Mask the interrupt to the ARM CPU irqdis

Master/slave interrupt codes

T e r r u p t codes

Code Name Master/slave Description

I2C master software driver I2C slave high level driver

F t w a r e d r i v e r

Master module normal mode, 16- bit

O w c h a r t s

Slave module normal mode, 16- bit

Real Time Clock Module

Address 9006

C G e n e r a l C o n t r o l r e g i s t e r

2 4 H o u r r e g i s t e r

12/24 clock mode operation

Calendar operation

Time date, hour, minute, second operation

HRT

M e r e g i s t e r

HRU

Address 9006 000C

L e n d a r r e g i s t e r

M e Alarm r e g i s t e r

Alarm E n a b l e r e g i s t e r

L e n d a r Alarm r e g i s t e r

Address 9006 001C

E n t F l a g s r e g i s t e r

Month event

Alarm event

Date event

Hour event

Month interrupt

Alarm interrupt

Date interrupt

Hour interrupt

T e r r u p t D i s a b l e r e g i s t e r

T e r r u p t E n a b l e S t a t u s r e g i s t e r

Address 9006 002C

N e r a l S t a t u s r e g i s t e r

General Status register

Structure

ADC module

ADC control block

C D M a p r o c e d u r e

C c o n t r o l a n d s t a t u s r e g i s t e r s

ADC configuration registers are located at offset

C C o n f i g u r a t i o n r e g i s t e r

Interrupt status

DMA enable

ADC channel select

C O u t p u t R e g i s t e r s 0

C C l o c k C o n f i g u r a t i o n r e g i s t e r

Wait

Dout

E c t r i c a l c h a r a c t e r i s t i c s

Parameter Symbola Rating Unit

Absolute maximum ratings

CPU / Memory clock Power

Parameter Symbol a Rating Unit

Recommended operating conditions

Inputs

E l e c t r i c a l c h a r a c t e r i s t i c s

Sym Parameter Conditiona Value Unit

Sym Parameter Value Unit

Ouputs

NC7SP17

Manufacturer Part Number Description

74LVC1G17GW

SN74LVC1G17DC

M o r y T i m i n g

Sdram burst read 16-bit

Sdram burst read 16 bit, CAS latency =

Sdram burst write 16 bit

Sdram burst read 32 bit

Sdram burst read 32 bit, CAS latency =

Sdram burst write 32-bit

Sdram load mode

Sdram refresh mode

Clock enable timing

Parm Description Min Max Unit

Static RAM read cycles with 0 wait states

Static RAM asynchronous page mode read, Wtpg =

Static RAM read cycle with configurable wait states

Static RAM sequential write cycles

Static RAM write cycle

Static write cycle with configurable wait states

CPU

Slow peripheral acknowledge timing

Slow peripheral acknowledge write

Slow peripheral acknowledge read

Ethernet MII timing

Ethernet timing

I2C timing

Standard Mode Fast Mode Parm Description Min Max Unit

Parm Description Min Max Unit Mod Not

SPI Timing

SPI master parameters

SPI slave parameters

Tbclk *8

SPI master mode2 and 3 2-byte transfer

SPI master mode 0 and 1 2-byte transfer

SPI slave mode 2 and 3 2-byte transfer

SPI slave mode 0 and 1 2-byte transfer

Parm Description Min Typ Unit

S e t a n d h a r d w a r e s t r a p p i n g t i m i n g

A G t i m i n g

O c k t i m i n g

Diagram below pertains to clock timing

System PLL reference clock Timing

Clock timing

C k a g e

Packaging

O c e s s o r D i m e n s i o n s

C K a G I N G

Processor Dimensions

V i s i o n C

V i s i o n B