82540EP/EM, 82541xx, 82544GC/EI, 82545GM/EM, 82546GB/EB,

Software Developer’s Manual

Date Version Comments

Initial Public Release

Software Developer’s Manual

Contents

TCP Segmentation Use of Multiple Data Descriptors

Software Developer’s Manual Vii

Power Management 129 Introduction to Power Management

10.1.3

203

13.4.25

13.7.10

Appendix 82540EP/EM and 82545GM/EM Differences

Xiv

Scope

Overview

Ethernet Controller Features

PCI Features

CSA Features 82547GI/EI Only

Network Side Features

Host Offloading Features

Additional Performance Features

Additional Ethernet Controller Features

Technology Features

Conventions

Related Documents

Memory Alignment Terminology

Register and Bit References

Architectural Overview

Introduction

LAN a LAN B

External Architecture

PHY

AGC, A/D

Eeprom Flash

ECHO, Next Fext

Microarchitecture

1 PCI/PCI-X Core Interface

2 82547GI/EI CSA Interface

DMA Engine and Data Fifo

4 10/100/1000 Mb/s Receive and Transmit MAC Blocks

5 MII/GMII/TBI/Internal SerDes Interface Block

6 10/100/1000 Ethernet Transceiver PHY

Eeprom Interface

DMA Addressing

Flash Memory Interface

Example 2-1. Byte Ordering

Little Endian Data Ordering

IA Byte # LSB MSB

Ethernet Addressing

Intel Architecture Byte Ordering

Interrupts

Hardware Acceleration Capability

Buffer and Descriptor Structure

Checksum Offloading

TCP Segmentation

Architectural Overview

Packet Address Filtering

Introduction

Packet Reception

Receive Descriptor Rdesc Layout

Receive Data Storage

Receive Descriptor Format

Receive Descriptor Status Field

Receive Status RDESC.STATUS Layout

PIF Ipcs Tcpcs RSV Ixsm EOP

Receive

Receive Descriptor Errors Field

Receive Errors RDESC.ERRORS Layout

RXE IPE Tcpe RSV

RSV SEQ

CXE

Receive Descriptor Special Field

Special Descriptor Field Layout

PRI CFI Vlan

PRI

Receive Descriptor Fetching

Receive Descriptor Fetching Algorithm

Receive Descriptor Write-Back

Receive Descriptor Queue Structure

Receive Descriptor Packing

Null Descriptor Padding

Receive Descriptor Ring Structure

Receive Interrupts

Receive Timer Interrupt

Receive Interrupt Delay Timer / Packet Timer Rdtr

Receive Interrupt Absolute Delay Timer Radv

Packet Delay Timer Operation State Diagram

Small Receive Packet Detect

8 82544GC/EI Receive Interrupts

Receive Packet Checksum Offloading

Receive Descriptor Minimum Threshold ICR.RXDMT

Receiver Fifo Overrun

Supported Receive Checksum Capabilities

Packet Type HW IP Checksum HW TCP/UDP Checksum Calculation

MAC Address Filter

GC/EI Supported Receive Checksum Capabilities

Packet Type HW IP Checksum HW TCP/UDP Checksum

Packet Type HW IP Checksum

Packet Transmission

SNAP/VLAN Filter

9.3 IPv4 Filter

9.4 IPv6 Filter

Transmit Data Storage

Transmit Descriptors

Transmit Descriptor Tdesc Layout Legacy Mode

Legacy Transmit Descriptor Format

Transmit Descriptor Tdesc Layout

Transmit Descriptor Legacy Descriptions

Transmit Descriptor Description Legacy

CMD

STA

CSS

Transmit Descriptor Command Field Format

10. Transmit Command TDESC.CMD Layout

IDE VLE Dext RSV

Ifcs EOP

Transmit Descriptor Status Field Format

11. Transmit Status Layout

Transmit Descriptor Special Field Format

12. Special Field TDESC.SPECIAL Layout

5 TCP/IP Context Transmit Descriptor Format

6 TCP/IP Context Descriptor Layout

13. Transmit Descriptor Tdesc Layout Type = 0000b

14. Transmit Descriptor Tdesc Layout

Transmit Description Descriptor Offload

6.1 TCP/UDP Offload Transmit Descriptor Command Field

Transmit Description

Tucmd

Dtyp

82544GC/EI only

15. Command Field TDESC.TUCMD Layout

IDE RSV Dext TSE TCP

16. Transmit Status Layout

7 TCP/IP Data Descriptor Format

6.2 TCP/UDP Offload Transmit Descriptor Status Field

Popts

17. Transmit Descriptor Tdesc Layout Type = 0001b

Popts RSV STA Dcmd Dtyp Dtalen

7.1 TCP/IP Data Descriptor Command Field

18. Command Field TDESC.DCMD Layout

IDE VLE Dext

TSE Ifcs EOP

Reserved

7.2 TCP/IP Data Descriptor Status Field

19. Transmit Status Layout

7.3 TCP/IP Data Descriptor Option Field

7.4 TCP/IP Data Descriptor Special Field

20. Packet Options Field TDESC.POPTS Layout

RSV Txsm Ixsm

Transmit Descriptor Ring Structure

21. Special Field TDESC.SPECIAL Layout

Transmit Descriptor Ring Structure

Transmit Descriptor Fetching

Transmit Descriptor Write-back

Transmit Interrupts

Delayed Transmit Interrupts

Assumptions

Transmission Process

TCP Segmentation Performance

Packet Format

TCP Segmentation Data Fetch Control

TCP/UDP Data FCS

TCP Segmentation Indication

3936

TCP Segmentation Use of Multiple Data Descriptors

TCP Partial Pseudo-Header Checksum

Options

IP and TCP/UDP Headers

Version IP Hdr

Offset High Header Checksum

Type of service Version IP Hdr Length Fragment

Fragment Offset Low

Destination Port Sequence Number

TCP Header

Length Checksum Urgent Pointer Options

Byte1 Byte0 Destination Port

Source Port Destination Port Length Checksum

Byte3 Byte2 Byte1 Byte0

17. UDP Pseudo Header Diagram for IPv4

Transmit Checksum Offloading with TCP Segmentation

9 IP/TCP/UDP Header Updating

19. Overall Data Flow

9.1 TCP/IP/UDP Header for the First Frame

9.2 TCP/IP/UDP Header for the Subsequent Frames

IP/TCP/UDP Transmit Checksum Offloading

9.3 TCP/IP/UDP Header for the Last Frame

Ipcss

Receive and Transmit Description

PCI Configuration

Mandatory PCI Registers

Address Description

PCI

Specification Update for the latest stepping information

Base Address Registers

Addr

All base address registers have the following fields

Field Bits Read Initial Description Write Value

Expansion ROM Base Address

Offset Space

Capabilities Linked List

Address Next Pointer

PCI definition for more details

Bits Initial Value Description

Status Register Layout

82547GI/EI

PCI-X Configuration Registers

PCI-X Capability ID

Next Capability

Byte Offset

PCI-X Command

Bits Read Initial

Write Value

Maximum Memory Read Byte Count. This register sets

Bits Read Intial Description Write Value

PCI-X Status

USC SCD

Command Register as follows

Reserved and Undefined Addresses

Message Signaled Interrupts1

Message Signaled Interrupt Configuration Registers

MSI Capability ID

Bits Read Initial Description Write Value 05h

Message Control

Commands

3.1.4 Message Address

3.1.5 Message Upper Address

3.1.6

Accepted PCI/PCI-X Command as a Target

PCI Commands Abr PCI-X Commands

Transaction Target PCI Commands PCI-X Commands

Transaction Cause PCI Commands PCI-X Commands

PCI/PCI-X Command Usage

Memory Write Operations

Master Write Command Usage Algorithm

MWI Bursts

PCI-X Command Usage

Memory Read Operations

MW Bursts

Rules for Memory Read Operations

Cache Line Information1

Outstanding Memory Read

Target Transaction Termination

LAN Disable

Interrupt Assignment 82547GI/EI Only

CardBus Application 82541PI/GI/EI Only

Eeprom Interface

General Overview

Stepping Vendor ID Device ID Description

Component Identification Via Programming Interface

Component Identification

Eeprom Device and Interface

Software Access

Signature and CRC Fields

Eeupdate Utility

Command Line Parameters

Eeprom Address Map1

Ethernet Controller Address Map

Word Used Bit Image

For the 82541xx and 82547GI

LAN a

82545GM 82540EP

82541xx and 82547GI/EI only

82546GB/EB only

82541xx

82545GM

82540EP/EM

ASF

Address Hi Byte Low Byte

Word Description Default HW Access

GC/EI and 82541ER Eeprom Address Map

Ethernet Address Words 00h-02h

Software Compatibility Word Word 03h

Software Compatibility Word Word 03h

Bit Name Description

SerDes Configuration Word 04h

Eeprom Image Version Word 05h

Compatibility Fields Word 05h 07h

PBA Number Word 08h, 09h

Initialization Control Word 1 Word 0Ah

Initialization Control Word 1 Word 0Ah

Subsystem ID Word 0Bh

Subsystem Vendor ID Word 0Ch

Device ID Word 0Dh, 11h1

Vendor ID Word 0Eh

Initialization Control Word 2 Word 0Fh

Initialization Control Word 2 Word 0Fh

82541PI/GI Only

Common Power Word 12h

Software Defined Pins Control Word 10h1, 20h

PHY Register Address Data Words 10h, 11h, and 13h 1Eh

OEM Reserved Words Words 10h, 11h, 13h 1Fh

Software Defined Pins Control Word 10h, 20h

Bit Description Default

CSA Port Configuration 2 Word 21h

CSA Port Configuration 2 Word 21h

20 D0 Power Word 22h high byte

21 D3 Power Word 22h low byte

Circuit Control Word 21h

Reserved Words 23h 2Eh

82541PI/GI/EI and 82547GI/EI Only

10. Initial Management Control Register Settings

Management Control Word 13h1, 23h2

SMBus Slave Address Word 14h1 low byte, 24h low byte

11. SMBus Slave Address

Initialization Control 3 Word 14h1 high byte, 24h high byte

12. Initialization Control

82546GB/EB uses INTB#

For Address 24h High Byte / LAN a

LED Configuration Defaults Word 2Fh2

Boot Agent Main Setup Options Word 30h

27 IPv4 Address Words 15h 16h1 and 25h 26h

28 IPv6 Address words 17h 1Eh1 and 27h 2Eh

15. Boot Agent Main Setup Options

BBS

Boot Agent Configuration Customization Options Word 31h

DBS

16. Boot Agent Configuration Customization Options Word 31h

SIG

Mode

DFU

Boot Agent Configuration Customization Options Word 32h

17. Boot Agent Configuration Customization Options Word 32h

18. IBA Capabilities

IBA Secondary Port Configuration Words 34h-35h

IBA Capabilities Word 33h

19. WOL Mode and Functionality Word 0Ah

20. WOL Mode and Functionality Word 20h

Checksum Word Calculation Word 3Fh

Eeprom Images

Parallel Flash Memory

21. Flash Memory Manufacturers

Manufacturer

Number

124

Flash Control and Accesses

Flash Interface Operation

Read Accesses

Write Accesses

Flash Buffer Write Cycle

128

Introduction to Power Management

Assumptions

Power States

D3cold support

Dr State

1.2 D0u State

1.4 D3

Timing

1.3 D0a D0 active

Power Up Off to Dr to D0u to D0a

Diagram #

Transition From D0a to D3 and Back Without PCI Reset

Transition from D0a to D3 and Back Without PCI Reset

Transition From D0a to D3 and Back with PCI Reset

RST#

PCI Reset Without Transition to D3

PCI Reset Sequence

PCI Power Management Registers

Bits Default Description

Capability ID Byte Offset = 0 RO

Next Item Pointer Byte Offset = 1 RO

Eeprom

Power Management Capabilities PMC 2 Bytes Offset = 2 RO

Reserved

Software Developer’s Manual 139

Pmcsrbse Bridge Support Extensions

3.6 Data Register

Byte Offset = 6 RO

Byte Offset = 7 RO

Advanced Power Management Wakeup

Wakeup

Acpi Power Management Wakeup

Directed Exact Packet

Wakeup Packets

Pre-Defined Filters

3.1.3 Broadcast

Directed Multicast Packet

3.1.4 Magic Packet*1

Offset Field Value Action Comment

Offset Field Value Action Comment Bytes

3.1.5 ARP/IPv4 Request Packet1

+ S a

+ D + S a

ARP

Directed IPv4 Packet1

Offset # of bytes Field Value Action Comment

Directed IPv6 Packet1

IPX Diagnostic Responder Request Packet Example1

Flexible Filter

+ S

+ D + S

Directed IPX Packet Example

3.4 IPv6 Neighbor Discovery Filter1

Wakeup Packet Storage

CRC

152

Ethernet Interface

Link Interfaces Overview

Internal SerDes Interface/TBI Mode- 1Gb/s1

1.2 8B10B Encoding/Decoding

Gmii 1 Gb/s

Code Groups and Ordered Sets

Code Group and Ordered Set Usage

Code OrderedSet

MII 10/100 Mb/s

Internal Interface1

Duplex Operation

Full Duplex

Half Duplex

Carrier Extension 1000 Mb/s Only

Packet Bursting

Auto-Negotiation and Link Setup1

Auto-Negotiation and Link Setup2

Auto-Negotiation

Link Configuration in Internal Serdes/TBI Mode1

Link Speed

TXCW.txConfigWord

Hardware Auto-Negotiation

Software Auto-Negotiation

Bit Description

Internal GMII/MII Mode

Forcing Link

Using Auto-Speed Detection ASD

Forcing Speed

Automatic Detection of Link Speed using SPD-IND

Duplex

MII Management Registers

Comments Regarding Forcing Link

Internal SerDes Mode1 Control Bit Resolution

Internal Serdes Mode1 Hardware Enabled

Internal Serdes1 Mode Software Enabled

Control Bit Effect on Control Bits

Internal Serdes Mode1 Auto-Negotiation Skipped

Internal PHY Mode Control Bit Resolution

GMII/MII Mode PHY Speed Indication

GMII/MII Mode Auto-Speed Detection

GMII/MII Mode Force Speed

Loss of Signal/Link Status Indication

Internal Serdes Mode

Internal PHY Mode

GMII/MII Mode Force Link

10/100 Mb/s Specific Performance Enhancements

Adaptive IFS1

Flow Control

MAC Control Frames & Reception of Flow Control Packets

10. Flow Control Registers

Register Name Description

3x MAC Control Frame Format

Discard Pause Frames and Pass MAC Control Frames

Transmission of Pause Frames

Software Initiated Pause Frame Transmission

External Control of Flow Control Operation1

802.1q Vlan Packet Format

1 802.1q Tagged Frames

Vlan Packet Format Comparison

Packet #Octets

Transmitting and Receiving 802.1q Packets

802.1q Vlan Packet Filtering

Adding 802.1q Tags on Transmits

Stripping 802.1q Tags on Receives

Packet Reception Decision Table

VFE

178

Configurable LED Outputs1

Selecting an LED Output Source

Polarity Inversion

Blink Control

Blink Control

182

PHY Functionality and Features

Auto-Negotiation

Register Update

Next Page Exchanges

11.2 MDI/MDI-X Crossover copper only

Status

Pin

1000BASE-T

Polarity Correction copper only

11.2.2 10/100 Downshift 82540EP/EM Only

Link Down Energy Detect copper only

PHY Power Management copper only

Cable Length Detection copper only

11.4.2 D3 State, No Link Required copper only

11.4.3 D3 Link-Up, Speed-Management Enabled copper only

11.4.4 D3 Link-Up, Speed-Management Disabled copper only

Mdio Control Mode

Initialization

Determining Link State

Overview of Link Establishment

Configuration Result

False Link

Forced Operation

Determining Duplex State Via Parallel Detection

Link Criteria

Auto Negotiation

Parallel Detection

11.7.1 1000BASE-T

Using SmartSpeed

Link Enhancements

11.7.3 10BASE-T

SmartSpeed

Low Power Operation

Pause And Asymmetric Pause Settings

Asmdir Settings Pause Setting

Management Data Interface

11.11 1000 Mbps Operation

Powerdown via the PHY Register

Smart Power-Down

DSP ECHO, Next 4DPAM5

Transmit Functions

Transmit Fifo

Spectral Shaper

Low-Pass Filter

Line Driver

Transmit/Receive Flow

Receive Functions

11.12 100 Mbps Operation

11.13 10 Mbps Operation

Descrambler

Viterbi Decoder/Decision Feedback Equalizer DFE

PHY Line Length Indication

202

12.2.1 PCI/PCI-X interface

Features of Each MAC

Introduction1

204

IO BAR

MAC Configuration Register Space

12.2.3 SDP, LED, INT# output

Eeprom Arbitration

Shared Eeprom

Eeprom Map

Flash Access Contention

Shared Flash

Values Sampled on Reset

Pin sampled LAN device controlled Enable/Disable

Interrupt Use

Power Reporting

Multi-Function Advertisement

Enabled

Summary

Interrupt Line Used

INTA#

Register Descriptions

Register Conventions

Memory-Mapped Access to Internal Registers and Memories

Memory-Mapped Access to Flash

Memory-Mapped Access to Expansion ROM

Memory and I/O Address Decoding

Ioaddr

Iodata

Offset Abbreviation Name Size

Ioaddr

Iodata Register Configurations

AD C/BE#30 Bits

Ethernet Controller Register Summary

Category Offset Abbreviation Name

82544GC/EI

82547GI/EI only

Ipat 82544GC

Xofftxc

Fcruc

PRC64

Gprc

Category

Abbreviation Name Register

82544GC/EI , 82541xx , or 82547GI/EI

To the 82544GC/EI , 82541xx , or 82547GI

PCI-X Register Access Split1

Ctrl 00000h R/W

Main Register Descriptions

Device Control Register

Ctrl Register Bit Description

Field Bits Initial Description Value

Speed

SLU

Ilos

Frcdplx

SDP0DATA

SDP1DATA

ADVD3WUC

Field Bits Initial Description

BEM = 0 64-bit mode Little-Endian

Device Status Register

Status 00008h R

Little-Endian Data Ordering

Tbimode

Status Register Bit Description

Txoff

Asdv

PCI66

Pcixmode

Pcixspd

EEPROM/Flash Control & Data Register

Eecd 00010h R/W

Eecd Register Bit Description

82544GC/EI Only

Eereq

Eegnt

Eepres

Eesize

Eeprom Read Register Bit Description

Eeprom Read Register1

Eerd 00014h RW

Eeprom Read Register Bit Description 82541xx and 82547GI/EI

Done Start

FLA 0001Ch R/W

Flash Access1

Flash Access FLA

Extended Device Control Register

Ctrlext 00018h, R/W

10. Ctrlext Register Bit Description

23 16

SDP6IODIR

SDP2IODIR

SDP7IODIR

Asdchk

Vreg Power

11. GPI to SDP Bit Mappings

Down

Linkmode

Swdpinshi

12 GC/EI Ctrlext Register Bit Description

Swdpiohi

CTRL.RST

13 GC/EI GPI to SDP Bit Mapping

MDI Control Register

Mdic 00020h R/W

14. MDI Control Register Bit Description

RSV PHY REG Data

Regadd

Phyadd

PHY Registers

15. PHY Register Bit Mode Definitions

Register Mode Description

Field Bits Description Mode HW Rst SW Rst

MSB

242

Enaxc

LSB

RO,L

Software Developer’s Manual 245

246

For the 82541xx and 82547GI/EI

82544GC/EI only 82541xx

Pause

82541xx 82547GI/EI 82541xx and 82547GI/EI only

82544GC/EI Only

ANEG3

ANEG2

RF1

Software Developer’s Manual 251

23. Link Partner Ability Register Base Page Bit Description1

82541xx and 82547GI/EI Only

24. PHY Link Page Ability Bit Description1

10BASE-T

100BASE-TX

1b 82541xx

Software Developer’s Manual 255

Bits Field Description Mode HW Rst SW Rst

Master

ANEG0

MASTER/SLAVE

ANEG1

258

Software Developer’s Manual 259

DIS

NLP

Preen

SFD

Software Developer’s Manual 263

264

Software Developer’s Manual 265

266

82541EI/82547GI B0 stepping

82541/GI/ER and 82547GI B1

268

HCD

NOK

Software Developer’s Manual 271

272

Field Bits Description Mode HW Rst

Ledactled

SPEED100LED

SPEED1000LED

276

Software Developer’s Manual 277

To Perform Operation MDI Read/Write Sequence

Documented MDI Register 30 Operations1

51. MDI Register 30 Operations

Flow Control Address Low

Flow Control Address High

Fcal 00028h R/W

Fcah 0002Ch R/W

Flow Control Type

Vlan Ether Type

FCT 00030h R/W

VET 00038h R/W

Flow Control Transmit Timer Value

Fcttv 00170h R/W

56. VET Register Bit Description

57. Fcttv Register Bit Description

58. Txcw Register Bit Description

Transmit Configuration Word Register1

Txcw 00178h R/W

Receive Configuration Word Register1

Rxcw 00180h R

59. Rxcw Register Bit Description

LED Control1

Ledctl 00E00h RW

ANC

LED1 ACTIVITY# LED0 LINKUP#

Mode Encodings for LED Outputs1

60. LED Control Bit Description1

61. Mode Encodings for LED Outputs

Mode Pneumonic State / Event Indicated

Packet Buffer Allocation

PBA 01000H R/W

62. PBA Register Bit Description

Field Bits Initial Value Description

63. ICR Register Bit Description

Interrupt Cause Read Register

ICR 000C0H R

RXT0

Mdac

Rxcfg

GPISDP6

Interval

Interrupt Throttling Register1

ITR 000C4h R/W

64. ICS Register Bit Description

Interrupt Cause Set Register

ICS 000C8h W

Interrupt Mask Set/Read Register

IMS 000D0h R/W

65. IMS Register Bit Description

To the 82544GC/EI

Interrupt Mask Clear Register

IMC 000D8h W

66. IMC Register Bit Description

Receive Control Register

Rctl 00100h R/W

67. Rctl Register Bit Description

SBP

MPE

LPE

LBM

Rdmts

BAM

Bsize

VFE

Cfien

Secrc

Pmcf

Bsex

XON Enable 82544GC/EI , 82541xx , and 82547GI/EI only

Flow Control Receive Threshold Low

Fcrtl 02160h R/W

68. Fcrtl Register Bit Description

69. Fcrth Register Bit Description

Flow Control Receive Threshold High

Fcrth 02168h R/W

Receive Descriptor Base Address Low

Receive Descriptor Base Address High

Rdbal 02800hR/W

Rdbah 02804h R/W

Receive Descriptor Length

Receive Descriptor Head

Rdlen 02808h R/W

RDH 02810h R/W

Receive Delay Timer Register

Receive Descriptor Tail

RDT 02818hR/W

Rdtr 02820h R/W

Receive Interrupt Absolute Delay Timer1

Radv 0282Ch RW

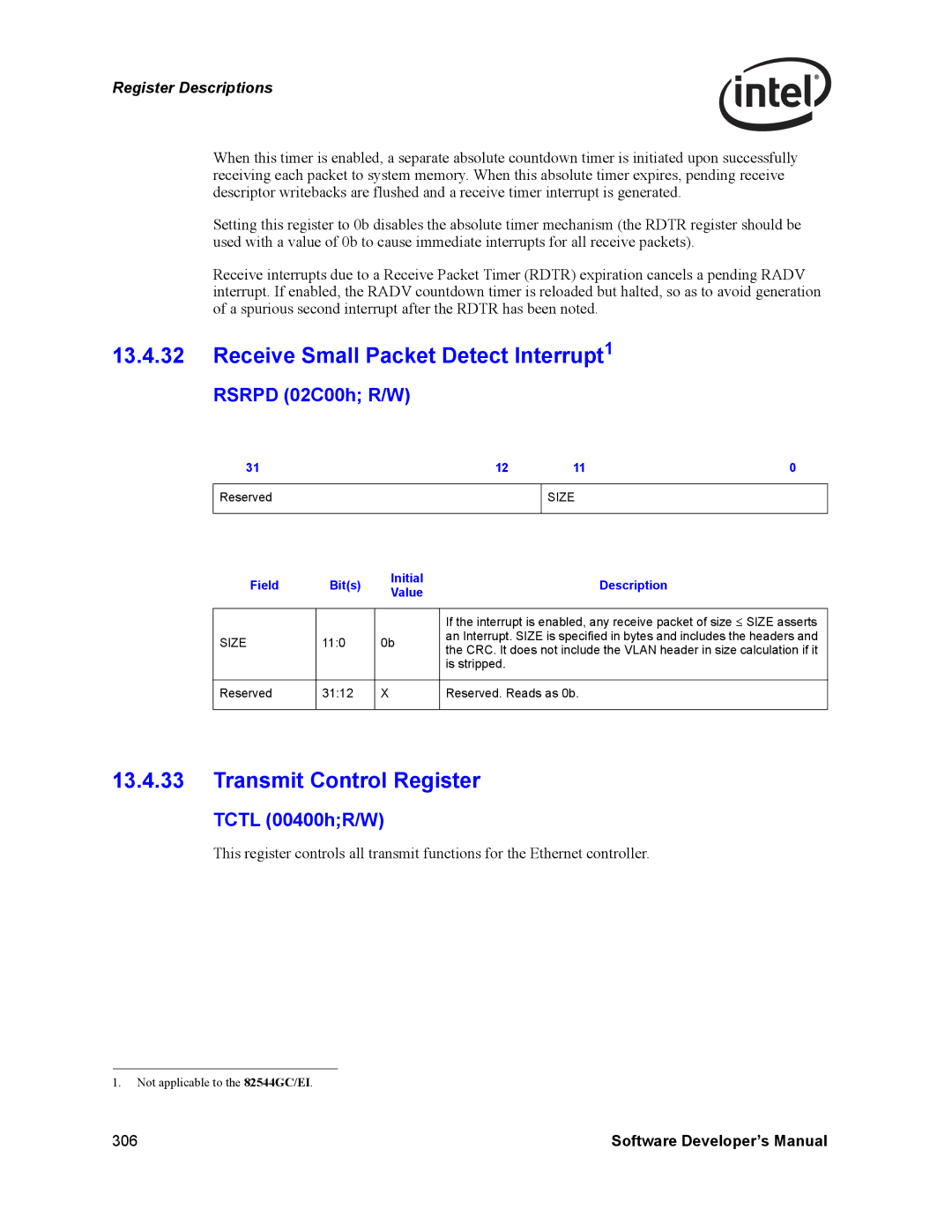

Receive Small Packet Detect Interrupt1

Transmit Control Register

Rsrpd 02C00h R/W

Tctl 00400hR/W

76. Tctl Register Bit Description

Cold

PSP

TCTL.COLD

Transmit IPG Register

Tipg 00410R/W

Rtlc

Nrtu

77. Tipg Register Bit Description

IPGR2 IPGR1 Ipgt

IPGR2

Adaptive IFS Throttle AIT

Aifs 00458R/W

Transmit Descriptor Base Address Low

Tdbal 03800h R/W

78. Aifs Register Bit Description

79. Tdbal Register Bit Description

Transmit Descriptor Base Address High

Transmit Descriptor Length

Tdbah 03804h R/W

Tdlen 03808h R/W

82. TDH Register Bit Description

Transmit Descriptor Head

TDH 03810h R/W

Transmit Interrupt Delay Value

Transmit Descriptor Tail

TDT 03818h R/W

Tidv 03820h R/W

TX DMA Control 82544GC/EI only

Transmit Descriptor Control

Txdmac 03000h R/W

Txdctl 03828h R/W

86. Txdctl Register Bit Description

Lwthresh RSV1 Gran RSV Wthresh Hthresh Pthresh

Transmit Absolute Interrupt Delay Value1

Tadv 0382Ch RW

Gran

Lwthresh

Tspbp

TCP Segmentation Pad And Minimum Threshold Tspmt 03830h RW

Tspbp Tsmt

Software Developer’s Manual 319

Receive Descriptor Control

Rxdctl 02828h R/W

87. Rxdctl Register Bit Description

Wthresh RSV Hthresh Pthresh

Receive Checksum Control

Rxcsum 05000h R/W

88. Rxcsum Register Bit Description

3111

IPV6OFL

Ipofld

Tuofld

Filter Registers

Multicast Table Array

MTA1270 05200h-053FCh R/W

89. MTA Register Bit Description

Destination Address

Receive Address Low

Receive Address High

RAL 05400h + 8*n R/W

RAH 05404h + 8∗n R/W

Vlan Filter Table Array1

VFTA1270 05600h 057FCh R/W

91. RAH Register Bit Description

RAH

Wakeup Registers

Wakeup Control Register

WUC 05800h R/W

92. VFTA1270 Bit Description

Wakeup Filter Control Register

Wufc 05808h R/W

Apmpme

SPM

Wakeup Status Register

WUS 05810h R

330

IP Address Valid

Ipav 5838h R/W

13.6.5 IPv4 Address

IP4AT 05840h 05858h R/W2

Address

Field Dword # Address Bits Initial Value Description

13.6.6 IPv6 Address

IP6AT 05880h 0588Ch R/W

IPV6ADDR0

Dword # Address Bits Initial Value Description

Flexible Filter Length Table

Wakeup Packet Length

Wakeup Packet Memory 128 Bytes

Flexible Filter Mask Table Ffmt 09000h 093F8h R/W

LEN0

LEN1

LEN2

Ffvt 09800h 09BF8h R/W

Statistics Registers

Flexible Filter Value Table

CRC Error Count

Alignment Error Count

Crcerrs 04000h R

Algnerrc 04004h R

Symbol Error Count

RX Error Count

Symerrs 04008h R

Rxerrc 0400Ch R

Missed Packets Count

Single Collision Count

MPC 04010h R

SCC 04014h R

Excessive Collisions Count

Multiple Collision Count

Ecol 04018h R

MCC 0401Ch R

Late Collisions Count

Collision Count

Latecol 04020h R

Colc 04028h R

Defer Count

Transmit with No CRS

DC 04030h R

Tncrs 04034h R

Sequence Error Count

Carrier Extension Error Count

SEC 04038h R

Cexterr 0403Ch R

Receive Length Error Count

XON Received Count

Rlec 04040h R

Xonrxc 04048h R

Xoff Transmitted Count

XON Transmitted Count

Xoff Received Count

FC Received Unsupported Count

Packets Received 64 Bytes Count

Fcruc 04058h R

PRC64 0405Ch R

Packets Received 65-127 Bytes Count

Packets Received 128-255 Bytes Count

PRC127 04060h R

PRC255 04064h R

Packets Received 256-511 Bytes Count

Packets Received 512-1023 Bytes Count

PRC511 04068h R

PRC1023 0406Ch R

Packets Received 1024 to Max Bytes Count

Good Packets Received Count

PRC1522 04070h R

Gprc 04074h R

Broadcast Packets Received Count

Multicast Packets Received Count

Bprc 04078h R

Mprc 0407Ch R

Good Packets Transmitted Count

Good Octets Received Count

Gptc 04080h R

Gorcl 04088h R/GORCH 0408Ch R

Good Octets Transmitted Count

Receive No Buffers Count

Gotcl 04090h R/ Gotch 04094 R

Rnbc 040A0h R

Receive Undersize Count

Receive Fragment Count

RUC 040A4h R

RFC 040A8h R

Receive Oversize Count

Receive Jabber Count

ROC 040ACh R

RJC 040B0h R

129. RJC Register Bit Description

Management Packets Received Count1

Mgtprc 040B4h R

Total Octets Received

Management Packets Dropped Count1

Management Pkts Transmitted Count1

Total Octets Transmitted

Totl 040C8h R/W / Toth 040CCh R

130. Torl and Torh Register Bit Descriptions

131. Totl and Toth Register Bit Descriptions

Total Packets Received

Total Packets Transmitted

TPR 040D0h R

TPT 040D4h R

Packets Transmitted 64 Bytes Count

Packets Transmitted 65-127 Bytes Count

PTC64 040D8h R

PTC127 040DCh R

Packets Transmitted 128-255 Bytes Count

Packets Transmitted 256-511 Bytes Count

PTC255 040E0h R

PTC511 040E4h R

Packets Transmitted 512-1023 Bytes Count

Packets Transmitted 1024 Bytes or Greater Count

PTC1023 040E8h R

PTC1522 040ECh R

Multicast Packets Transmitted Count

Broadcast Packets Transmitted Count

Mptc 040F0h R

Bptc 040F4h R

TCP Segmentation Context Transmitted Count

TCP Segmentation Context Transmit Fail Count

Tsctc 040F8h R

Tsctfc 040FCh R

Diagnostics Registers

Receive Data Fifo Head Register

Receive Data Fifo Tail Register

Rdfh 02410h R/W

Receive Data Fifo Head Saved Register

Receive Data Fifo Tail Saved Register

Rdfhs 02420h R/W

Rdfts 02428h R/W

Receive Data Fifo Packet Count

Transmit Data Fifo Head Register

Rdfpc 02430h R/W

Tdfh 03410h R/W

Transmit Data Fifo Tail Register

Transmit Data Fifo Head Saved Register

Tdft 03418h R/W

Tdfhs 03420h R/W

Transmit Data Fifo Tail Saved Register

Transmit Data Fifo Packet Count

Tdfts 03428h R/W

Tdfpc 03430h R/W

Packet Buffer Memory

PBM 10000h 1FFFCh R/W

151. Tdfpc Register Bit Description

152. PBM Bit Description

370

Power Up State

General Configuration

General Initialization and Reset Operation

Receive Initialization

Transmit Initialization

Fiber Copper 82544GC/EI

Ipgt IPGR1 IPGR2

Signal Descriptions

Signal Ball Name and Function

Signal Interface

Carrier Sense

Receive Data

Receive Clock

GMII/MII Features not Supported

Signal Functions

Signal Function Pin Gmii 1000 Mbps Operations

MII 10/100 Mbps Differences

Direct PHY Indications to MAC

Avoiding Gmii Test Modes MAC Configuration

Signal Functions Not Supported

Link Setup

CTRL.FD

PHY Initialization 10/100/1000 Mb/s Copper Media

CTRL.RFCE

Reset Operation

Lanpwrgood

382

Software Developer’s Manual 383

Initialization of Statistics

Diagnostics

Fifo State

Fifo Data

Loopback

Testability

Internal Loopback

Extest Instruction

SAMPLE/PRELOAD Instruction

Idcode Instruction

Bypass Instruction

388

New Features

Appendix Changes From 82544EI/82544GC

Register Changes

Table A-1. Register Changes

Register Offset

EEC

82540EP/EM Differences

Serial Flash Interface

4 32-Bit PCI Support

No TBI/Internal SerDes Interface

Single-Port Functionality