www.ti.com

Video Display Field and Frame Operation

4.7Video Display Field and Frame Operation

As a video source, the video port always outputs entire frames of data and transmits continuous video control signals. Depending on the EDMA structure, however, the video port may need to interrupt the DSP on a field or frame basis to allow it to update video port registers or EDMA parameters. To achieve this, the video port provides programmable control over the display process.

4.7.1 Display Determination and Notification

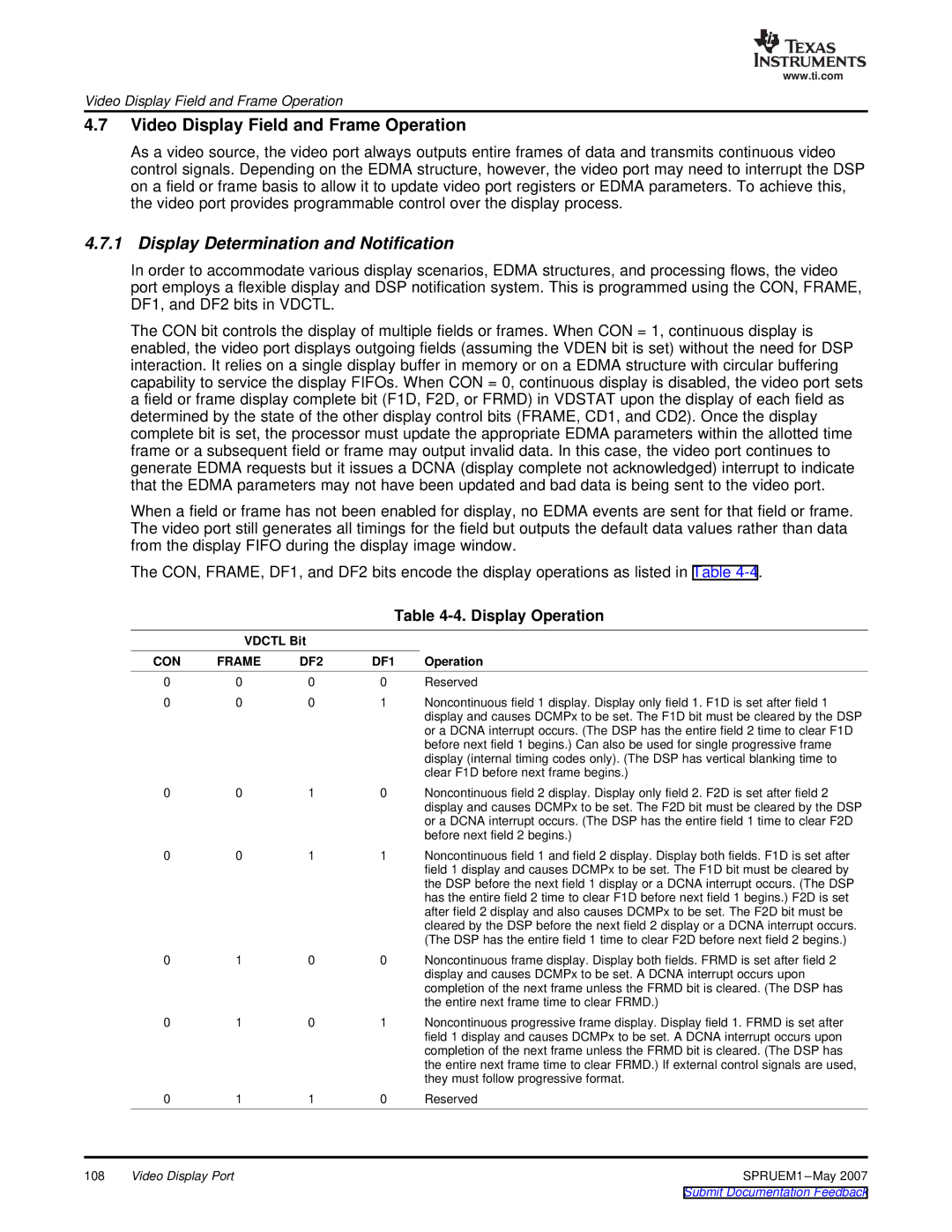

In order to accommodate various display scenarios, EDMA structures, and processing flows, the video port employs a flexible display and DSP notification system. This is programmed using the CON, FRAME, DF1, and DF2 bits in VDCTL.

The CON bit controls the display of multiple fields or frames. When CON = 1, continuous display is enabled, the video port displays outgoing fields (assuming the VDEN bit is set) without the need for DSP interaction. It relies on a single display buffer in memory or on a EDMA structure with circular buffering capability to service the display FIFOs. When CON = 0, continuous display is disabled, the video port sets a field or frame display complete bit (F1D, F2D, or FRMD) in VDSTAT upon the display of each field as determined by the state of the other display control bits (FRAME, CD1, and CD2). Once the display complete bit is set, the processor must update the appropriate EDMA parameters within the allotted time frame or a subsequent field or frame may output invalid data. In this case, the video port continues to generate EDMA requests but it issues a DCNA (display complete not acknowledged) interrupt to indicate that the EDMA parameters may not have been updated and bad data is being sent to the video port.

When a field or frame has not been enabled for display, no EDMA events are sent for that field or frame. The video port still generates all timings for the field but outputs the default data values rather than data from the display FIFO during the display image window.

The CON, FRAME, DF1, and DF2 bits encode the display operations as listed in Table

Table 4-4. Display Operation

| VDCTL Bit |

|

| |

CON | FRAME | DF2 | DF1 | Operation |

0 | 0 | 0 | 0 | Reserved |

0 | 0 | 0 | 1 | Noncontinuous field 1 display. Display only field 1. F1D is set after field 1 |

|

|

|

| display and causes DCMPx to be set. The F1D bit must be cleared by the DSP |

|

|

|

| or a DCNA interrupt occurs. (The DSP has the entire field 2 time to clear F1D |

|

|

|

| before next field 1 begins.) Can also be used for single progressive frame |

|

|

|

| display (internal timing codes only). (The DSP has vertical blanking time to |

|

|

|

| clear F1D before next frame begins.) |

0 | 0 | 1 | 0 | Noncontinuous field 2 display. Display only field 2. F2D is set after field 2 |

|

|

|

| display and causes DCMPx to be set. The F2D bit must be cleared by the DSP |

|

|

|

| or a DCNA interrupt occurs. (The DSP has the entire field 1 time to clear F2D |

|

|

|

| before next field 2 begins.) |

0 | 0 | 1 | 1 | Noncontinuous field 1 and field 2 display. Display both fields. F1D is set after |

|

|

|

| field 1 display and causes DCMPx to be set. The F1D bit must be cleared by |

|

|

|

| the DSP before the next field 1 display or a DCNA interrupt occurs. (The DSP |

|

|

|

| has the entire field 2 time to clear F1D before next field 1 begins.) F2D is set |

|

|

|

| after field 2 display and also causes DCMPx to be set. The F2D bit must be |

|

|

|

| cleared by the DSP before the next field 2 display or a DCNA interrupt occurs. |

|

|

|

| (The DSP has the entire field 1 time to clear F2D before next field 2 begins.) |

0 | 1 | 0 | 0 | Noncontinuous frame display. Display both fields. FRMD is set after field 2 |

|

|

|

| display and causes DCMPx to be set. A DCNA interrupt occurs upon |

|

|

|

| completion of the next frame unless the FRMD bit is cleared. (The DSP has |

|

|

|

| the entire next frame time to clear FRMD.) |

0 | 1 | 0 | 1 | Noncontinuous progressive frame display. Display field 1. FRMD is set after |

|

|

|

| field 1 display and causes DCMPx to be set. A DCNA interrupt occurs upon |

|

|

|

| completion of the next frame unless the FRMD bit is cleared. (The DSP has |

|

|

|

| the entire next frame time to clear FRMD.) If external control signals are used, |

|

|

|

| they must follow progressive format. |

0 | 1 | 1 | 0 | Reserved |

108 | Video Display Port | SPRUEM1 |