www.ti.com

Video Capture FIFO Registers

3.14 Video Capture FIFO Registers

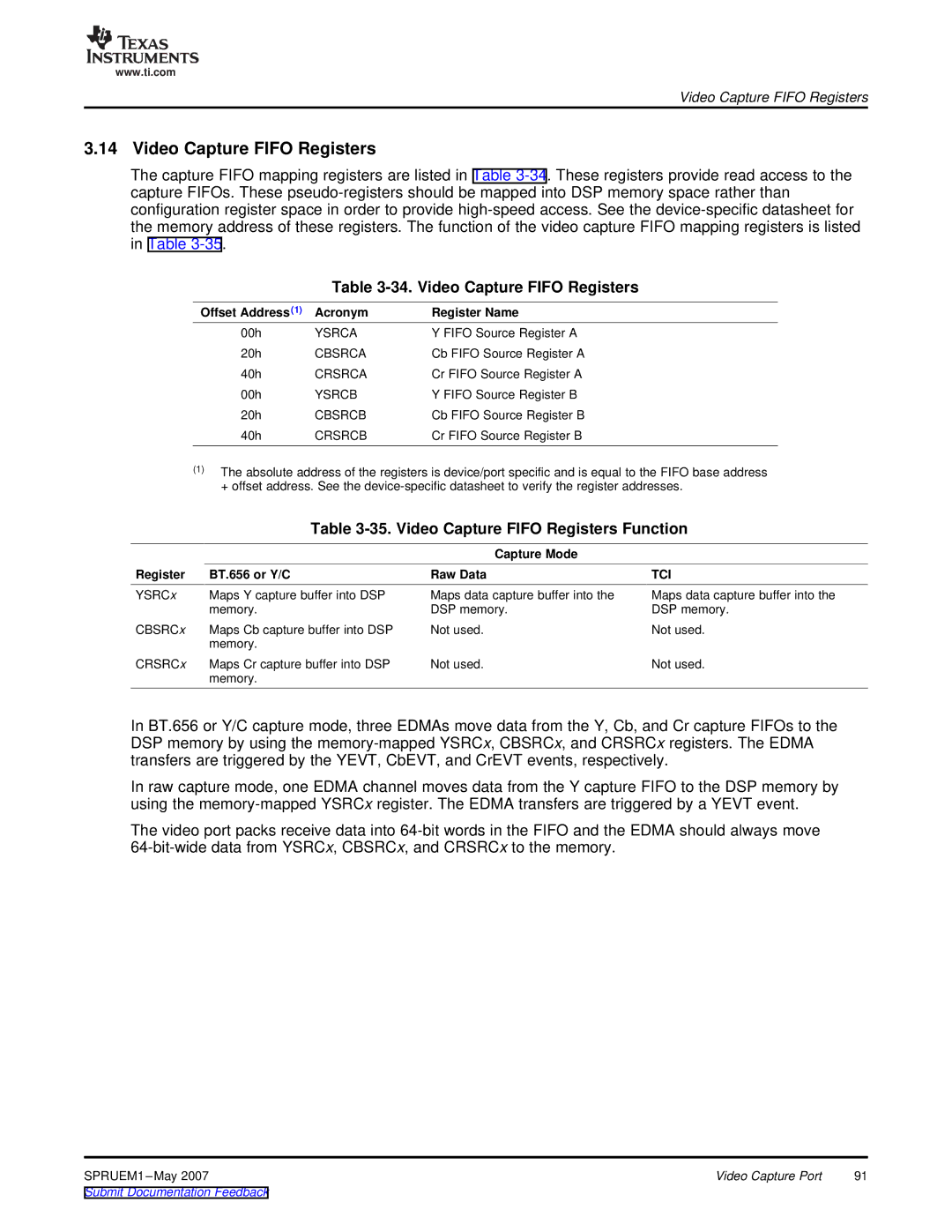

The capture FIFO mapping registers are listed in Table

Table 3-34. Video Capture FIFO Registers

Offset Address (1) | Acronym | Register Name |

00h | YSRCA | Y FIFO Source Register A |

20h | CBSRCA | Cb FIFO Source Register A |

40h | CRSRCA | Cr FIFO Source Register A |

00h | YSRCB | Y FIFO Source Register B |

20h | CBSRCB | Cb FIFO Source Register B |

40h | CRSRCB | Cr FIFO Source Register B |

(1)The absolute address of the registers is device/port specific and is equal to the FIFO base address + offset address. See the

Table 3-35. Video Capture FIFO Registers Function

Capture Mode

Register BT.656 or Y/C | Raw Data | TCI |

YSRCx Maps Y capture buffer into DSP memory.

CBSRCx Maps Cb capture buffer into DSP memory.

Maps data capture buffer into the DSP memory.

Not used.

Maps data capture buffer into the DSP memory.

Not used.

CRSRCx Maps Cr capture buffer into DSP | Not used. | Not used. |

memory. |

|

|

In BT.656 or Y/C capture mode, three EDMAs move data from the Y, Cb, and Cr capture FIFOs to the DSP memory by using the

In raw capture mode, one EDMA channel moves data from the Y capture FIFO to the DSP memory by using the

The video port packs receive data into

SPRUEM1 | Video Capture Port | 91 |