www.ti.com

Video Display Registers

Table

|

|

|

|

| Description |

Bit | field (1) | symval (1) | Value | BT.656 and Y/C Mode | Raw Data Mode |

Reserved | - | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field | ||

|

|

|

| has no effect. |

|

| OF(value) | |

|

| least VDTHRLD double words of space |

|

| in the Y display FIFO, a new Y EDMA |

|

| event may be generated. Whenever |

|

| there are at least ½ VDTHRLD double |

|

| words of space in the Cb or Cr display |

|

| FIFO, a new Cb or Cr EDMA event may |

|

| be generated. |

| DEFAULT | 0 |

Field 1 threshold. Whenever there are at least VDTHRLD double words of space in the display FIFO, a new Y EDMA event may be generated.

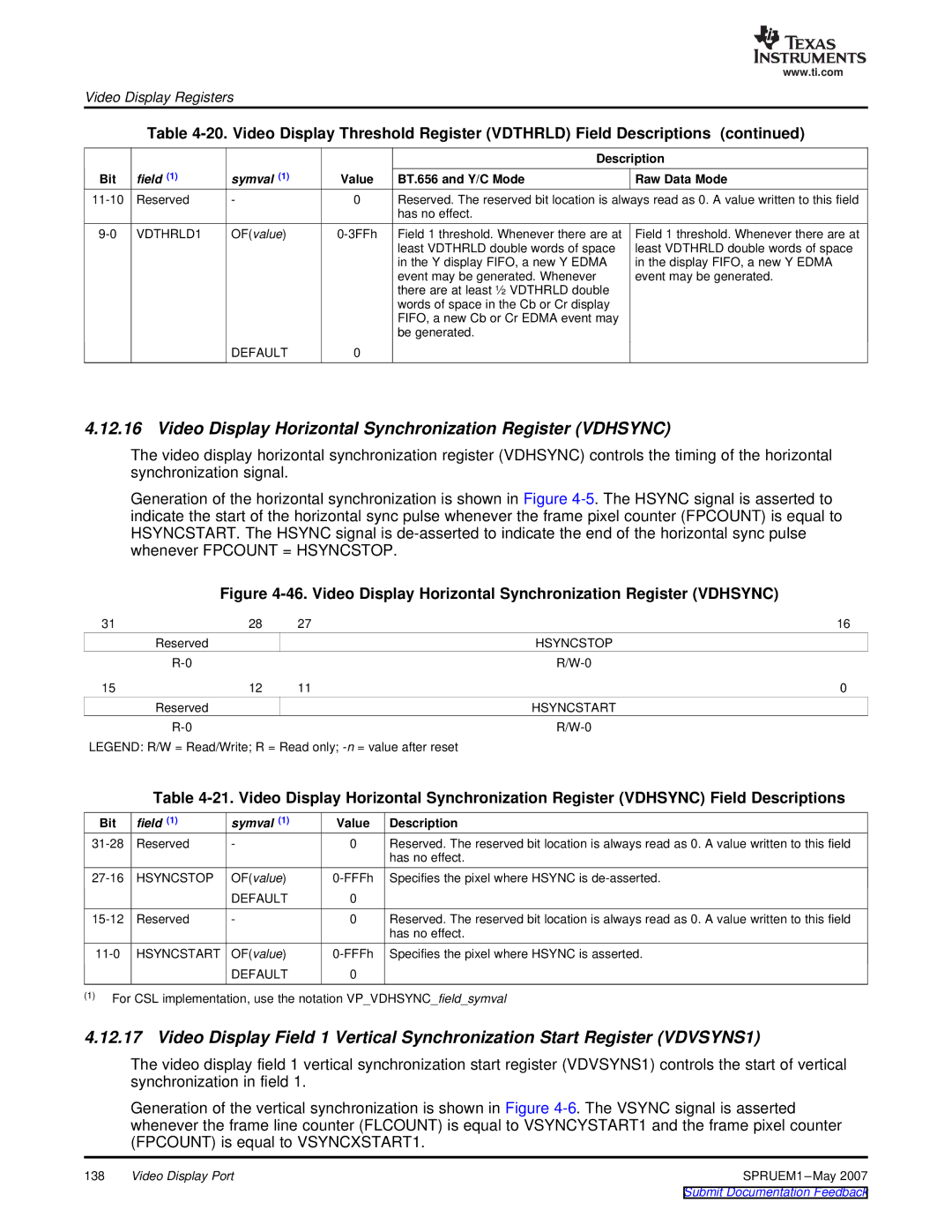

4.12.16 Video Display Horizontal Synchronization Register (VDHSYNC)

The video display horizontal synchronization register (VDHSYNC) controls the timing of the horizontal synchronization signal.

Generation of the horizontal synchronization is shown in Figure

Figure 4-46. Video Display Horizontal Synchronization Register (VDHSYNC)

31 | 28 | 27 | 16 |

| Reserved |

| HSYNCSTOP |

|

| ||

15 | 12 | 11 | 0 |

| Reserved |

| HSYNCSTART |

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table

Bit | field (1) | symval (1) | Value | Description |

Reserved | - | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field | |

|

|

|

| has no effect. |

HSYNCSTOP | OF(value) | Specifies the pixel where HSYNC is | ||

|

| DEFAULT | 0 |

|

Reserved | - | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field | |

|

|

|

| has no effect. |

HSYNCSTART | OF(value) | Specifies the pixel where HSYNC is asserted. | ||

|

| DEFAULT | 0 |

|

(1)For CSL implementation, use the notation VP_VDHSYNC_field_symval

4.12.17 Video Display Field 1 Vertical Synchronization Start Register (VDVSYNS1)

The video display field 1 vertical synchronization start register (VDVSYNS1) controls the start of vertical synchronization in field 1.

Generation of the vertical synchronization is shown in Figure

138 | Video Display Port | SPRUEM1 |