www.ti.com

Video Port FIFO

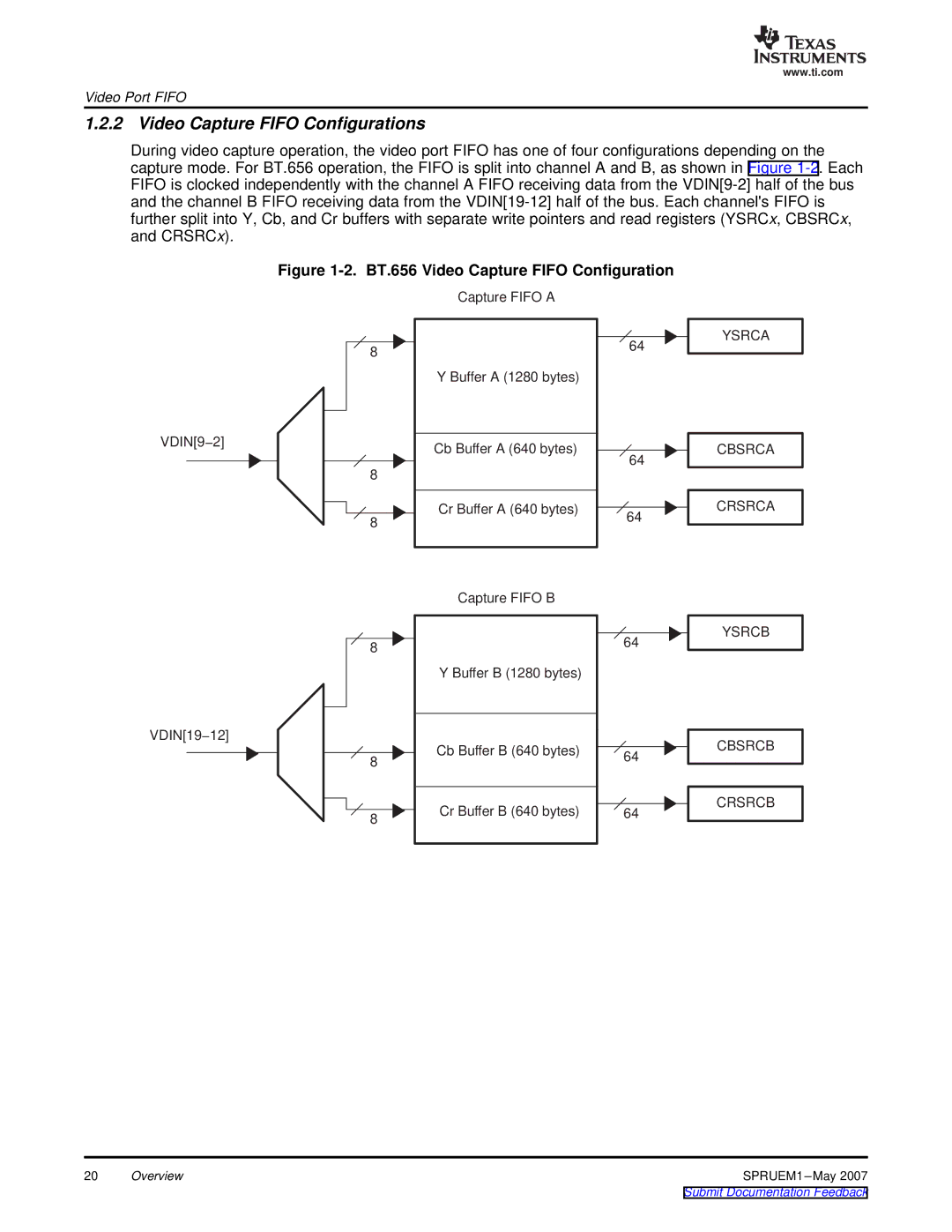

1.2.2 Video Capture FIFO Configurations

During video capture operation, the video port FIFO has one of four configurations depending on the capture mode. For BT.656 operation, the FIFO is split into channel A and B, as shown in Figure

Figure 1-2. BT.656 Video Capture FIFO Configuration

VDIN[9−2]

8 |

8 |

8 |

Capture FIFO A

Y Buffer A (1280 bytes)

Cb Buffer A (640 bytes)

Cr Buffer A (640 bytes)

64

64

64

YSRCA

CBSRCA

CRSRCA

VDIN[19−12]

8 |

8 |

8 |

Capture FIFO B

Y Buffer B (1280 bytes)

Cb Buffer B (640 bytes)

Cr Buffer B (640 bytes)

64

64

64

YSRCB

CBSRCB

CRSRCB

20 | Overview | SPRUEM1 |