www.ti.com

BT.656 and Y/C Mode Field and Frame Operation

For the Y/C video capture mode, the FIFO buffer is divided into three sections (three buffers). One section is 2560 bytes deep and is dedicated for storage of Y data samples. The other two sections are dedicated for storage of Cb and Cr data samples, respectively. The buffers for Cb and Cr samples are each 1280 bytes deep. The incoming video data stream is separated into Y, Cb, and Cr data streams, scaled (if selected) and the Y, Cb, and Cr buffers are filled. Each of the three buffers has a

If video capture is enabled, pixels in the capture window are captured in the Y, Cb, and Cr buffers. The video capture module uses the YEVT, CbEVT, and CrEVT events to notify the EDMA controller to copy data from the capture buffers to the DSP memory. The number of pixels required to generate the events is set by the VCTHRLDn bits in VCxCTL (the VCTHRLDn value must be an even number for Y/C mode). The capture module generates the events after VCTHRLD new pixels have been received. On every YEVT, the EDMA should move data from the Y buffer to DSP memory using the YSRC register as the source address. On every CbEVT, the EDMA should move data from the Cb buffer to DSP memory using the CBSRC register as the source address. On every CrEVT, the EDMA should move data from the Cr buffer to DSP memory using the CRSRC register as the source address. Note that transfer size from the Cb and Cr buffers is half of the transfer size from the Y buffer since for every four Y samples, there are two Cb and two Cr samples.

The three EDMA events are generated simultaneously when VCTHRLD is reached. Each event is reenabled when the first read of the respective FIFO by the requested EDMA begins.

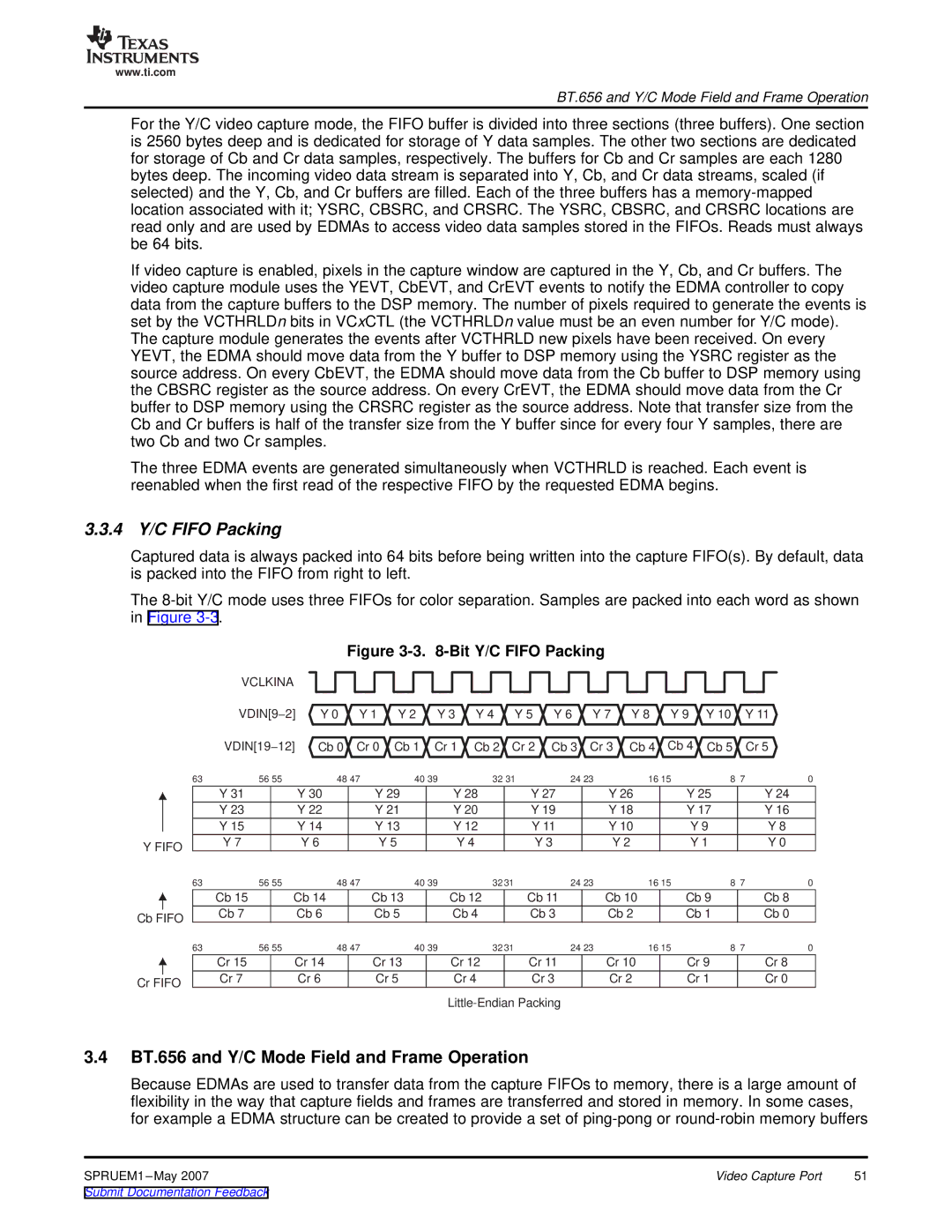

3.3.4 Y/C FIFO Packing

Captured data is always packed into 64 bits before being written into the capture FIFO(s). By default, data is packed into the FIFO from right to left.

The

|

|

|

|

|

|

|

|

|

| Figure |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

| VCLKINA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

| VDIN[9−2] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

| Y 0 |

|

|

| Y 1 |

| Y 2 |

|

| Y 3 |

| Y 4 |

| Y 5 |

|

| Y 6 |

|

| Y 7 | Y 8 |

|

| Y 9 |

| Y 10 | Y 11 | ||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| VDIN[19−12] |

|

|

| Cb 0 |

|

|

| Cr 0 |

| Cb 1 |

|

| Cr 1 |

| Cb 2 |

| Cr 2 |

|

| Cb 3 |

|

| Cr 3 | Cb 4 |

|

| Cb 4 |

|

| Cb 5 | Cr 5 | ||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

63 | 56 55 | 48 47 |

|

|

| 40 39 |

|

|

| 32 31 |

|

| 24 23 |

|

|

| 16 15 |

|

| 8 7 | 0 | |||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

| Y 31 |

| Y 30 |

|

|

|

|

| Y 29 |

|

|

|

| Y 28 |

|

|

|

| Y 27 |

|

|

| Y 26 |

|

|

| Y 25 |

|

|

| Y 24 | |||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||||||||||||||||||||||||

|

|

| Y 23 |

| Y 22 |

|

|

|

|

| Y 21 |

|

|

|

| Y 20 |

|

|

|

| Y 19 |

|

|

| Y 18 |

|

|

| Y 17 |

|

|

| Y 16 | |||||||||||||||||||||||||||||||

|

|

| Y 15 |

| Y 14 |

|

|

|

|

| Y 13 |

|

|

|

| Y 12 |

|

|

|

| Y 11 |

|

|

| Y 10 |

|

|

| Y 9 |

|

|

| Y 8 | |||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||||||

Y FIFO |

| Y 7 |

| Y 6 |

|

|

|

|

| Y 5 |

|

|

|

| Y 4 |

|

|

|

| Y 3 |

|

|

| Y 2 |

|

|

| Y 1 |

|

|

| Y 0 | ||||||||||||||||||||||||||||||||

63 | 56 55 | 48 47 |

|

|

| 40 39 |

|

|

| 32 31 |

|

| 24 23 |

|

|

| 16 15 |

|

| 8 7 | 0 | |||||||||||||||||||||||||||||||||||||||||||

|

|

| Cb 15 |

| Cb 14 |

|

|

|

| Cb 13 |

|

|

| Cb 12 |

|

|

| Cb 11 |

|

|

| Cb 10 |

|

|

| Cb 9 |

|

|

| Cb 8 | ||||||||||||||||||||||||||||||||||

Cb FIFO |

| Cb 7 |

| Cb 6 |

|

|

|

|

| Cb 5 |

|

|

|

| Cb 4 |

|

|

|

| Cb 3 |

|

|

| Cb 2 |

|

|

| Cb 1 |

|

|

| Cb 0 | ||||||||||||||||||||||||||||||||

63 | 56 55 | 48 47 |

|

|

| 40 39 |

|

|

| 32 31 |

|

| 24 23 |

|

|

| 16 15 |

|

| 8 7 | 0 | |||||||||||||||||||||||||||||||||||||||||||

|

|

| Cr 15 |

| Cr 14 |

|

|

|

| Cr 13 |

|

|

| Cr 12 |

|

|

| Cr 11 |

|

|

| Cr 10 |

|

|

| Cr 9 |

|

|

| Cr 8 | ||||||||||||||||||||||||||||||||||

Cr FIFO |

| Cr 7 |

| Cr 6 |

|

|

|

|

| Cr 5 |

|

|

|

| Cr 4 |

|

|

|

| Cr 3 |

|

|

| Cr 2 |

|

|

| Cr 1 |

|

|

| Cr 0 | ||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||

3.4BT.656 and Y/C Mode Field and Frame Operation

Because EDMAs are used to transfer data from the capture FIFOs to memory, there is a large amount of flexibility in the way that capture fields and frames are transferred and stored in memory. In some cases, for example a EDMA structure can be created to provide a set of

SPRUEM1 | Video Capture Port | 51 |