www.ti.com

|

|

|

|

|

|

| Video Capture Registers |

|

| Figure | |||||

31 |

| 28 | 27 |

|

|

| 16 |

| Reserved |

|

|

|

| VCYSTOP |

|

|

|

|

|

|

| ||

15 |

| 12 | 11 |

|

|

| 0 |

| Reserved |

|

|

|

| VCXSTOP |

|

|

|

|

|

|

| ||

LEGEND: R/W = Read/Write; R = Read only; |

|

| |||||

| Table | ||||||

|

|

|

|

|

| Description |

|

Bit | field (1) | symval (1) |

| Value | BT.656 or Y/C Mode | Raw Data Mode | TCI Mode |

Reserved | - |

| 0 | Reserved. The reserved bit location is always read as 0. A value written to this | |||

|

|

|

|

| field has no effect. |

|

|

| OF(value) | Last captured line. | Upper 12 bits of the | |

|

|

|

| data size (in data |

|

|

|

| samples). |

Upper 12 bits of the data size (in data samples).

| DEFAULT | 0 |

|

- | 0 | Reserved. The reserved bit location is always read as 0. A value written to this | |

|

|

| field has no effect. |

| OF(value) | Last captured pixel (VCXSTOP | |

|

|

| - 1). Must be an even value |

|

|

| (the LSB is treated as 0). |

| DEFAULT | 0 |

|

(1)For CSL implementation, use the notation VP_VCxSTOP1_field_symval

Lower 12 bits of the data size (in data samples).

Lower 12 bits of the data size (in data samples).

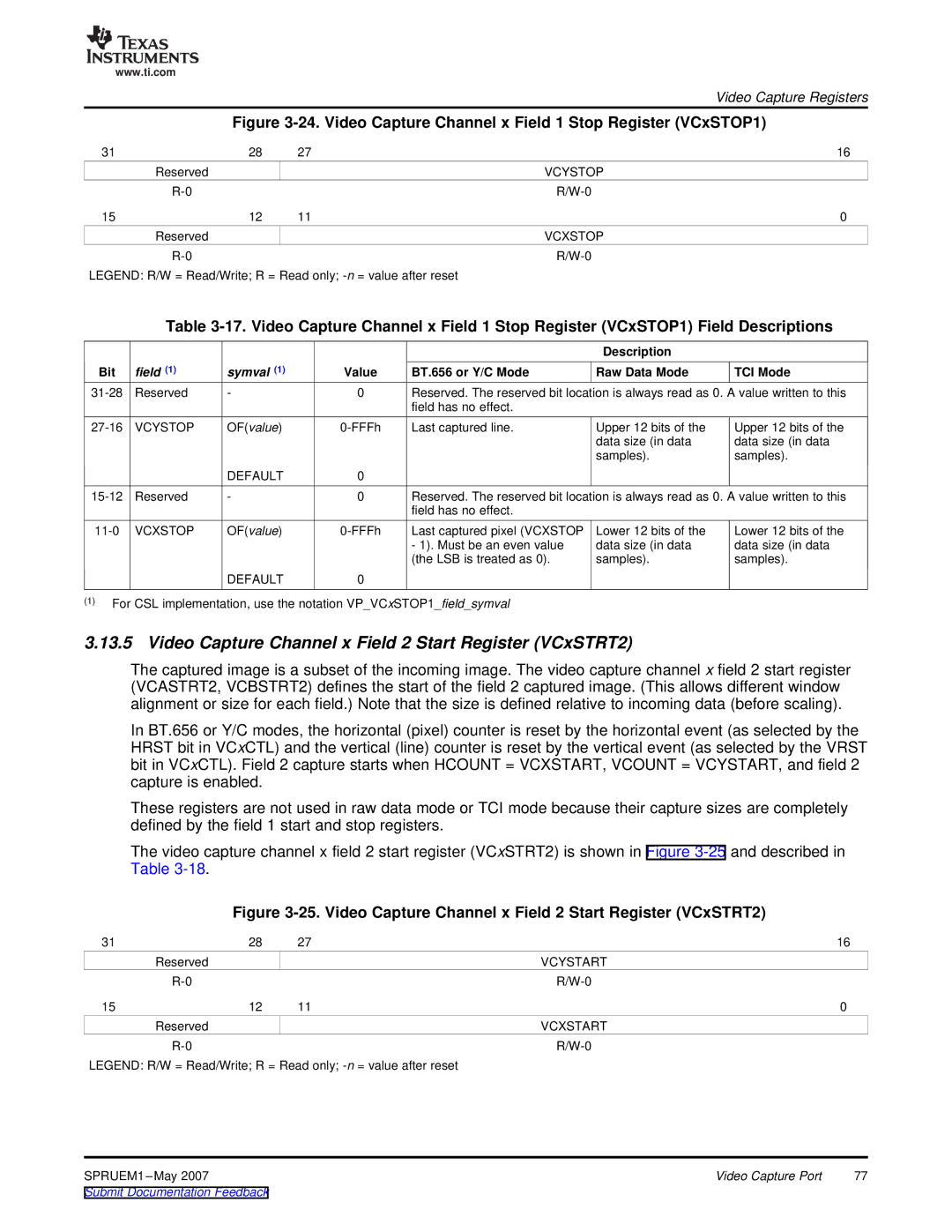

3.13.5 Video Capture Channel x Field 2 Start Register (VCxSTRT2)

The captured image is a subset of the incoming image. The video capture channel x field 2 start register (VCASTRT2, VCBSTRT2) defines the start of the field 2 captured image. (This allows different window alignment or size for each field.) Note that the size is defined relative to incoming data (before scaling).

In BT.656 or Y/C modes, the horizontal (pixel) counter is reset by the horizontal event (as selected by the HRST bit in VCxCTL) and the vertical (line) counter is reset by the vertical event (as selected by the VRST bit in VCxCTL). Field 2 capture starts when HCOUNT = VCXSTART, VCOUNT = VCYSTART, and field 2 capture is enabled.

These registers are not used in raw data mode or TCI mode because their capture sizes are completely defined by the field 1 start and stop registers.

The video capture channel x field 2 start register (VCxSTRT2) is shown in Figure

Figure 3-25. Video Capture Channel x Field 2 Start Register (VCxSTRT2)

31 | 28 | 27 | 16 |

| Reserved |

| VCYSTART |

|

| ||

15 | 12 | 11 | 0 |

| Reserved |

| VCXSTART |

|

|

LEGEND: R/W = Read/Write; R = Read only;

SPRUEM1 | Video Capture Port | 77 |

Submit Documentation Feedback |

|

|