www.ti.com

Video Capture Registers

3.13.8 Video Capture Channel x Threshold Register (VCATHRLD, VCBTHRLD)

The video capture channel x threshold register (VCATHRLD, VCBTHRLD) determines when EDMA requests are sent.

The VCTHRLD1 bits determine when capture EDMA events are generated. Once the threshold is reached, generation of further EDMA events is disabled until service of the previous event(s) begins (the first FIFO read by the EDMA occurs).

In BT.656 and Y/C modes, every two captured pixels represent 2 luma values in the Y FIFO and 2 chroma values (1 each in the Cb and Cr FIFOs). Depending on the data size each value may be a byte

In raw data mode, each data sample may occupy a byte

In TCI mode, VCTHRLD1 represents groups of 8 samples with each sample occupying a byte in the FIFO.

The VCTHRLD2 bits behave identically to VCTHRLD1, but are used during field 2 capture. It is only used if the field 2 EDMA size needs to be different from the field 1 EDMA size for some reason (for example, different captured line lengths in field 1 and field 2). If VT2EN is not set, then the VCTHRLD1 value is used for both fields.

Note that the VCTHRLDn applies to data being written into the FIFO. In the case of

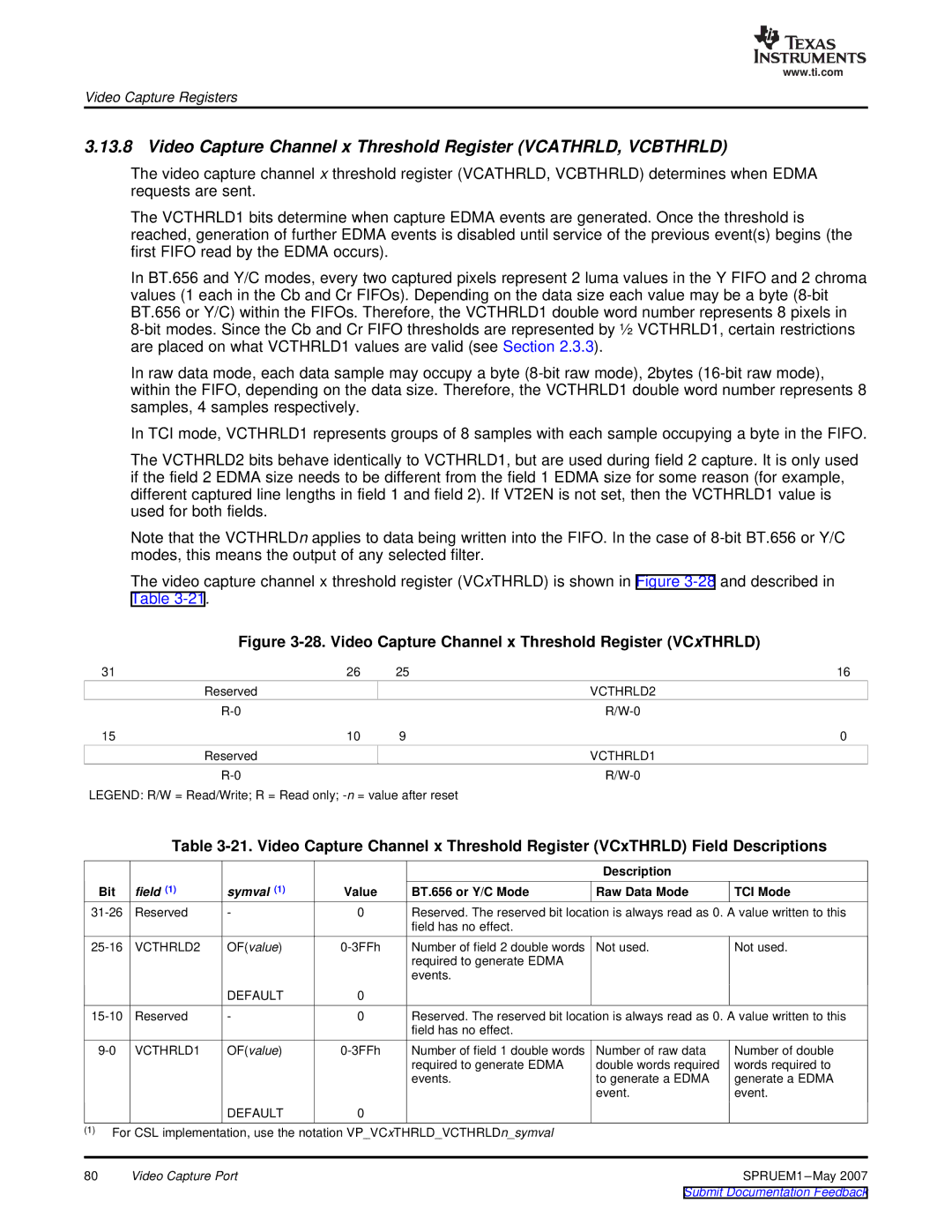

The video capture channel x threshold register (VCxTHRLD) is shown in Figure

Figure 3-28. Video Capture Channel x Threshold Register (VCxTHRLD)

31 | 26 | 25 | 16 |

| Reserved |

| VCTHRLD2 |

|

| ||

15 | 10 | 9 | 0 |

| Reserved |

| VCTHRLD1 |

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table

|

|

|

|

| Description |

|

Bit | field (1) | symval (1) | Value | BT.656 or Y/C Mode | Raw Data Mode | TCI Mode |

Reserved | - | 0 | Reserved. The reserved bit location is always read as 0. A value written to this | |||

|

|

|

| field has no effect. |

|

|

VCTHRLD2 | OF(value) | Number of field 2 double words | Not used. | Not used. | ||

|

|

|

| required to generate EDMA |

|

|

|

|

|

| events. |

|

|

|

| DEFAULT | 0 |

|

|

|

Reserved | - | 0 | Reserved. The reserved bit location is always read as 0. A value written to this | |||

|

|

|

| field has no effect. |

|

|

OF(value) | Number of field 1 double words | ||

|

|

| required to generate EDMA |

|

|

| events. |

Number of raw data | Number of double |

double words required | words required to |

to generate a EDMA | generate a EDMA |

event. | event. |

DEFAULT ![]() 0

0

(1)For CSL implementation, use the notation VP_VCxTHRLD_VCTHRLDn_symval

80 | Video Capture Port | SPRUEM1 |