www.ti.com

GPIO Registers

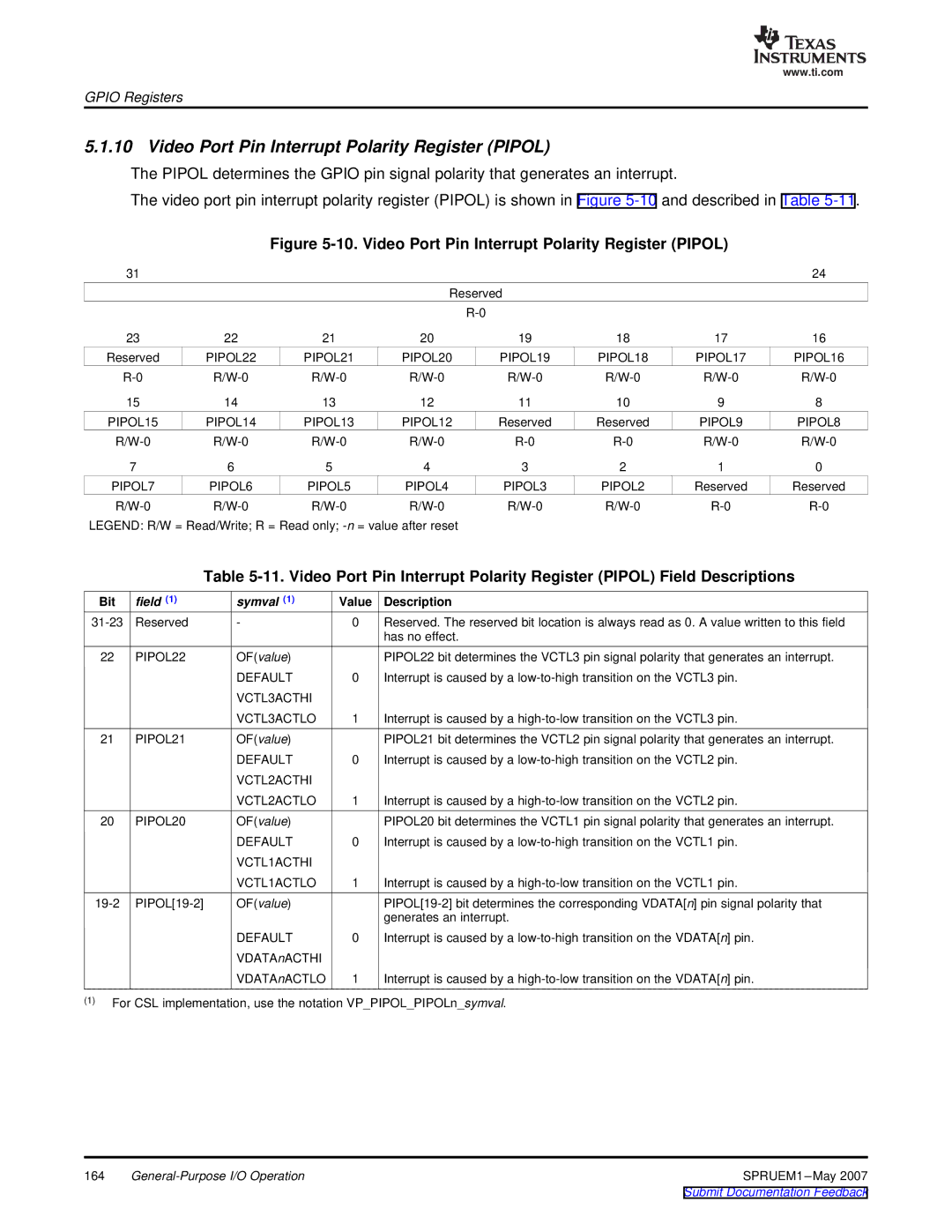

5.1.10 Video Port Pin Interrupt Polarity Register (PIPOL)

The PIPOL determines the GPIO pin signal polarity that generates an interrupt.

The video port pin interrupt polarity register (PIPOL) is shown in Figure

Figure 5-10. Video Port Pin Interrupt Polarity Register (PIPOL)

31 |

|

|

|

|

|

| 24 |

|

|

| Reserved |

|

|

| |

|

|

|

|

|

|

| |

23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

Reserved | PIPOL22 | PIPOL21 | PIPOL20 | PIPOL19 | PIPOL18 | PIPOL17 | PIPOL16 |

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

PIPOL15 | PIPOL14 | PIPOL13 | PIPOL12 | Reserved | Reserved | PIPOL9 | PIPOL8 |

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

PIPOL7 | PIPOL6 | PIPOL5 | PIPOL4 | PIPOL3 | PIPOL2 | Reserved | Reserved |

LEGEND: R/W = Read/Write; R = Read only;

Table

Bit | field (1) | symval (1) |

Reserved | - | |

22 | PIPOL22 | OF(value) |

|

| DEFAULT |

|

| VCTL3ACTHI |

|

| VCTL3ACTLO |

21 | PIPOL21 | OF(value) |

|

| DEFAULT |

|

| VCTL2ACTHI |

|

| VCTL2ACTLO |

20 | PIPOL20 | OF(value) |

|

| DEFAULT |

|

| VCTL1ACTHI |

|

| VCTL1ACTLO |

OF(value) |

DEFAULT

VDATAnACTHI

VDATAnACTLO ![]()

Value  Description

Description

0Reserved. The reserved bit location is always read as 0. A value written to this field has no effect.

![]() PIPOL22 bit determines the VCTL3 pin signal polarity that generates an interrupt.

PIPOL22 bit determines the VCTL3 pin signal polarity that generates an interrupt.

0Interrupt is caused by a

1![]() Interrupt is caused by a

Interrupt is caused by a

![]() PIPOL21 bit determines the VCTL2 pin signal polarity that generates an interrupt.

PIPOL21 bit determines the VCTL2 pin signal polarity that generates an interrupt.

0Interrupt is caused by a

1![]() Interrupt is caused by a

Interrupt is caused by a

PIPOL20 bit determines the VCTL1 pin signal polarity that generates an interrupt.

0Interrupt is caused by a

1![]() Interrupt is caused by a

Interrupt is caused by a

0Interrupt is caused by a

1![]() Interrupt is caused by a

Interrupt is caused by a

(1)For CSL implementation, use the notation VP_PIPOL_PIPOLn_symval.

164 | SPRUEM1 | |

|

| Submit Documentation Feedback |