www.ti.com

GPIO Registers

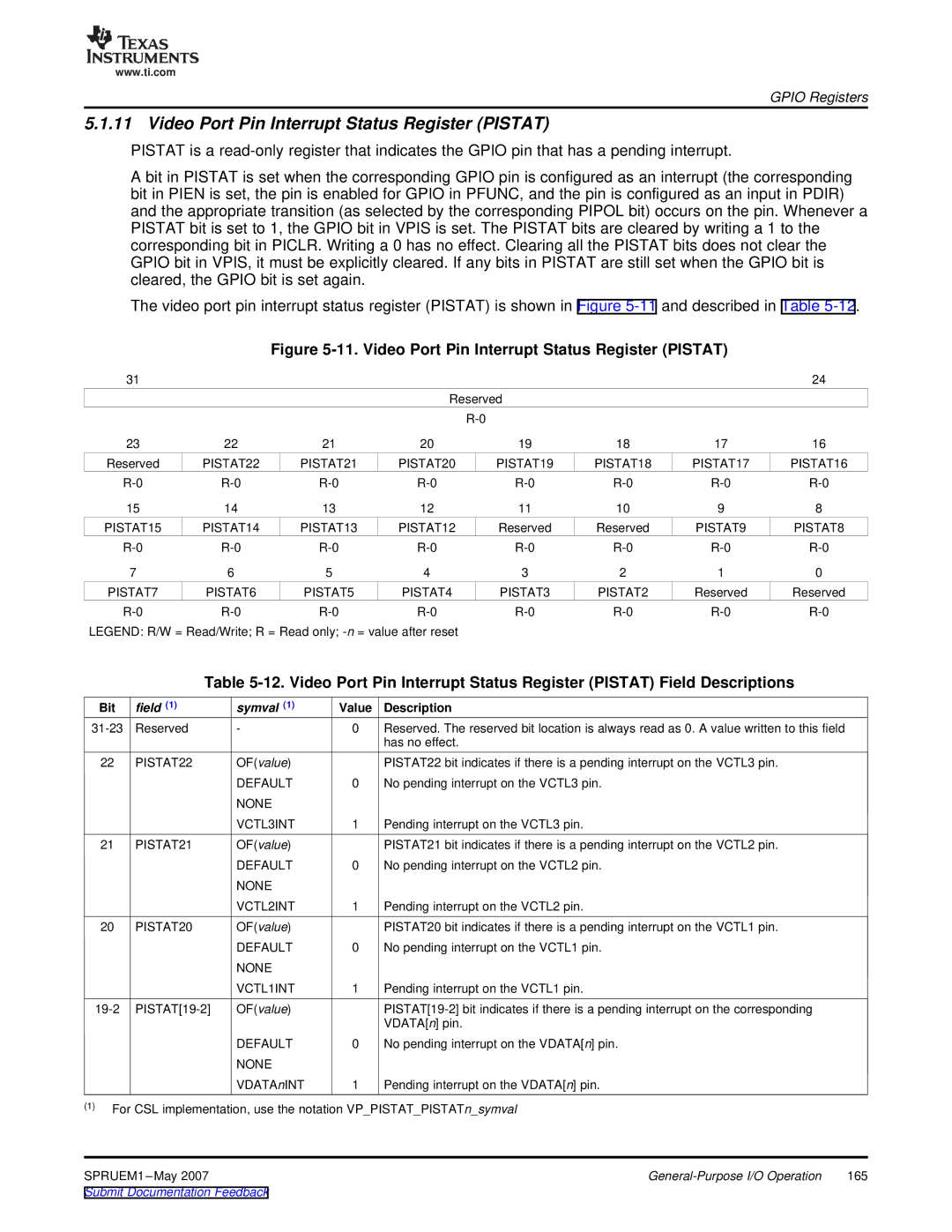

5.1.11 Video Port Pin Interrupt Status Register (PISTAT)

PISTAT is a

A bit in PISTAT is set when the corresponding GPIO pin is configured as an interrupt (the corresponding bit in PIEN is set, the pin is enabled for GPIO in PFUNC, and the pin is configured as an input in PDIR) and the appropriate transition (as selected by the corresponding PIPOL bit) occurs on the pin. Whenever a PISTAT bit is set to 1, the GPIO bit in VPIS is set. The PISTAT bits are cleared by writing a 1 to the corresponding bit in PICLR. Writing a 0 has no effect. Clearing all the PISTAT bits does not clear the GPIO bit in VPIS, it must be explicitly cleared. If any bits in PISTAT are still set when the GPIO bit is cleared, the GPIO bit is set again.

The video port pin interrupt status register (PISTAT) is shown in Figure

Figure 5-11. Video Port Pin Interrupt Status Register (PISTAT)

31 |

|

|

|

|

|

| 24 |

|

|

| Reserved |

|

|

| |

|

|

|

|

|

|

| |

23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

Reserved | PISTAT22 | PISTAT21 | PISTAT20 | PISTAT19 | PISTAT18 | PISTAT17 | PISTAT16 |

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

PISTAT15 | PISTAT14 | PISTAT13 | PISTAT12 | Reserved | Reserved | PISTAT9 | PISTAT8 |

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

PISTAT7 | PISTAT6 | PISTAT5 | PISTAT4 | PISTAT3 | PISTAT2 | Reserved | Reserved |

LEGEND: R/W = Read/Write; R = Read only;

Table

Bit | field (1) | symval (1) | Value | Description |

Reserved | - | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field | |

|

|

|

| has no effect. |

22 | PISTAT22 | OF(value) |

| PISTAT22 bit indicates if there is a pending interrupt on the VCTL3 pin. |

|

| DEFAULT | 0 | No pending interrupt on the VCTL3 pin. |

|

| NONE |

|

|

|

| VCTL3INT | 1 | Pending interrupt on the VCTL3 pin. |

21 | PISTAT21 | OF(value) |

| PISTAT21 bit indicates if there is a pending interrupt on the VCTL2 pin. |

|

| DEFAULT | 0 | No pending interrupt on the VCTL2 pin. |

|

| NONE |

|

|

|

| VCTL2INT | 1 | Pending interrupt on the VCTL2 pin. |

20 | PISTAT20 | OF(value) |

| PISTAT20 bit indicates if there is a pending interrupt on the VCTL1 pin. |

|

| DEFAULT | 0 | No pending interrupt on the VCTL1 pin. |

|

| NONE |

|

|

|

| VCTL1INT | 1 | Pending interrupt on the VCTL1 pin. |

OF(value) |

| |||

|

|

|

| VDATA[n] pin. |

|

| DEFAULT | 0 | No pending interrupt on the VDATA[n] pin. |

|

| NONE |

|

|

|

| VDATAnINT | 1 | Pending interrupt on the VDATA[n] pin. |

(1)For CSL implementation, use the notation VP_PISTAT_PISTATn_symval

SPRUEM1 | 165 | |

Submit Documentation Feedback |

|

|