www.ti.com

BT.656 Video Display Mode

4.1.3 Sync Signal Generation

The video display module must generate a number of control signals for both internal and external use. As seen in Section 4.1.2, the HSYNC, HBLNK, VSYNC, VBLNK, and FLD signals are generated directly from the pixel and line counters and comparison registers. Several additional signals are also generated indirectly for use in external control.

A composite blank (CBLNK) signal is generated as the

Up to three of the eight sync signals may be output on VCTL1, VCTL2, and VCTL3 as selected by the video display control register (VDCTL). Each signal may be output in its

4.1.4 External Sync Operation

The video display module may be synchronized with an external video source using external sync signals. VCTL1 may be configured as an external horizontal sync input. When the external HSYNC is asserted, FPCOUNT is loaded with the HRLD value and VCCOUNT is loaded with the CRLD value. VCTL2 may be configured as an external vertical sync input. When the external VSYNC is asserted during field 1, FLCOUNT is loaded with the VRLD value. Field determination is made using either VCTL3 as an external FLD input or by field detect logic using the VSYNC and HSYNC inputs.

4.1.5 Port Sync Operation

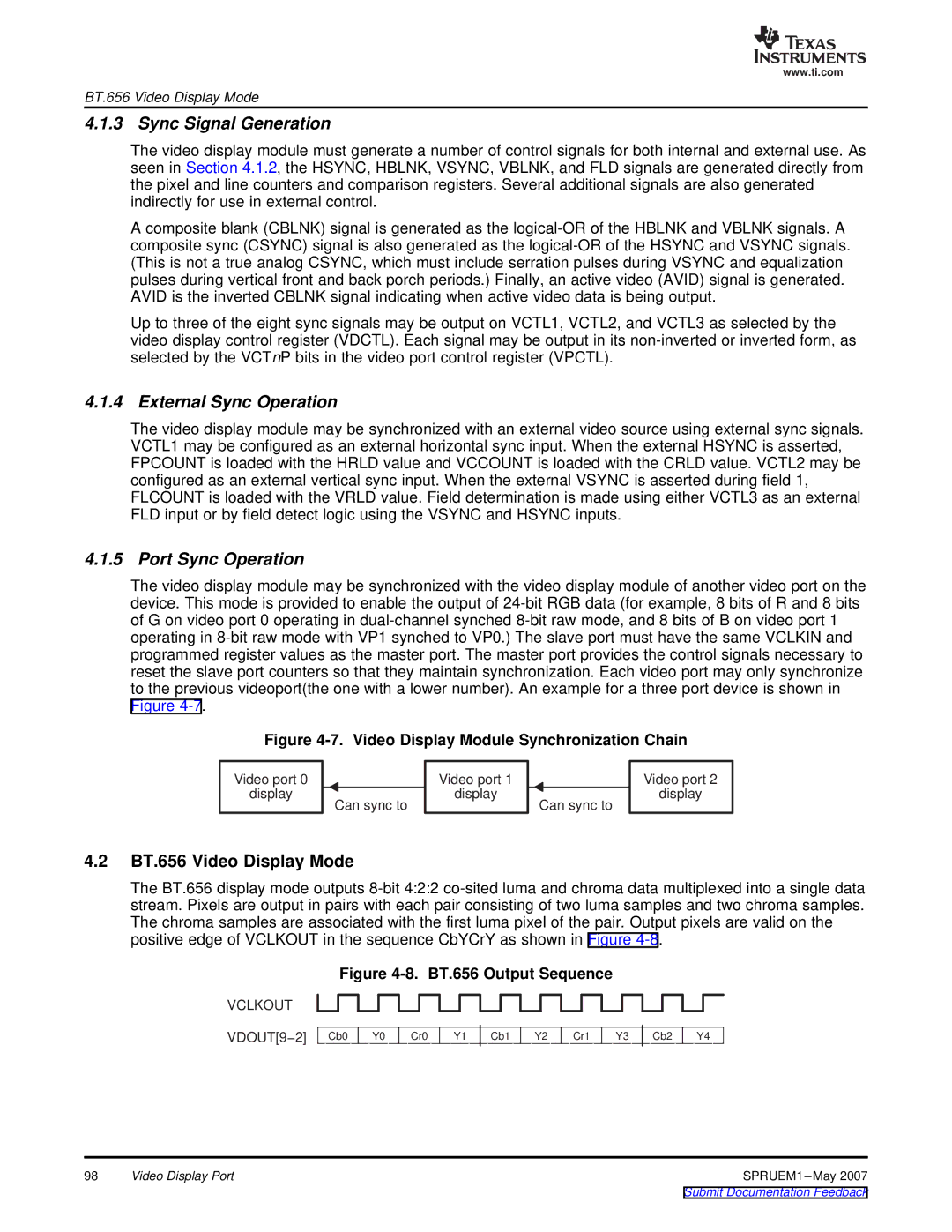

The video display module may be synchronized with the video display module of another video port on the device. This mode is provided to enable the output of

Figure 4-7. Video Display Module Synchronization Chain

Video port 0

display

Can sync to

Video port 1

display

Can sync to

Video port 2

display

4.2BT.656 Video Display Mode

The BT.656 display mode outputs

Figure 4-8. BT.656 Output Sequence

VCLKOUT

VDOUT[9−2]

Cb0

Y0

Cr0

Y1

Cb1

Y2

Cr1

Y3

Cb2

Y4

98 | Video Display Port | SPRUEM1 |