www.ti.com

Display Timing Examples

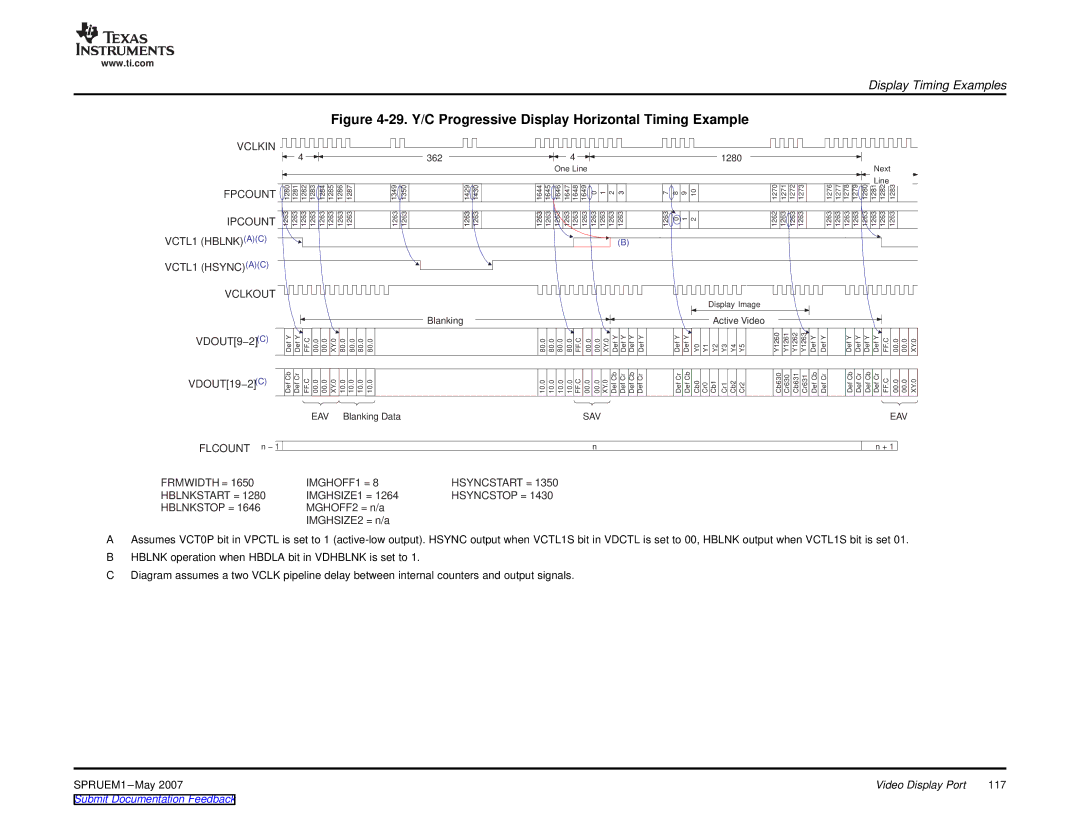

Figure 4-29. Y/C Progressive Display Horizontal Timing Example

VCLKIN ![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

|

|

| 4 |

|

|

|

|

|

FPCOUNT | 1280 | 1281 | 1282 | 1283 | 1284 | 1285 | 1286 | 1287 |

IPCOUNT | 1263 | 1263 | 1263 | 1263 | 1263 | 1263 | 1263 | 1263 |

VCTL1 (HBLNK)(A)(C)

VCTL1 (HSYNC)(A)(C)

VCLKOUT

|

| 362 |

|

|

|

|

| 4 |

|

|

|

|

|

|

|

|

| 1280 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| One Line |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Next | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1270 | 1271 | 1272 | 1273 | 1276 | 1277 | 1278 | 1279 | 1280 | Line |

| |

1349 | 1350 | 1429 | 1430 | 1644 | 1645 | 1646 | 1647 | 1648 | 1649 | 0 | 1 | 2 | 3 | 7 | 8 | 9 | 10 | 1281 | 1282 | 1283 | |||||||||

1263 | 1263 | 1263 | 1263 | 1263 | 1263 | 2631 | 2631 | 1263 | 1263 | 1263 | 1263 | 1263 | 1263 | 1263 | 0 | 1 | 2 | 1262 | 1263 | 1263 | 1263 | 1263 | 1263 | 1263 | 1263 | 1263 | 1263 | 1263 | 1263 |

Display Image

Blanking | Active Video |

VDOUT[9−2] (C)

Def Y

Def Y

FF.C | 00.0 | 00.0 | XY.0 | 80.0 | 80.0 | 80.0 | 80.0 | 80.0 | 80.0 | 80.0 | 80.0 | FF.C | 00.0 | 00.0 | XY.0 | Def Y | Def Y | Def Y | Def Y | Def Y | Def Y | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y1260 | Y1261 | Y1262 | Y1263 | Def Y | Def Y | Def Y | Def Y | Def Y | Def Y | FF.C | 00.0 | 00.0 | XY.0 |

VDOUT[19−2] (C)

FLCOUNT n − 1

Def Cb Def Cr | FF.C 00.0 00.0 XY.0 | 10.0 10.0 10.0 10.0 |

| EAV | Blanking Data |

10.0 10.0 10.0 10.0 FF.C 00.0 | 00.0 XY.0 Def Cb Def Cr Def Cb Def Cr | Def Cr Def Cb Cb0 Cr0 Cb1 | Cr1 Cb2 Cr2 | Cb630 Cr630 Cb631 Cr631 Def Cb Def Cr | Def Cb Def Cr Def Cb Def Cr FF.C | 00.0 00.0 XY.0 |

SAV |

|

|

|

| EAV | |

| n |

|

|

| n + 1 | |

FRMWIDTH = 1650 | IMGHOFF1 = 8 |

HBLNKSTART = 1280 | IMGHSIZE1 = 1264 |

HBLNKSTOP = 1646 | MGHOFF2 = n/a |

| IMGHSIZE2 = n/a |

HSYNCSTART = 1350 HSYNCSTOP = 1430

AAssumes VCT0P bit in VPCTL is set to 1

BHBLNK operation when HBDLA bit in VDHBLNK is set to 1.

CDiagram assumes a two VCLK pipeline delay between internal counters and output signals.

SPRUEM1 | Video Display Port | 117 |

Submit Documentation Feedback |

|

|