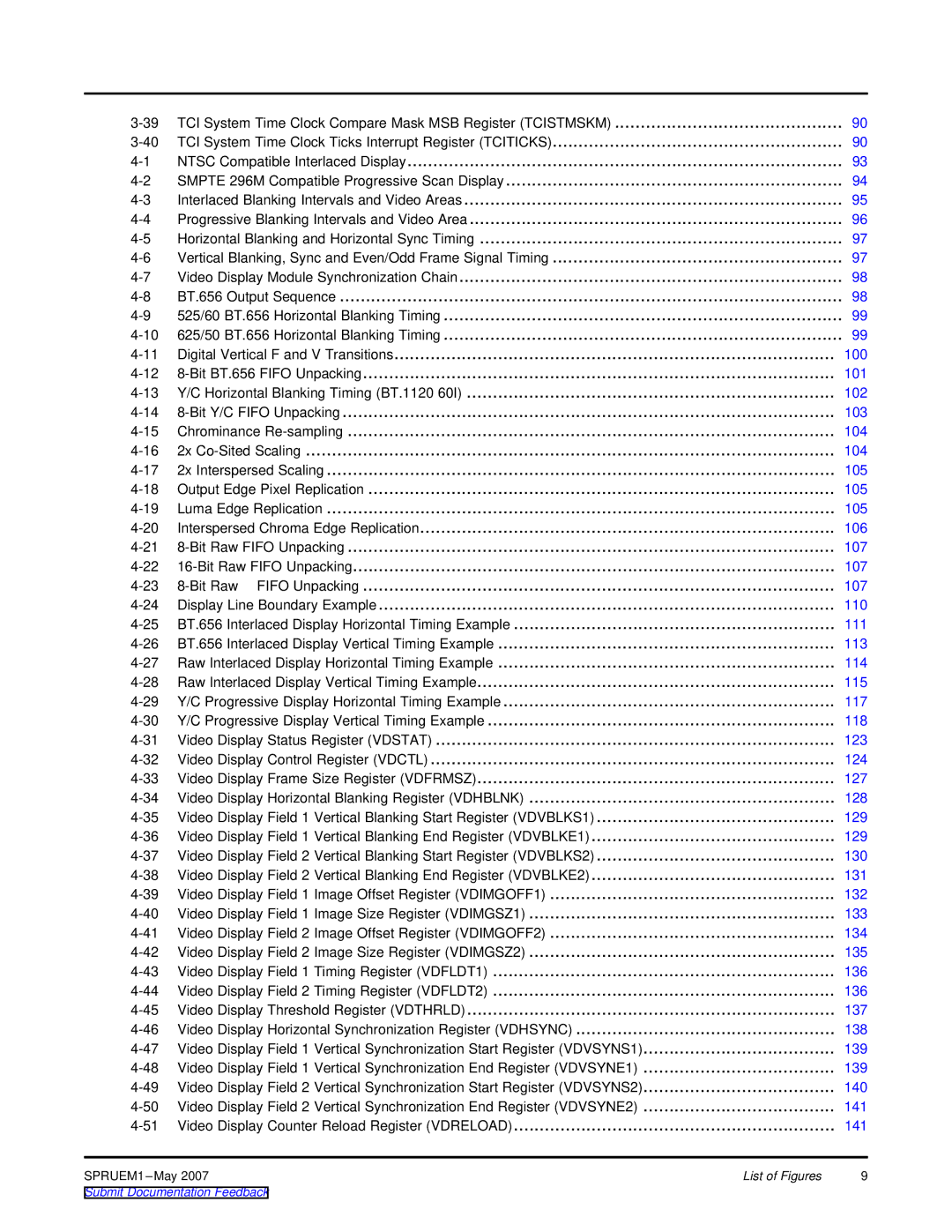

TCI System Time Clock Compare Mask MSB Register (TCISTMSKM) | 90 | ||

TCI System Time Clock Ticks Interrupt Register (TCITICKS) | 90 | ||

NTSC Compatible Interlaced Display | 93 | ||

SMPTE 296M Compatible Progressive Scan Display | 94 | ||

Interlaced Blanking Intervals and Video Areas | 95 | ||

Progressive Blanking Intervals and Video Area | 96 | ||

Horizontal Blanking and Horizontal Sync Timing | 97 | ||

Vertical Blanking, Sync and Even/Odd Frame Signal Timing | 97 | ||

Video Display Module Synchronization Chain | 98 | ||

BT.656 Output Sequence | 98 | ||

525/60 BT.656 Horizontal Blanking Timing | 99 | ||

625/50 BT.656 Horizontal Blanking Timing | 99 | ||

Digital Vertical F and V Transitions | 100 | ||

| 101 | ||

Y/C Horizontal Blanking Timing (BT.1120 60I) | 102 | ||

103 | |||

Chrominance | 104 | ||

2x | 104 | ||

2x Interspersed Scaling | 105 | ||

Output Edge Pixel Replication | 105 | ||

Luma Edge Replication | 105 | ||

Interspersed Chroma Edge Replication | 106 | ||

107 | |||

107 | |||

107 | |||

Display Line Boundary Example | 110 | ||

BT.656 Interlaced Display Horizontal Timing Example | 111 | ||

BT.656 Interlaced Display Vertical Timing Example | 113 | ||

Raw Interlaced Display Horizontal Timing Example | 114 | ||

Raw Interlaced Display Vertical Timing Example | 115 | ||

Y/C Progressive Display Horizontal Timing Example | 117 | ||

Y/C Progressive Display Vertical Timing Example | 118 | ||

Video Display Status Register (VDSTAT) | 123 | ||

Video Display Control Register (VDCTL) | 124 | ||

Video Display Frame Size Register (VDFRMSZ) | 127 | ||

Video Display Horizontal Blanking Register (VDHBLNK) | 128 | ||

Video Display Field 1 Vertical Blanking Start Register (VDVBLKS1) | 129 | ||

Video Display Field 1 Vertical Blanking End Register (VDVBLKE1) | 129 | ||

Video Display Field 2 Vertical Blanking Start Register (VDVBLKS2) | 130 | ||

Video Display Field 2 Vertical Blanking End Register (VDVBLKE2) | 131 | ||

Video Display Field 1 Image Offset Register (VDIMGOFF1) | 132 | ||

Video Display Field 1 Image Size Register (VDIMGSZ1) | 133 | ||

Video Display Field 2 Image Offset Register (VDIMGOFF2) | 134 | ||

Video Display Field 2 Image Size Register (VDIMGSZ2) | 135 | ||

Video Display Field 1 Timing Register (VDFLDT1) | 136 | ||

Video Display Field 2 Timing Register (VDFLDT2) | 136 | ||

Video Display Threshold Register (VDTHRLD) | 137 | ||

Video Display Horizontal Synchronization Register (VDHSYNC) | 138 | ||

Video Display Field 1 Vertical Synchronization Start Register (VDVSYNS1) | 139 | ||

Video Display Field 1 Vertical Synchronization End Register (VDVSYNE1) | 139 | ||

Video Display Field 2 Vertical Synchronization Start Register (VDVSYNS2) | 140 | ||

Video Display Field 2 Vertical Synchronization End Register (VDVSYNE2) | 141 | ||

Video Display Counter Reload Register (VDRELOAD) | 141 | ||

SPRUEM1 | List of Figures | 9 | |