www.ti.com

|

|

|

|

| Video Capture Registers |

| Table | ||||

|

|

|

| Description | |

Bit | field (1) | symval (1) | Value | BT.656, Y/C Mode, or Raw Data Mode | TCI Mode |

3 | STEN | OF(value) |

| System time clock interrupt enable bit. |

|

|

| DEFAULT | 0 | Not used. | Setting of the STC bit is disabled. |

|

| DISABLE |

|

|

|

|

| SET |

| Not used. | A valid STC compare sets the STC bit in |

|

|

|

|

| VPIS. |

2 | CTMODE | OF(value) |

| Counter mode select bit. |

|

|

| DEFAULT | 0 | Not used. | The |

|

| 90KHZ |

|

| counter increments at 90 kHz (when |

|

|

|

| PCRE rolls over from 299 to 0). | |

|

|

|

|

| |

|

| STCLK |

| Not used. | The |

|

|

|

|

| counter increments by the STCLK input. |

1 | ERRFILT | OF(value) |

| Error filtering enable bit. |

|

|

| DEFAULT | 0 | Not used. | Packets with errors are received and the |

|

| ACCEPT |

|

| PERR bit is set in the timestamp inserted |

|

|

|

| at the end of the packet. | |

|

|

|

|

| |

|

| REJECT |

| Not used. | Packets with errors are filtered out (not |

|

|

|

|

| received in the FIFO). |

0 | Reserved | - | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field | |

|

|

|

| has no effect. |

|

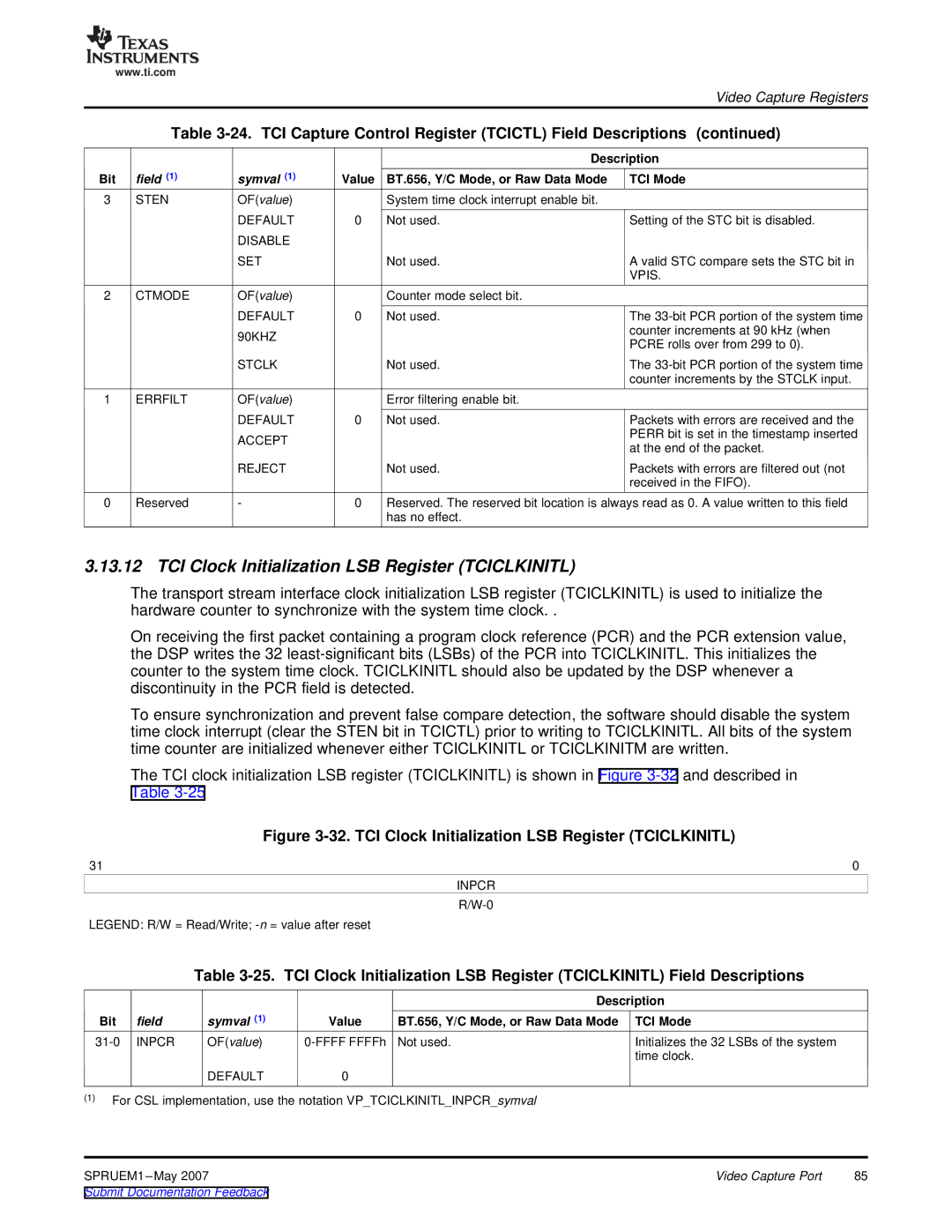

3.13.12 TCI Clock Initialization LSB Register (TCICLKINITL)

The transport stream interface clock initialization LSB register (TCICLKINITL) is used to initialize the hardware counter to synchronize with the system time clock. .

On receiving the first packet containing a program clock reference (PCR) and the PCR extension value, the DSP writes the 32

To ensure synchronization and prevent false compare detection, the software should disable the system time clock interrupt (clear the STEN bit in TCICTL) prior to writing to TCICLKINITL. All bits of the system time counter are initialized whenever either TCICLKINITL or TCICLKINITM are written.

The TCI clock initialization LSB register (TCICLKINITL) is shown in Figure

Figure 3-32. TCI Clock Initialization LSB Register (TCICLKINITL)

31 | 0 |

INPCR

LEGEND: R/W = Read/Write;

Table

|

|

|

| Description | |

Bit | field | symval (1) | Value | BT.656, Y/C Mode, or Raw Data Mode | TCI Mode |

INPCR | OF(value) | Not used. | Initializes the 32 LSBs of the system | ||

|

|

|

|

| time clock. |

|

| DEFAULT | 0 |

|

|

(1)For CSL implementation, use the notation VP_TCICLKINITL_INPCR_symval

SPRUEM1 | Video Capture Port | 85 |

Submit Documentation Feedback |

|

|