www.ti.com

Display Timing Examples

VCLKIN

FPCOUNT

IPCOUNT

VCTL1 (HBLNK)(A)(C)

VCTL1 (HSYNC)(A)(C)

VCLKOUT

VDOUT[9−2]

FLCOUNT

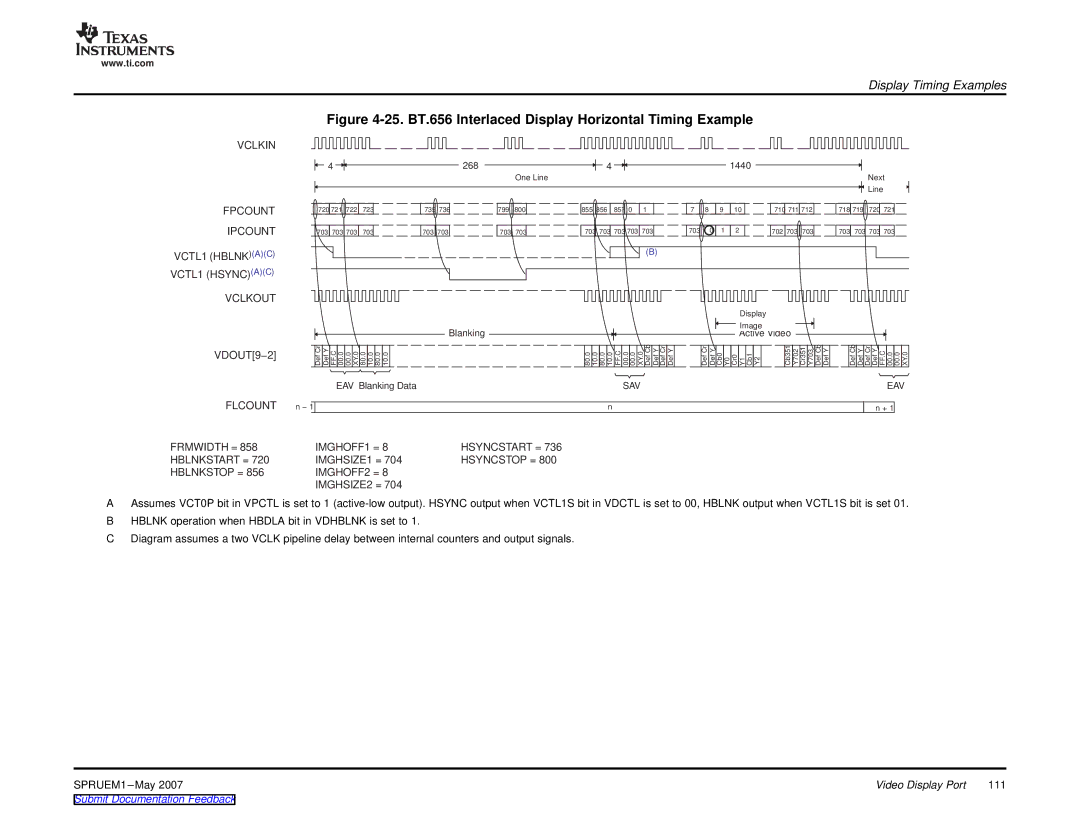

Figure 4-25. BT.656 Interlaced Display Horizontal Timing Example

4 |

|

| 268 |

|

| 4 |

|

|

|

|

|

| 1440 |

|

|

|

|

|

|

|

|

|

| One Line |

|

|

|

|

|

|

|

|

|

|

|

| Next |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Line |

720 721 | 722 | 723 | 735 736 | 799 | 800 | 855 856 | 857 0 | 1 | 7 | 8 |

| 9 | 10 | 710 711 712 | 718 719 | 720 721 | ||

703 703 703 | 703 | 703 703 | 703 | 703 | 703 703 703 703 703 | 703 |

| 0 | 1 | 2 | 702 703 | 703 | 703 | 703 703 703 | ||||

|

|

|

|

|

|

|

| (B) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Display |

|

|

|

|

|

|

|

| Blanking |

|

|

|

|

|

|

|

|

| Image |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Active Video |

|

|

|

| ||

Def Cr Def Y FF.C 00.0 | 00.0 XY.0 | 80.0 10.0 80.0 | 10.0 |

|

| 80.0 10.0 80.0 10.0 | FF.C 00.0 00.0 XY.0 | Def Cb Def Y Def Cr Def Y |

| Def Cr | Def Y | Cb0 Y0 | Cr0 Y1 Cb1 Y2 | Cb351 Y702 | Cr351 Y703 Def Cb Def Y | Def Cb Def Y | Def Cr Def Y FF.C 00.0 00.0 XY.0 | |

EAV Blanking Data |

|

|

| SAV |

|

|

|

|

|

|

|

|

|

| EAV | |||

n − 1 |

|

|

|

|

| n |

|

|

|

|

|

|

|

|

|

|

| n + 1 |

FRMWIDTH = 858 | IMGHOFF1 = 8 | HSYNCSTART = 736 |

HBLNKSTART = 720 | IMGHSIZE1 = 704 | HSYNCSTOP = 800 |

HBLNKSTOP = 856 | IMGHOFF2 = 8 |

|

| IMGHSIZE2 = 704 |

|

AAssumes VCT0P bit in VPCTL is set to 1

BHBLNK operation when HBDLA bit in VDHBLNK is set to 1.

CDiagram assumes a two VCLK pipeline delay between internal counters and output signals.

SPRUEM1 | Video Display Port | 111 |

Submit Documentation Feedback |

|

|