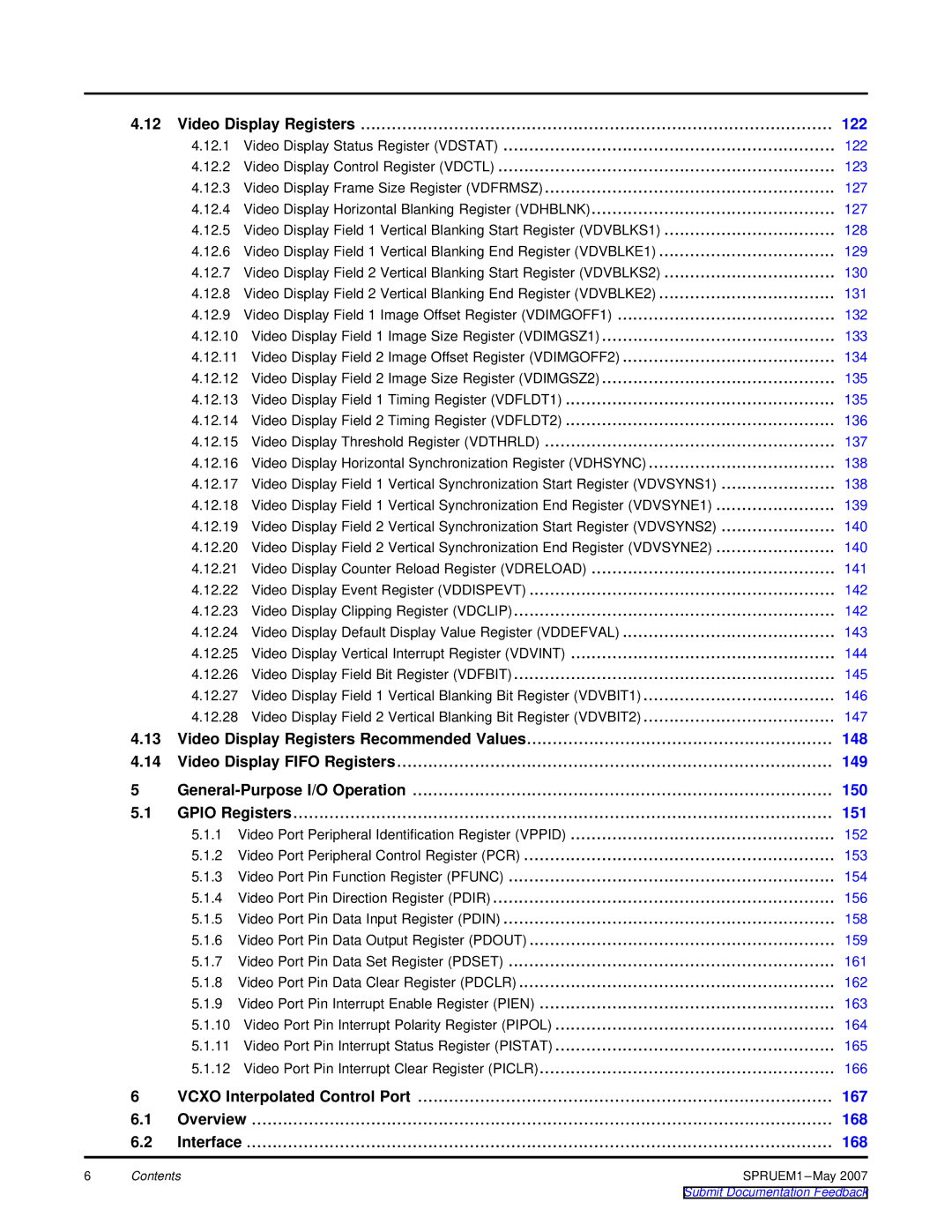

| 4.12 | Video Display Registers | 122 |

|

| 4.12.1 Video Display Status Register (VDSTAT) | 122 |

|

| 4.12.2 Video Display Control Register (VDCTL) | 123 |

|

| 4.12.3 Video Display Frame Size Register (VDFRMSZ) | 127 |

|

| 4.12.4 Video Display Horizontal Blanking Register (VDHBLNK) | 127 |

|

| 4.12.5 Video Display Field 1 Vertical Blanking Start Register (VDVBLKS1) | 128 |

|

| 4.12.6 Video Display Field 1 Vertical Blanking End Register (VDVBLKE1) | 129 |

|

| 4.12.7 Video Display Field 2 Vertical Blanking Start Register (VDVBLKS2) | 130 |

|

| 4.12.8 Video Display Field 2 Vertical Blanking End Register (VDVBLKE2) | 131 |

|

| 4.12.9 Video Display Field 1 Image Offset Register (VDIMGOFF1) | 132 |

|

| 4.12.10 Video Display Field 1 Image Size Register (VDIMGSZ1) | 133 |

|

| 4.12.11 Video Display Field 2 Image Offset Register (VDIMGOFF2) | 134 |

|

| 4.12.12 Video Display Field 2 Image Size Register (VDIMGSZ2) | 135 |

|

| 4.12.13 Video Display Field 1 Timing Register (VDFLDT1) | 135 |

|

| 4.12.14 Video Display Field 2 Timing Register (VDFLDT2) | 136 |

|

| 4.12.15 Video Display Threshold Register (VDTHRLD) | 137 |

|

| 4.12.16 Video Display Horizontal Synchronization Register (VDHSYNC) | 138 |

|

| 4.12.17 Video Display Field 1 Vertical Synchronization Start Register (VDVSYNS1) | 138 |

|

| 4.12.18 Video Display Field 1 Vertical Synchronization End Register (VDVSYNE1) | 139 |

|

| 4.12.19 Video Display Field 2 Vertical Synchronization Start Register (VDVSYNS2) | 140 |

|

| 4.12.20 Video Display Field 2 Vertical Synchronization End Register (VDVSYNE2) | 140 |

|

| 4.12.21 Video Display Counter Reload Register (VDRELOAD) | 141 |

|

| 4.12.22 Video Display Event Register (VDDISPEVT) | 142 |

|

| 4.12.23 Video Display Clipping Register (VDCLIP) | 142 |

|

| 4.12.24 Video Display Default Display Value Register (VDDEFVAL) | 143 |

|

| 4.12.25 Video Display Vertical Interrupt Register (VDVINT) | 144 |

|

| 4.12.26 Video Display Field Bit Register (VDFBIT) | 145 |

|

| 4.12.27 Video Display Field 1 Vertical Blanking Bit Register (VDVBIT1) | 146 |

|

| 4.12.28 Video Display Field 2 Vertical Blanking Bit Register (VDVBIT2) | 147 |

| 4.13 Video Display Registers Recommended Values | 148 | |

| 4.14 | Video Display FIFO Registers | 149 |

| 5 | 150 | |

| 5.1 | GPIO Registers | 151 |

|

| 5.1.1 Video Port Peripheral Identification Register (VPPID) | 152 |

|

| 5.1.2 Video Port Peripheral Control Register (PCR) | 153 |

|

| 5.1.3 Video Port Pin Function Register (PFUNC) | 154 |

|

| 5.1.4 Video Port Pin Direction Register (PDIR) | 156 |

|

| 5.1.5 Video Port Pin Data Input Register (PDIN) | 158 |

|

| 5.1.6 Video Port Pin Data Output Register (PDOUT) | 159 |

|

| 5.1.7 Video Port Pin Data Set Register (PDSET) | 161 |

|

| 5.1.8 Video Port Pin Data Clear Register (PDCLR) | 162 |

|

| 5.1.9 Video Port Pin Interrupt Enable Register (PIEN) | 163 |

|

| 5.1.10 Video Port Pin Interrupt Polarity Register (PIPOL) | 164 |

|

| 5.1.11 Video Port Pin Interrupt Status Register (PISTAT) | 165 |

|

| 5.1.12 Video Port Pin Interrupt Clear Register (PICLR) | 166 |

| 6 | VCXO Interpolated Control Port | 167 |

| 6.1 | Overview | 168 |

| 6.2 | Interface | 168 |

6 | Contents | SPRUEM1 | |