www.ti.com

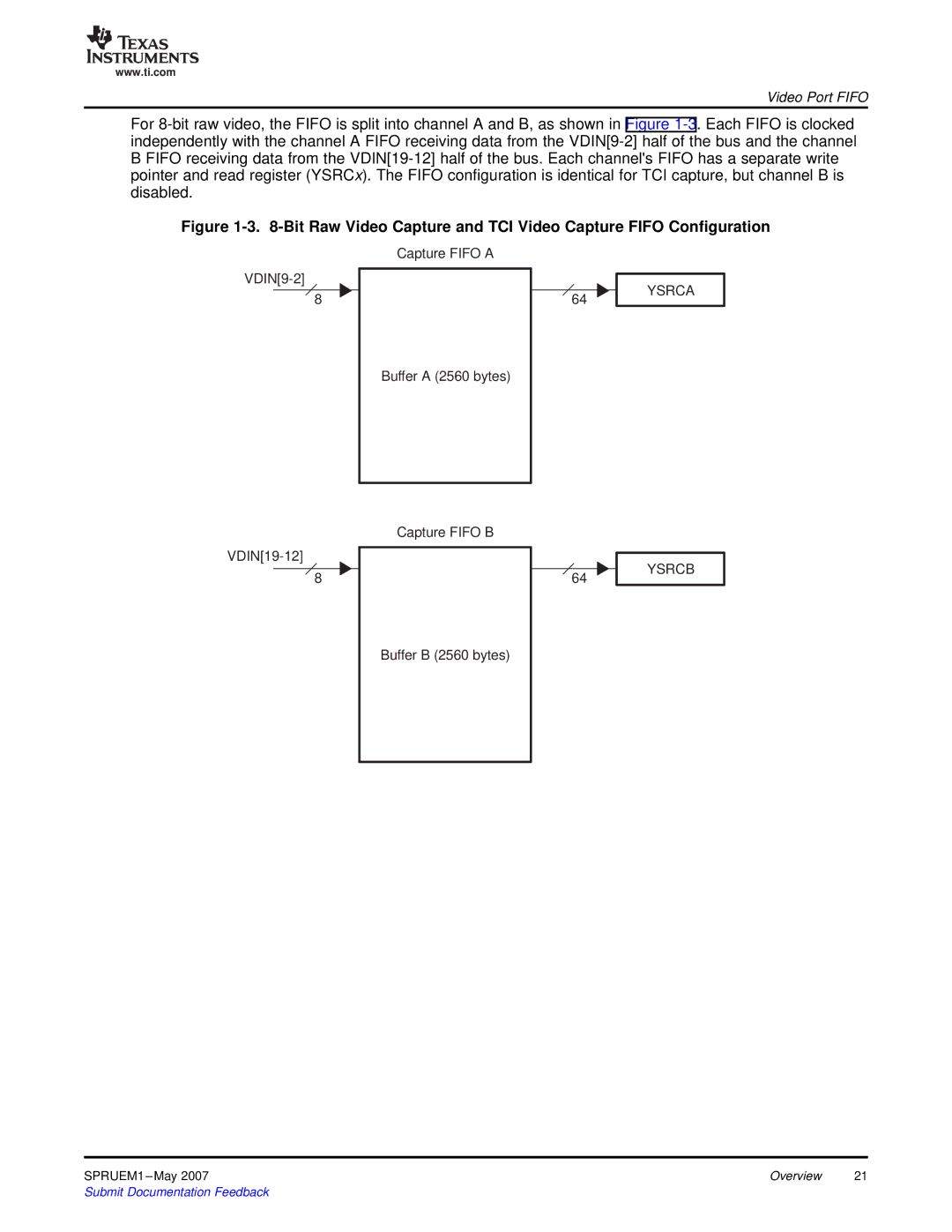

Video Port FIFO

For

Figure 1-3. 8-Bit Raw Video Capture and TCI Video Capture FIFO Configuration

Capture FIFO A

VDIN[9−2]

8

64

YSRCA

Buffer A (2560 bytes)

Capture FIFO B

VDIN[19−12]

8

64

YSRCB

Buffer B (2560 bytes)

SPRUEM1 | Overview | 21 |