www.ti.com

Video Port Control Registers

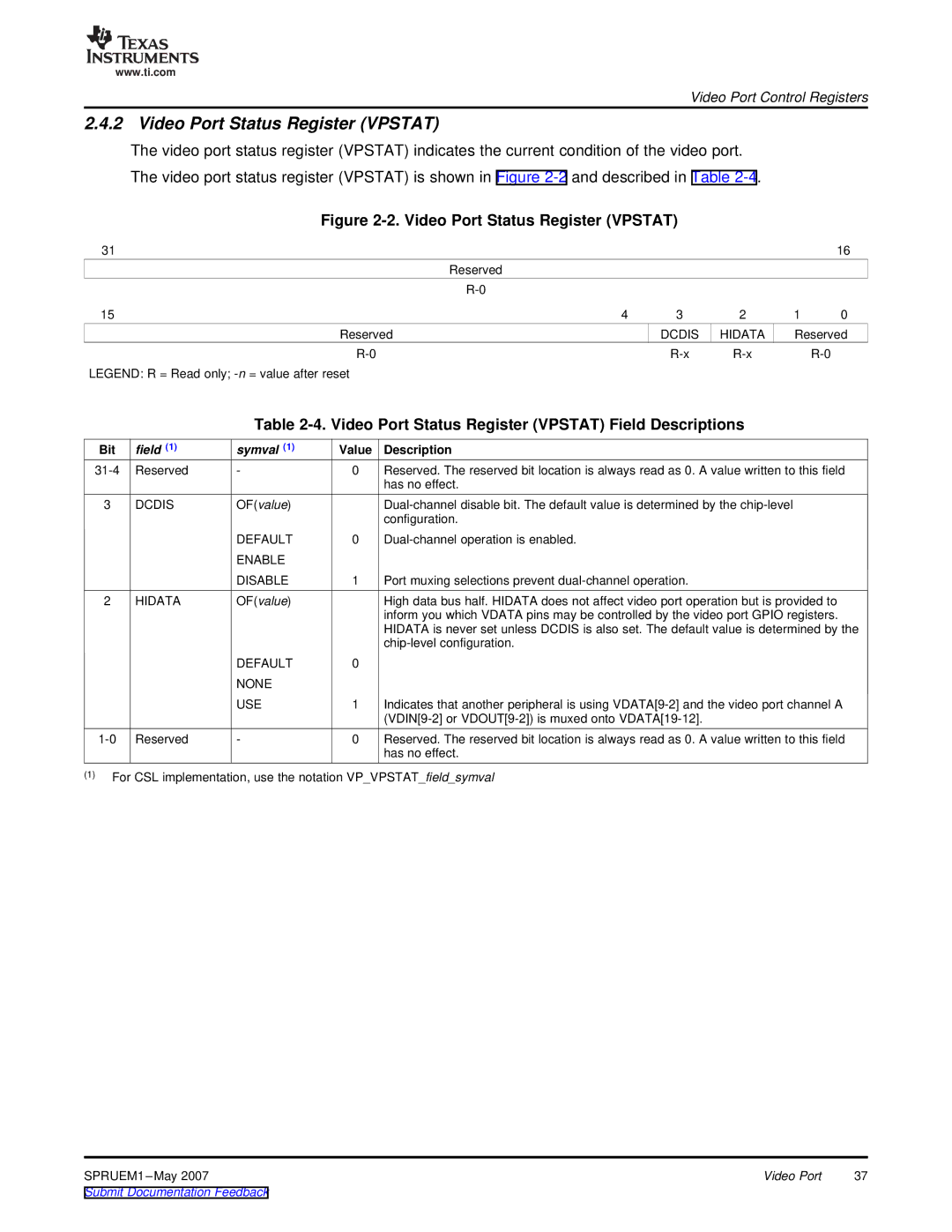

2.4.2 Video Port Status Register (VPSTAT)

The video port status register (VPSTAT) indicates the current condition of the video port. The video port status register (VPSTAT) is shown in Figure

Figure 2-2. Video Port Status Register (VPSTAT)

31 |

|

|

|

| 16 |

| Reserved |

|

|

|

|

|

|

|

|

| |

15 | 4 | 3 | 2 | 1 | 0 |

Reserved |

| DCDIS | HIDATA | Reserved | |

|

| ||||

LEGEND: R = Read only;

Table 2-4. Video Port Status Register (VPSTAT) Field Descriptions

Bit | field (1) | symval (1) | Value | Description |

Reserved | - | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field | |

|

|

|

| has no effect. |

3 | DCDIS | OF(value) |

| |

|

|

|

| configuration. |

|

| DEFAULT | 0 | |

|

| ENABLE |

|

|

|

| DISABLE | 1 | Port muxing selections prevent |

2 | HIDATA | OF(value) |

| High data bus half. HIDATA does not affect video port operation but is provided to |

|

|

|

| inform you which VDATA pins may be controlled by the video port GPIO registers. |

|

|

|

| HIDATA is never set unless DCDIS is also set. The default value is determined by the |

|

|

|

| |

|

| DEFAULT | 0 |

|

|

| NONE |

|

|

|

| USE | 1 | Indicates that another peripheral is using |

|

|

|

| |

Reserved | - | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field | |

|

|

|

| has no effect. |

(1)For CSL implementation, use the notation VP_VPSTAT_field_symval

SPRUEM1 | Video Port | 37 |

Submit Documentation Feedback |

|

|