www.ti.com

VIC Port Registers

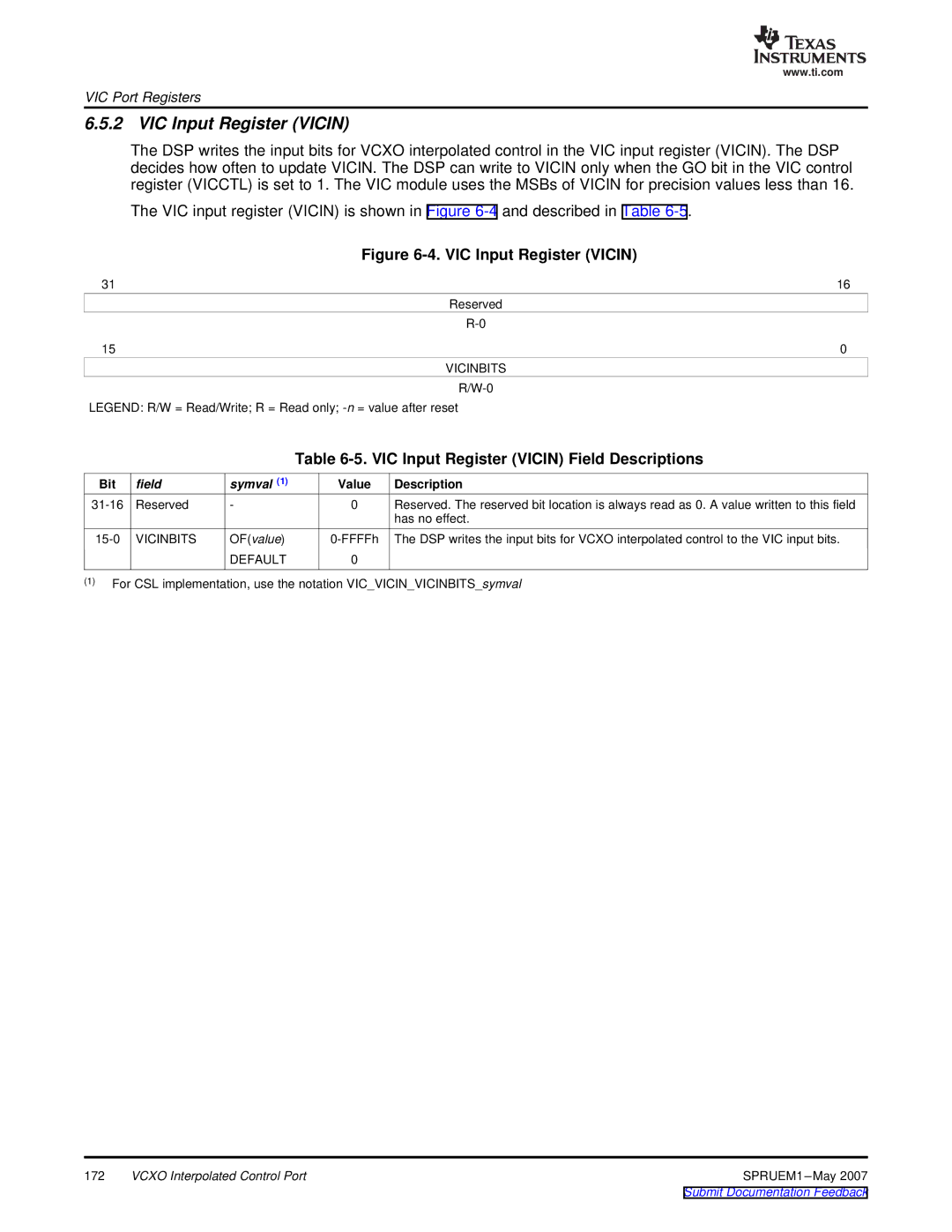

6.5.2 VIC Input Register (VICIN)

The DSP writes the input bits for VCXO interpolated control in the VIC input register (VICIN). The DSP decides how often to update VICIN. The DSP can write to VICIN only when the GO bit in the VIC control register (VICCTL) is set to 1. The VIC module uses the MSBs of VICIN for precision values less than 16.

The VIC input register (VICIN) is shown in Figure

| Figure |

31 | 16 |

| Reserved |

| |

15 | 0 |

VICINBITS

LEGEND: R/W = Read/Write; R = Read only;

Table 6-5. VIC Input Register (VICIN) Field Descriptions

Bit | field | symval (1) | Value | Description |

Reserved | - | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field | |

|

|

|

| has no effect. |

VICINBITS | OF(value) | The DSP writes the input bits for VCXO interpolated control to the VIC input bits. | ||

|

| DEFAULT | 0 |

|

(1)For CSL implementation, use the notation VIC_VICIN_VICINBITS_symval

172 | VCXO Interpolated Control Port | SPRUEM1 |

|

| Submit Documentation Feedback |