www.ti.com

BT.656 and Y/C Mode Field and Frame Operation

to which a continuous stream of fields are stored without DSP intervention. In other cases, the DSP may need to modify EDMA pointer addresses after each field or frame is captured. In some applications, only one field may be captured and the other ignored completely, or a frame may need to be ignored in order to have time to process a previous frame. The video port addresses these issues by providing programmable control over different aspects of the capture process.

3.4.1 Capture Determination and Notification

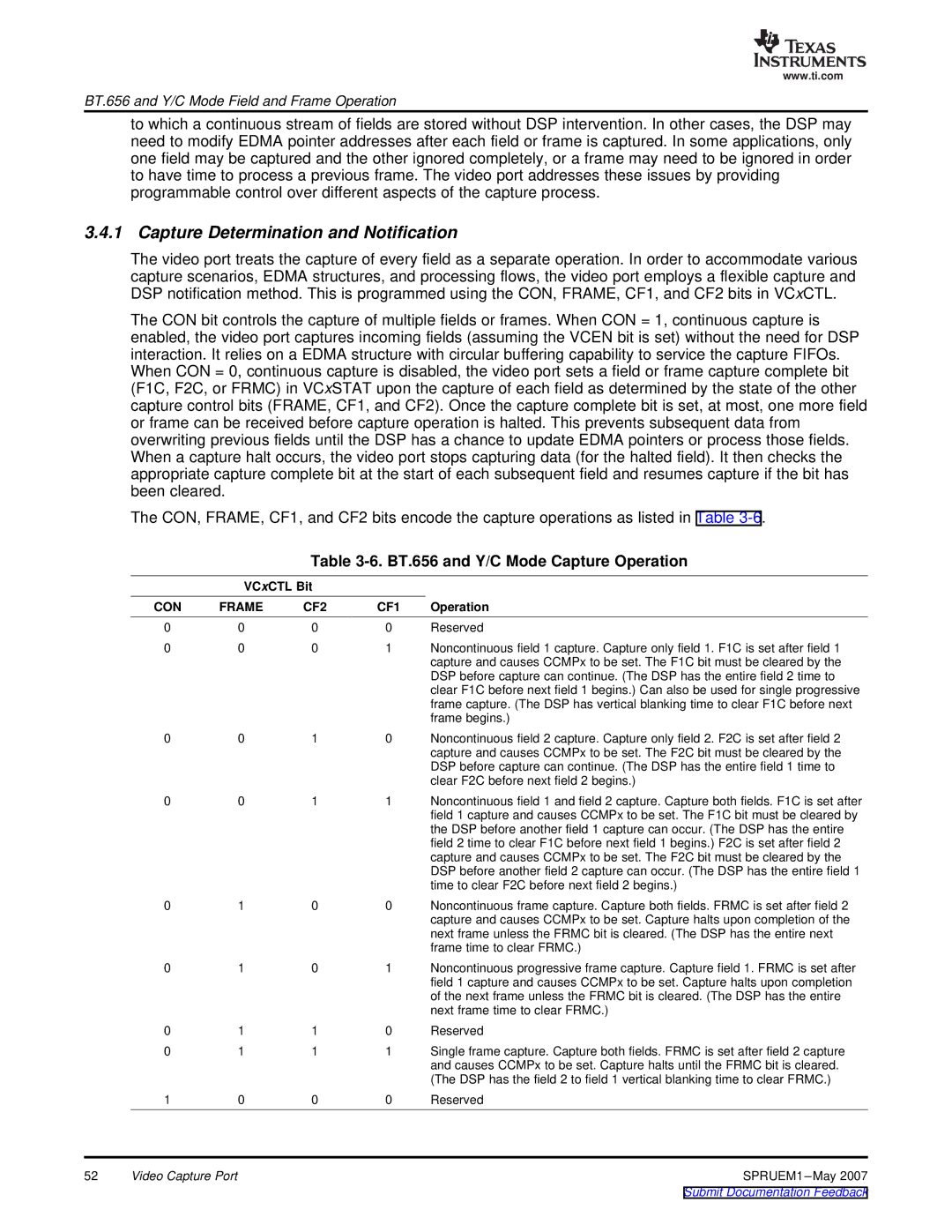

The video port treats the capture of every field as a separate operation. In order to accommodate various capture scenarios, EDMA structures, and processing flows, the video port employs a flexible capture and DSP notification method. This is programmed using the CON, FRAME, CF1, and CF2 bits in VCxCTL.

The CON bit controls the capture of multiple fields or frames. When CON = 1, continuous capture is enabled, the video port captures incoming fields (assuming the VCEN bit is set) without the need for DSP interaction. It relies on a EDMA structure with circular buffering capability to service the capture FIFOs. When CON = 0, continuous capture is disabled, the video port sets a field or frame capture complete bit (F1C, F2C, or FRMC) in VCxSTAT upon the capture of each field as determined by the state of the other capture control bits (FRAME, CF1, and CF2). Once the capture complete bit is set, at most, one more field or frame can be received before capture operation is halted. This prevents subsequent data from overwriting previous fields until the DSP has a chance to update EDMA pointers or process those fields. When a capture halt occurs, the video port stops capturing data (for the halted field). It then checks the appropriate capture complete bit at the start of each subsequent field and resumes capture if the bit has been cleared.

The CON, FRAME, CF1, and CF2 bits encode the capture operations as listed in Table

Table 3-6. BT.656 and Y/C Mode Capture Operation

| VCxCTL Bit |

|

| |

CON | FRAME | CF2 | CF1 | Operation |

0 | 0 | 0 | 0 | Reserved |

0 | 0 | 0 | 1 | Noncontinuous field 1 capture. Capture only field 1. F1C is set after field 1 |

|

|

|

| capture and causes CCMPx to be set. The F1C bit must be cleared by the |

|

|

|

| DSP before capture can continue. (The DSP has the entire field 2 time to |

|

|

|

| clear F1C before next field 1 begins.) Can also be used for single progressive |

|

|

|

| frame capture. (The DSP has vertical blanking time to clear F1C before next |

|

|

|

| frame begins.) |

0 | 0 | 1 | 0 | Noncontinuous field 2 capture. Capture only field 2. F2C is set after field 2 |

|

|

|

| capture and causes CCMPx to be set. The F2C bit must be cleared by the |

|

|

|

| DSP before capture can continue. (The DSP has the entire field 1 time to |

|

|

|

| clear F2C before next field 2 begins.) |

0 | 0 | 1 | 1 | Noncontinuous field 1 and field 2 capture. Capture both fields. F1C is set after |

|

|

|

| field 1 capture and causes CCMPx to be set. The F1C bit must be cleared by |

|

|

|

| the DSP before another field 1 capture can occur. (The DSP has the entire |

|

|

|

| field 2 time to clear F1C before next field 1 begins.) F2C is set after field 2 |

|

|

|

| capture and causes CCMPx to be set. The F2C bit must be cleared by the |

|

|

|

| DSP before another field 2 capture can occur. (The DSP has the entire field 1 |

|

|

|

| time to clear F2C before next field 2 begins.) |

0 | 1 | 0 | 0 | Noncontinuous frame capture. Capture both fields. FRMC is set after field 2 |

|

|

|

| capture and causes CCMPx to be set. Capture halts upon completion of the |

|

|

|

| next frame unless the FRMC bit is cleared. (The DSP has the entire next |

|

|

|

| frame time to clear FRMC.) |

0 | 1 | 0 | 1 | Noncontinuous progressive frame capture. Capture field 1. FRMC is set after |

|

|

|

| field 1 capture and causes CCMPx to be set. Capture halts upon completion |

|

|

|

| of the next frame unless the FRMC bit is cleared. (The DSP has the entire |

|

|

|

| next frame time to clear FRMC.) |

0 | 1 | 1 | 0 | Reserved |

0 | 1 | 1 | 1 | Single frame capture. Capture both fields. FRMC is set after field 2 capture |

|

|

|

| and causes CCMPx to be set. Capture halts until the FRMC bit is cleared. |

|

|

|

| (The DSP has the field 2 to field 1 vertical blanking time to clear FRMC.) |

1 | 0 | 0 | 0 | Reserved |

52 | Video Capture Port | SPRUEM1 |