Page

Page

Page

Preface

Page

Table of Contents

Troubleshooting

Operation and Start Up

Parameters

Fault Code Information and Maintenance

Appendix a Specifications Appendix B Accessories

Appendix C How to Select the Right AC Motor Drive

Recommended Position the Rubber Magnet of the Digital Keypad

Introduction

Receiving and Inspection

Nameplate Information

Model Explanation

VFD110VL23A

Series Number Explanation

Drive Frames and Appearances

15HP/5.5-11kWFrame C 20-30HP/15-22kWFrame D

Please refer to .3 for exact dimensions

40-100HP/30-75kWFrame E

VFD750VL43A

Drive Features

Communication Port Internal structure Removable fan

Preparation for Installation and Wiring Ambient Conditions

Operation

Storage

Transportation

Remove Front Cover

15HP/5.5-11kWframe C & 20-30HP/15-22kWframe D

Lifting

40-100HP/30-75kW frame E

Step

Flange Mounting

Fixed plate Fixed pl ate

Fixed plate

Cutout Dimensions

15HP/5.5-11kW frame C

20-30HP/15-22kW frame D

Dimensions

Frame C

Unit mm inch

Frame

Frame D

255.0 226.0 403.8 384.0 360.0 21.9 168.0 10.04 15.90 15.12

Frame D VFD150VL23A/43A, VFD185VL23A/43A, VFD220VL23A/43A

Frame E

This page intentionally left blank

Installation and Wiring

Wiring

Installation and Wiring

Used with internal power +24Vdc

Used with external power

Sink NPN mode Source PNP mode

DC voltage Low voltage level Battery voltage

Run

Valve

EPS detection MI-COM=43 Electromagnetic Valve Drive ready

Loops

Grouning terminals

External Wiring

Main Circuit Main Circuit Connection

Brak e res istor

Pti onal Non-fuse break er

Motor

Mains power terminals R/L1, S/L2, T/L3

Output terminals for main circuit U, V, W

Models Wire Torque Wire Type

Main Circuit Terminals

Models

Torque Wire Type

Control Terminals

Position of External Terminals

OFF

REV

MI1

MI2

Analog input terminals ACI, AUI1, AUI2, ACM

Frame Torque Wire

Digital outputs MO1, MO2, MCM

AWG 0.3-2.1mm2

Terminal 0V/24V Kgf-com1.4 in-lbf AWG 0.051-1.3mm2

Installation and Wiring

Operation and Start Up

Operation Method

STOP/RESET

KPVL-CC01

RUN

Trial Run

Auto-tuning Operations Flow Chart

Basic parameter settings Motor tuning

Explanations for the Auto-tuning Steps

Operation and Start Up

Step

IM motor

PM motor

Step

SIN/COS

EMVL-PGABO/ABL

EMVL-PGABL

EMVL-PGH01/02

Step

Operation and Start Up

Trial run

Operation and Start Up

Operation and Start Up

Operation and Start Up

Parameters

Summary of Parameter Settings

Parameter can be set during operation

Group 0 System Parameters

Focpg Tqcpg Focpm

Group 1 Basic Parameters

Vfpg SVC Focpg Tqcpg Focpm

Group 2 Digital Input/Output Parameters

Vfpg SVC Focpg Tqcpg

By FWD/REV By Enable 02-25

Explanation Settings

Group 3 Analog Input/Output Parameters

03-19

Group 4 Multi-Step Speed Parameters

Group 5 IM Motor Parameters

Group 6 Protection Parameters

~100.0%

Group 7 Special Parameters

Group 8 PM Motor Parameters

Group 9 Communication Parameters

Group 10 Speed Feedback Control Parameters

SIN/COS

Group 11 Advanced Parameters

Group 12 User-defined Parameters

Group 13 View User-defined Parameters

Description of Parameter Settings

00-00

00-01

Factory setting

Content of Multi-Function Display

Factory setting

00-02

SEEEEEEE0 0 HzEE

DI EON/ OFFESt a t

DOEON/ OFFESt a t

FFF

MI8 MI7 MI6 MI5 MI4 MI3 MI2 MI1 REV FWD

Factory setting Read Only

Settings Read Only Display #.##

00-05

User Defined Coefficient K

Password Input Unit

Password Set Unit

Settings To 9998 and 10000 to Display

00-07

Decoding Flow Chart

Pass word Setting

00-09Control Method

00-10

00-11

00-12

230V/460V Series

Source of the Master Frequency Command

Source of the Operation Command

00-14

00-15

01-01

01-02

01-03

01-04

01-05

01-06

01-07

01-09

01-10

Output Frequency Upper Limit Unit

01-11

01-12

01-14

01-16

01-18

Switch Frequency between 1st/4th Accel/decel Unit

01-22

JOG Frequency Unit

01-23

1st/4th Acceleration/Deceleration Switching

01-29

01-28

01-31

Parameters

02-00

02-01

02-00 Control Circuits of the External Terminal

02-02

02-03

02-04

02-05

Settings Functions Descriptions

By Pr.07-28 setting

Eeprom

02-09

02-10

MI8 MI7 MI6 MI5 MI4 MI3 MI2 MI1 REV

02-11

02-12

Settings Control Mode

Settings Functions Descriptions

Active when the warning is detected

Enable

Input MI=40

Multifunction output MO=15

02-23

02-25

02-26

02-27

02-28

02-31

02-32

2 7=S

02-33

02-34

02-35

03-00

03-01

03-02

Settings 100.0~100.0%

03-03

Analog Input Bias 1 AUI1 Unit

03-04

03-05

03-06

03-07

03-08

03-12

03-13

03-14

03-15

03-18

Analog Output Gain Unit

03-21

04-00

04-01

04-02

04-03

Pr 06 Pr Equivalent circuit for VFD -VL ser ie s

05-00

Factory setting #.##

Settings 40 to 120%

05-02

05-03

05-12

05-13

05-14

05-15

05-16

05-17

Settings To 250%

05-20

Core Loss Compensation Unit

06-00

06-01

06-02

06-03

06-04

06-05

06-06

06-07

06-08

Pr.06-06

Pr.06-09

Pr.06-07

06-10

Operation time min

Load

Fac tor %

60Hz

Readings No fault

06-16 06-17 06-18 06-19 06-20 06-21

Parameters

Setting Method of Fault Output

Bit Fault code

06-30

Bit Fault code

Fault code Bit0 Bit1 Bit2 Bit3 Bit4 Bit5 Bit6 Current Volt

06-22

06-23

06-24

Bit1 Bit2 Bit3 Bit4 Bit5 Bit6 Fault code Volt

Fault code Current Volt. OL

Bit0 Bit1 Bit2 Bit3 Bit4 Bit5

06-26

06-27

06-28

06-29

07-00

07-01

07-02

07-03

07-05

07-0

07-06

07-07

07-11

07-12

07-13

07-14

07-15

07-17

07-18

07-19

07-20

07-21

07-22

07-23

07-24

07-25

07-26

100%

300% x 07-29=t

00-01

07-28

08-00Motor Auto Tuning

Settings No function

Rated Power of Motor Unit

08-02

08-03

08-04

08-05

08-06

Parameters

RS-485 5 NC 6 NC

09-00

09-01

09-02

Ascii mode

RTU mode

Code Description

STX

Data

Start

END

FEH

5CH

A0H

Count by word 02H CRC CHK Low

6FH

F7H

Content

AC drive Parameters Command Write only

Address Function

GG means parameter group, nn means parameter number

Content Address Function

Ascii mode RTU mode

A1H

Exception

09-05

ABZ

SIN/COS+

Settings Disable

Motor will run Motor won’t run 10-00=5

Motor will run 10-00=6

10-01

10-03

10-04

10-05

10-06

10-08

10-09

10-11

10-12

10-18

10-19

10-20

10-21

10-22

10-23

10-24

Setting auto gain adjustment Pr.11-00=1

Adjust by requirement

11-00

System Control

11-01

11-02

11-03

11-04

11-05

11-06

11-07

11-08

11-10

11-11

11-12

11-13

11-14

11-15

FREQ. Esetpoi NTn t

SEEEEEE6 0 1 2 0 0 Prog

Umap ADD0 Eeeetee SEEEEE0 8 0 3 0 8 0 3 0

PMSMOTORUB- Emf ET SEEEEEE6 0 1 3 0 0 Prog

FREQ. Esetpoi NTn t SEEEEEE6 0 Hz EEE

SEEEEEE6 0 1 2- 0 0 Prog

EEE- EEn d . E- EEE Eeeeeeeeeeeeeeee

DI SPL AYEUSER- SET SEEEEEE6 0 1 3 0

FREQ. Esetpoi NTn t SEEEEEE6 0 Hz EEE Prog

Systemsparameter press SEEEEEE6 0 0 0 EE twice

Ma x Eo f s Fc md i n t ET SEEEEEE6 0 1 3 0

2127

Settings Refer to group 12 for details

13-00

View User-defined Parameters

13-31

Troubleshooting

Over Current OC

Ground Fault

Ground fault

Over Voltage OV

Suitable power

Low Voltage Lv

Over Heat OH

Overload

Phase Loss PHL

Display of KPVL-CC01 is Abnormal

Yes

Motor cannot Run

Motor Speed cannot be Changed

Motor Stalls during Acceleration

Motor does not Run as Expected

Electromagnetic/Induction Noise

Environmental Condition

Affecting Other Machines

Fault Code Information and Maintenance

Fault Code Information

Common Problems and Solutions

EEE Fault Co d e 0 E

Ea t EAc c e l Eeeee

EEE F a u l t code 0 E3

EEE Fault Co d e 0 9 E

Display Description Ground fault Corrective Actions

Motor drive protection, not for protection of the user

EEE Fault code 1 E

Ea t ES t o p Eeeeee

EEE Fault code 2 E0

Eeef a u l t code 2 2 E

EEE Fault code 3 0 E

EEE Fault code 3 2 E

EEE Fault code 3 E

EEE Fault code 2 E7

FEEEFault code 3 E9

EEE Fault Co d e 4 E

EEE Fault code 4 E

EHWEEr r o r Eeeee

EEE Fault Co d e 5 E

PC EE r r ECo mma n d EE

EEE Fa u l t code 5 E

EEEFa u l t code 5 E6

Reset

EEE Fault code 5 E

Eeef a u l t code 6 3 E

Fault Code Information and Maintenance

Maintenance and Inspections

Voltage Maintenance Check Items Methods and Criterion

Keypad Maintenance Check Items Methods and Criterion

One

Main circuit Maintenance Check Items Methods and Criterion

Change of copper plate

Year

Visual, aural inspection and smell Or peculiar smell

Daily

Change fan Overheat

Daily

This page intentionally left blank

Appendix a Specifications

Per torque 100% Accel up 140% Cruise 80% Decel up Post

General Specifications

This page intentionally left blank

Appendix B Accessories

All Brake Resistors & Brake Units Used in AC Motor Drives

Decrease accordingly. Recommended cycle time is one minute

Appendix B Accessories

Dimensions and Weights for Brake Resistors

Dimensions are in millimeter

Order P/N BR500W030, BR500W100, BR1K0W020, BR1K0W075

Specifications for Brake Unit

Dimensions for Brake Unit

121.0 80.0 130.0

189.5 200.0

VFDB4132

Non-fuse Circuit Breaker Chart

Fuse Specification Chart

Phase Model

Model Recommended Input Current a

110 120 225

142 145 250

130 110 250

160 150 300

AC Reactor AC Input Reactor Recommended Value

AC Output Reactor Recommended Value

Impedance

37.5 52.5 18.5 67.5 82.5 120 100 150 130 195

Applications for AC Reactor

37.5 52.5 18.5 67.5 120 100 150 130 195 160 240

Correct wiring

M1 reactor

AC motor drive

AC motor drive Motor

Silicon rectifier Powerreactor AC motor drive Reactor Motor

Zero Phase Reactor RF220X00A

Diagram a

Diagram B

Nominal Method

230Vac Built-in 50/60Hz 18.5 110 Phase 125 460V DC Choke

460Vac 18.5 Built-in 50/60Hz Phase 110 125 200 100 240

DC Choke Recommended Values

230V DC Choke

Digital Keypad KPVL-CC01

Description of the Digital Keypad KPVL-CC01

=Sto p

=Ru n

Paramecopyeeeeee SEEEREADE1 Eeeeee

Paramecopyeeeeee SEEESAVEE1 Ev 1

Syst Emeparameter S0 EEEEEEEE0 0 EE

EEE- EEr r . E- EEE

How to Operate the Digital Keypad KPVL-CC01

To set parameters

When Read 1 starts blinking, it starts to save to KPVL-CC01

Enter parameter settings

From drive to KPVL-CC01

Press and hold on for about 5 seconds

Dimension of the Digital Keypad

Recommended Position the Rubber Magnet of the Digital Keypad

Terminal Symbols

Specifications

PG Card for Encoder

V, V, W, W

Encoder

Line driver

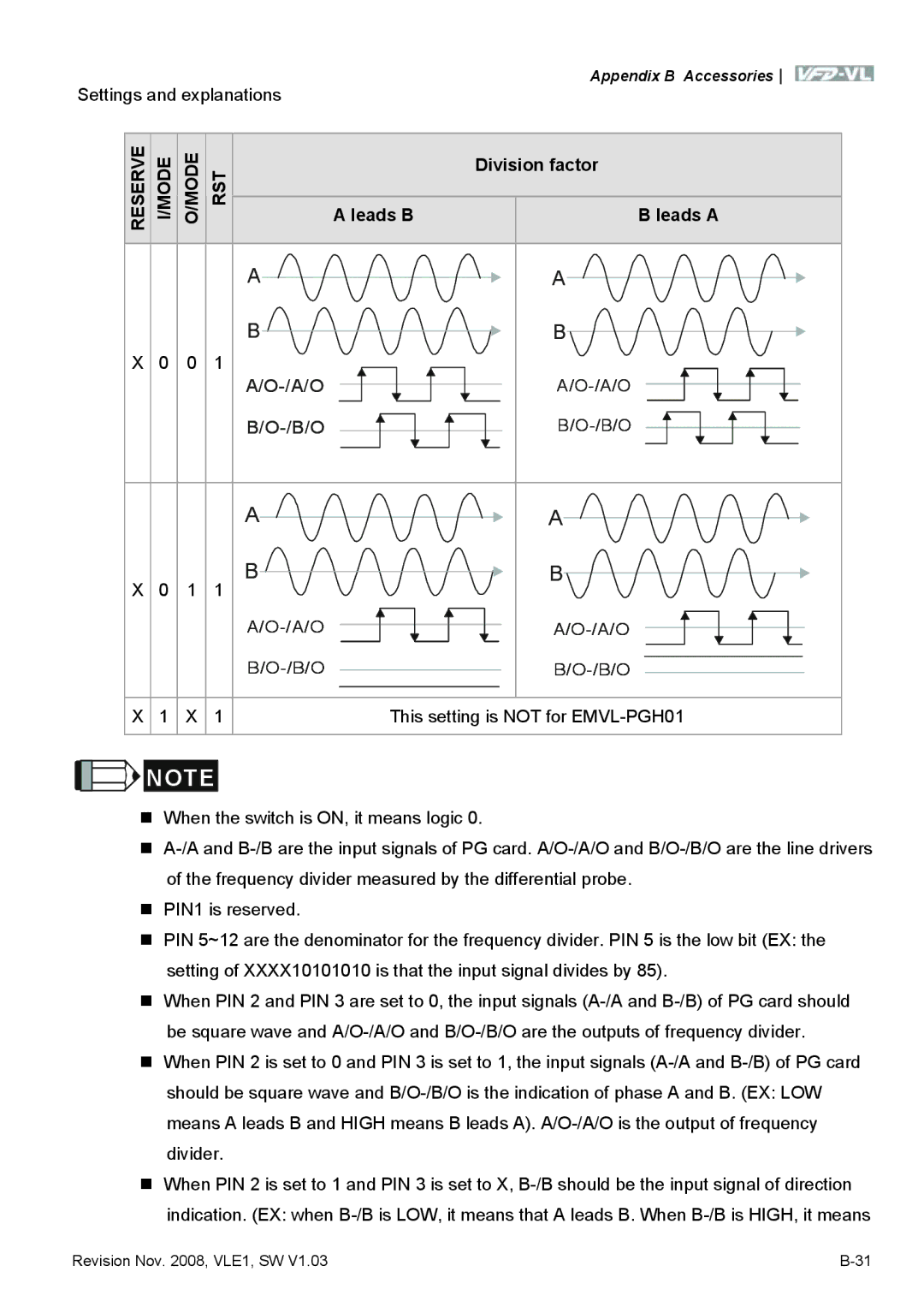

Division Factor

10 11

A/O

B/O

A/O B/O

Terminal Symbols Descriptions

Power source of encoder

Power source common for

TB1

A/O, B/O, B/O Z/O

Open collector

Leads B Leads a A/O B/O

EMVL-PGH01 only for Heidenhain ERN1387

Sinusoidal Encoder Function

+5V Vdc

900el

SIN COS COS 900mech

Terminal Symbols Descriptions Specifications

+ Z

SIN, SIN’

COS, COS’

Division factor

Leads B Leads a

EMVL-PGS01

+COS

Refcos

+SIN

Encoder

+ +CO S

+ +S

Data+

OA-GND OB-GND

OA-GND

Appendix B Accessories

AMD-EMI Filter Cross Reference

AC Drives Model Number FootPrint

50TDS4W4C VFD185VL43A

„ EN61000-6-4 „ EN61800-3 „ EN55011 1991 Class a Group

Saddle on both ends Saddle on one end

Length of motor cable

Dimensions are in millimeter and inch

230VAC input voltage

Order P/N RF110B43CA

Order P/N 50TDS4W4C Order P/N 100TDS84C

Order P/N 200TDDS84C

Order P/N 150TDS84C Order P/N 180TDS84C

Max +24V/5mA MO3~MO10 Internal circuit MCM

AVO1-AGND AVO2-AGND

AVO1 Agnd MO10 MO9 MO8

MCM MO7 MO6 MO5 MO 4 MO3

Safety Relay EMVL-SAF01 Functions of the Terminals

Wiring of the Safety Relay

Relay contact Connect to J P19 On the c ontrol board

Descriptions

This page intentionally left blank

Related Specification

Speed Time Overload Starting Torque Ratings

When one AC motor drive operates one motor

When one AC motor drive operates more than one motor

Capacity Formulas

„ Acceleration time ≧60 seconds Starting capacity=

⋅ IM ≤ the rated current of AC motor drive a

General Precaution

Parameter Settings Note

Selection Note

How to Choose a Suitable Motor

Torque% 25% 40% 60% 100 Continuous Frequency Hz

Standard motor

Special motors

Pole-changing Dahlander motor

Power Transmission Mechanism

Motor torque

This page intentionally left blank

![]()

![]()

![]()

![]() NOTE

NOTE