Intel 815 Chipset Graphics Controller

Programmer’s Reference Manual PRM

Intel 815 Chipset Graphics Controller PRM, Rev

Contents

100

106

141

Monosrccopyimmediateblt

Gfxrenderstatemaplodlimits

15.4.3.3 HORZPH-Horizontal Phase Register 279 15.4.3.4

16.2.5

Figures

Tables

Date

Revision History

Rev

This page is intentionally left blank

Term Description

Introduction

Terminology

Reference Documents

MCH

Intel 815 Chipset Overview

I/O Controller Hub

Intel 82815 Chipset Gmch Overview

Intel 82815 Chipset Gmch Block Diagram

Host Interface

Multiplexed AGP and Display Cache Interface

Data Rate Signaling Level

System Memory Interface

Hub Interface

Intel 82815 Chipset Gmch Integrated Graphics Support

Gmch Power Delivery

Three PCI Devices on Gmch

System Clocking

Front Side Bus System Memory Display Cache Interface

Supported Single Monitor and Multi-monitor Configurations

Multi-Mode Capability Requirements

Configuration Single Monitor Multi-monitor

Device Mode Auto-Detect Flowchart

System Startup

Software Start-Up Sequence

Graphics Driver Startup

Switching Device modes

System Address Map

System Memory Space

Memory and I/O Space Registers

Graphics Controller Register Memory and I/O Map

Reserved 50000h−5FFFFh. Reserved in the Intel 815 chipset

Address Offset Symbol Register Name Access

GC Register Memory Address Map

VGA and VGA Extended Registers

Instruction and Interrupt Control Registers 01000h −02FFFh

Instpm

OV0ADD

Ssladd

VGA and Extended VGA Register Map

Display and Cursor Control Registers 70000h-7FFFFh

VGA and Extended VGA I/O and Memory Register Map

Address Register Name Read Register Name Write 2D Registers

Index Sym Register Name

Indirect VGA and Extended VGA Register Indices

Index Sym Description

2D Attribute Controller Registers 3C0h / 3C1h

CR0F

Graphics Address Translation

Memory Buffers for GC’s Instruction Interface

GTT

Graphics Translation Table GTT Range Definition

This page is intentionally left blank

Basic Initialization Procedures

Vendor Id Device Id PCI Device Characteristics

Initialization Sequence

Hardware Detection Probe

Frame Buffer Initialization

Hardware Register Initialization

Hardware State

Color vs. Monochrome Monitors

Protect Registers Locking and Unlocking

Saving the Hardware State

Restoring the Hardware State

Intel 815 Chipset Graphics Controller PRM, Rev

Intel 815 Chipset Graphics Controller PRM, Rev

This page is intentionally left blank

BLT Engine Programming Considerations

When the Source and Destination Locations Overlap

Blt Engine Programming

Source

Bblt3.vsd

Destination Source Bblt4.vsd

Basic Graphics Data Considerations

Contiguous vs. Discontinuous Graphics Data

Source Data

Monochrome Source Data

Pattern Data

Pattern Data -- Always an 8x8 Array of Pixels

Bpp Pattern Data -- Occupies 64 Bytes 8 quadwords

Destination Data

BLT Programming Examples

Pattern Fill -- a Very Simple BLT

Pattern Data for Example Pattern Fill BLT

Results of Example Pattern Fill BLT

Drawing Characters Using a Font Stored in System Memory

On-Screen Destination for Example Character Drawing BLT

Intel 815 Chipset Graphics Controller PRM, Rev

Results of Example Character Drawing BLT

Initialization Registers

Standard VGA Registers

Smram Registers

SMRAM-System Management RAM Control Register Device

Bit Description

RAM

Initialization and Usage of Stolen Memory

Display and Cursor Control Registers

Clock Control and Power Management Registers

LCD/TV-Out

Graphics Controller Registers 3CEh / 3CFh

CRT Controller Registers 3B4h/3D4h/3B5h/3D5h

Initialization Values for VGA Registers

MSR

GR01 00h

This page is intentionally left blank

Frame Buffer Access

Intel 815 Chipset Graphics Controller PRM, Rev

VGA and Extended VGA Registers

General Control & Status Registers

Name Function Read Write Memory

Offset

1. ST00Input Status

Bit

Display Enable Output

ST01Input Status

Bit Descriptions

Vertical Retrace/Video

FCRFeature Control

Reserved. Read as Vsync Control

CRT HSync Polarity

MSRMiscellaneous Output

CRT VSync Polarity

Sequencer Registers

SRXSequencer Index

2. SR00Sequencer Reset

3. SR01Clocking Mode

Shift

4. SR02Plane/Map Mask

Bit 10,4 Map Number Table Location

5. SR03Character Font

Bit 32 Map Number Table Location

6. SR04Memory Mode Register

Made according to the value of the Plane Mask Register SR02

7. SR07Horizontal Character Counter Reset

Graphics Controller Registers

GRXGRX Graphics Controller Index Register

Bit Description Horizontal Character Counter

2. GR00Set/Reset Register

3. GR01Enable Set/Reset Register

4. GR02Color Compare Register

5. GR03Data Rotate Register

7. GR05Graphics Mode Register

6. GR04Read Plane Select Register

Bits 65=1x

Bits 65=00

Bits 65=01

Write Mode

Odd/Even Mode

Read Mode

Bit

Graphics/Text Mode

8. GR06Miscellaneous Register

Bit Mask

9. GR07Color Don’t Care Register

10. GR08Bit Mask Register

Reserved To Local Memory Enable

Packed Mode Enable

11. GR10Address Mapping

VGA Buffer/Memory Map Select

12. GR11Page Selector

Supported

Memory Offset Address 3CFh Index=14h-1fh Default Attribute

13. GR141FSoftware Flags

Attribute Controller Registers

ARXAttribute Controller Index Register

2. AR000FPalette Registers 0F

3. AR10Mode Control Register

Palette Bits P5, P4 Select

Pixel Width/Clock Select

Enable Blinking/Select Background Intensity

Enable Line Graphics Character Code

Graphics/Alphanumeric Mode

Pixel Panning Compatibility

Bit 54 ST01 Bit

5. AR12Memory Plane Enable Register

4. AR11Overscan Color Register

6. AR13Horizontal Pixel Panning Register

Reserved

Pixel Text Color

Pixel Text Graphics

VGA Color Palette Registers

7. AR14Color Select Register

DACMASKPixel Data Mask Register

DACSTATEDAC State Register

DACRXPalette Read Index Register

DACWXPalette Write Index Register

Bits Index Register Indicated

CRT Controller Register

DACDATAPalette Data Register

Display Fields and Dimensions CRxx Control Registers

CRXCRT Controller Index Register

4. CR02Horizontal Blanking Start Register

3. CR01Horizontal Display Enable End Register

2. CR00Horizontal Total Register

6. CR04Horizontal Sync Start Register

Bit Amount of Delay

5. CR03Horizontal Blanking End Register

7. CR05Horizontal Sync End Register

8. CR06Vertical Total Register

9. CR07Overflow Register

115

116

10. CR08Preset Row Scan Register

Double Scanning Enable

11. CR09Maximum Scan Line Register

12. CR0AText Cursor Start Register

13. CR0BText Cursor End Register

14. CR0CStart Address High Register

15. CR0DStart Address Low Register

16. CR0EText Cursor Location High Register

17. CR0FText Cursor Location Low Register

18. CR10Vertical Sync Start Register

19. CR11Vertical Sync End Register

20. CR12Vertical Display Enable End Register

CR13Offset Register

CR146 CR176 Addressing Mode

22. CR14Underline Location Register

Count By

CR145 CR173 Address Incrementing Interval

23. CR15Vertical Blanking Start Register

24. CR16Vertical Blanking End Register

CR146 CR176

25. CR17CRT Mode Control

Word Mode or Byte Mode

Compatibility Mode Support

Select Row Scan Counter

DWord Mode

Memory Address Counter Address Bits

Frame Buffer Address Decoder

CR17 bit 1=1 CR17 bit 1=0 CR17 bit 0=1 CR17 bit 0=0

26. CR18Line Compare Register

27. CR22Memory Read Latch Data Register

29. CR30Extended Vertical Total Register

30. CR31Extended Vertical Display End Register

31. CR32Extended Vertical Sync Start Register

32. CR33Extended Vertical Blanking Start Register

Extended Horizontal Total MSB that extends CR00

33. CR35 Extended Horizontal Total Time Register

34. CR39Extended Horizontal Blank Time Register

35. CR40Extended Start Address Register

36. CR41Extended Offset Register

37. CR42Extended Start Address High Register

39. CR80I/O Control

Interlace Enable

38. CR70Interlace Control Register

40. CR81Reserved

41. CR82Blink Rate Control

Overview

Programming Interface

Reserved Bits and Software Compatibility

GC Register Programming

GC Instruction Streams

Instruction Use

Instruction Transport Overview

Instruction Parser

Interrupt Ring

Ring Buffers RB

Ring Buffer Registers

Ring Buffer Use

Characteristic Description

Ring Buffer Initialization

Batch Buffers

Batch Buffer Sequence

Wait Instructions

Instruction Arbitration

Arbitration Rationale

Instruction Arbitration Rules

Batch Buffer Protected Mode

Instruction Arbitration Points

Instructions

Instruction Format

Instruction Parser Instructions

Bits

3129 2824 210

Graphics Controller Instructions

Client Instruction

Client

Instruction Parser Instructions

Introduction

Instruction Descriptions

DWord Bit Description

Reserved MBZ

Opcode 01h

Opcode 02h

Gfxcmdparserwaitforevent

DWord Bit

DWord Bits Description

Dwordlength 00h

Opcode 15h

Reserved 00000h

Dword Length 00h

Instruction Target 14h

Flip type 0 Synch flip, 1 Async flip

Opcode 16h

Opcode 07h

Opcode 08h

Arbitration ON/OFF

Instruction Target 11h

Instruction Target 12h

Word Bits Description

Gfxcmdparserbatchbuffer

Instruction Target 30h

BLT Engine Instructions

Instructions

BLTs To and From Cacheable Memory

Setupblt

Setup Background Color All

Setup Foreground Color SLB & TB only

Instruction Target Opcode 00h

Dword Length 06h

Instruction Target Opcode 10h

Dword Length 07h

Color Depth

Raster Operation

Pixelblt

Instruction Target Opcode 20h

Instruction Target Opcode 21h

Destination X2 Coordinate Ending Right

Dword Length 04h

Textblt

Instruction Target Opcode 22h

TEXTImmediateBLT

Instruction Target Opcode 30h

Immediate Data DW

Immediate Data DWs 2 through Dwordlength DWL

Colorblt

Instruction Target Opcode 40h

Dword Length 03h

Solid Pattern Color

Patblt

Instruction Target Opcode 41h

Mono Pattern Transparency Mode 1 = transparency enabled

Monopatblt

Instruction Target Opcode 42h

Pattern Background Color

Srccopyblt

Instruction Target Opcode 43h

Instruction Target Opcode 44h

Line

Source Background Color

Source Foreground Color

Mono Source Transparency Mode 1 = transparency enabled

Instruction Target Opcode 61h

Instruction Target Opcode 45h

Destination Transparency Mode See BR00 definition

Fullblt

Fullmonosrcblt

Destination Transparency Color

Instruction Target Opcode 46h

Instruction Target Opcode 47h

Dword Length 09h

181

Instruction Target Opcode 48h

Dword Length 0Ah

183

BLT Engine Instruction Definitions

12.3.1. BR00-BLT Opcode and Control

185

SolPat Rsvd Mono

187

12.3.3. BR02-Clip Rectangle Y1 Address

12.3.4. BR03-Clip Rectangle Y2 Address

12.3.5. BR04-Clip Rectangle X1

3128 Reserved. Must be Zero 2716

12.3.6. BR05-Setup Expansion Background Color

12.3.7. BR06-Setup Expansion Foreground Color

12.3.8. BR07-Setup Color Pattern Address

12.3.9. BR08-Destination X1

12.3.10. BR09-Destination Address and Destination Y1 Address

12.3.11. BR10-Destination Y2 Address

Source Pitch Offset or Monochrome Source Quadwords

12.3.13. BR12-Source Address

12.3.14. BR13-BLT Raster OP, Control, and Destination Pitch

Increment/Decrement Select

Source Select Mode

Dynamic Color Depth

12.3.15. BR14-Destination Width & Height

12.3.16. BR15-Color Pattern Address

12.3.18. BR17-Pattern Expansion Foreground Color

3124 Reserved. Must be Zero 230

12.3.20. BR19-Source Expansion Foreground Color

SSLADD-Source Scan Line Address

DSLH-Destination Scan Line Height

DSLRADD-Destination Scan Line Read Address

204

Rendering Engine Instructions

Gfxprimitive

Axis Aligned Rectangles

Primitive Winding Order

Primitive Rendering Instruction Format

Position Mask

Bias

Variable Length Vertex Formats for Rendering Instructions

Vertex Attribute Comments

Gfxvertex

Gfxrenderstatevertexformat

Gfxblock

Rendering Block 1Eh

Block Type

Block Pattern Format

Prediction Type

DWord Bits

Vertical Motion Vector Precision 00 = 1/2 pixel

212

Precision Format Range

Non-pipelined State Variables

Motion Vector Format

Gfxrenderstatemaptexels

Gfxrenderstatemapcoordsets

Update Coordinate Set Index The valid range is

Normalized Coordinate Set Mask 0 = Do not update 1 = Update

Opcode 1h

Normalized Coordinate Set

Gfxrenderstatemapinfo

Discrete Integrated Base Utilize Fence Tiled Surface

Walk

3DstateMW 1Dh

Dwordlength 2h

Reserved 0h

Surface Format

Color Space Conversion Enable

1511

221

Gfxrenderstatemapfilter

Reserved 00h Mip Mode Filter Valid values are

Opcode 2h

Gfxrenderstatemaplodlimits

Opcode 3h

Opcode 4h

Texture LOD Dither Weight Mask 0 = Do not update 1 = Update

Gfxrenderstatemaplodcontrol

Opcode 82h

Gfxrenderstatemappaletteload

3DStateMWNPNon-pipelined 1Dh

Gfxrenderstatemapcolorblendstages

Blend Equation Description

Update Blending Stage Index The valid range is

3DState24 00h

Write result to Current Register or Accumulator Select

Replicate Arg1 Alpha to Color Channels

Invert Color Arg2

Gfxrenderstatemapalphablendstages

Invert Alpha Arg2

3DState24 01h

Invert Alpha Arg1

Gfxrenderstatecolorfactor

Instruction 1h

Kill Pixel Mode

Gfxrenderstatecolorchromakey

KeyedPixelControl

KeyedPixelControl Write Mask 0 = Do not update 1 = Update

Instruction 2h

Monochrome Specular Full Color RGB

Gfxrenderstatesrcdstblendmono

No Specular

236

Opcode Source / Destination Blend State

3DState24NP Non-pipelined 14h

Alpha Reference State Mask 1 = Update 0 = Do Not Update

Gfxrenderstatezbiasalphafuncref

Gfxrenderstatelinewidthcullshade Mode

Alpha Shade Mode State Mask 1 = Update 0 = Do Not Update

Specular Shade Mode State Mask 1 = Update 0 = Do Not Update

Color Shade Mode State Mask 1 = Update 0 = Do Not Update

2824 3DState24 02h

Alpha Setup Enable Enable Mask 1 = Update 0 = Do Not Update

Color Index Key Enable Mask 1 = Update 0 = Do Not Update

Specular Enable State Mask 1 = Update 0 = Do Not Update

GFXRENDERSTATEBOOLEANENA1

Specular Dither Enable Mask 1 = Update 0 = Do Not Update

Frame Buffer Write Enable Mask 1 = Update 0 = Do Not Update

Buffer Write Enable Mask 1 = Update 0 = Do Not Update

GFXRENDERSTATEBOOLEANENA2

3DState24NP Non-pipelined 15h

Gfxrenderstatefogcolor

Gfxrenderstatedrawingrectangleinfo

3DStateMWNP Non-pipelined 1Dh

Opcode 80h

Gfxrenderstatescissorenable

Scissor Rectangle Enable Mask 1 = Update 0 = Do Not Update

3DState16NP Non-pipelined 1Ch

Opcode 10h

Gfxrenderstatescissorrectangleinfo

Opcode 81h

Stipple Pattern

Stipple Pattern

Opcode 83h

Gfxrenderstateantialiasing

Gfxrenderstateprovokingvtxpixelization Rule

Vertex Sequence

Small Triangle Filter Enable Mask

Pixelization Rule Mask

Gfxrenderstatedestbuffervariables

Opcode 85h

Dest Buffer Format 0h = Any 8-bit Surface

Programming Hints/Rules

Drawing and Scissor Rectangles

Color Calculator

255

256

Clock Control Registers

Programming Notes

DCLK0D-Display Clock 0 Divisor Register

Example Programming Sequence DCLK2

DCLK1D-Display Clock 1 Divisor Register

DCLK2D-Display Clock 2 Divisor Register

LCDCLKD-LCD Clock Divisor Register

Reserved VCO Loop Divide LCD Clock

DCLK0DS-Display & LCD Clock Divisor Select Register

Post Divisor Select LCD Clock

Post Divisor Select clock

VCO Loop Divide clock

PWRCLKC-Power Management and Miscellaneous Clock Control

Internal DAC Enable

Overlay Registers

Register/Instruction Category

Comment

15.1. OV0ADD-Overlay 0 Register Update Address Register

Updating Register Values

DOV0STA-Display/Overlay 0 Status Register

Gamma Correction

GAMC50-Gamma Correction Registers

Red

Green Blue

Mathematical Gamma Correction For Overlay

Three times

Gamma Correction Theory Of Operation

Latch Address

Gamma Hardware Implementation

Memory Offset Registers

Overlay Buffer Pointer Registers

OBUF0Y-Overlay Buffer 0 Y Pointer Register

Format Alignment

OBUF1Y-Overlay Buffer 1 Y Pointer Register

OBUF0U-Overlay Buffer 0 U Pointer Register

Bit Descriptiont

OBUF0V-Overlay Buffer 0 V Pointer Register

OBUF1U-Overlay Buffer 1 U Pointer Register

15.4.2.1. OV0STRIDE-Overlay 0 Stride Register

Overlay Stride Registers

OBUF1V-Overlay Buffer 1 V Pointer Register

Overlay Initial Phase Registers

YRGBVPH-Y/RGB Vertical Phase Register

UVVPH-UV Vertical Phase Register

HORZPH-Horizontal Phase Register

INITPH-Initial Phase Register

DWINSZ-Destination Window Size Register

Overlay Destination Window Position/Size Registers

DWINPOS-Destination Window Position Register

Overlay Source Size Registers

SWID-Source Width Register

SWIDQW-Source Width In QWords Register

SHEIGHT-Source Height Register

Overlay Scale Factor Registers

YRGBSCALE-Y/RGB Scale Factor Register

UVSCALE-UV Scale Factor Register

15.4.7.2. OV0CLRC1-Overlay 0 Color Correction 1 Register

Overlay Color Correction Registers

15.4.7.1. OV0CLRC0-Overlay 0 Color Correction 0 Register

Overlay Destination Color Key Registers

DCLRKV-Destination Color Key Value Register

DCLRKM-Destination Color Key Mask Register

Destination Constant Alpha Blend Enable

Always Constant Alpha Blend Enable

Overlay Source Color Key Registers

SCLRKVH-Source Color Key Value High Register

SCLRKVL-Source Color Key Value Low Register

SCLRKM-Source Color Key Mask Register

Source Constant Alpha Blend Enable

Overlay Configuration Registers

15.4.10.1. OV0CONF-Overlay Configuration Register

15.4.11. OV0CMD-Overlay Command Register

Vertical Chrominance Filter. Vertical Chrominance Filter

Vertical Luminance Filter. Vertical Luminance Filter

Automatic flipping

Manual flip command

Source Format

297

Overlay Alpha Blend Window Position/Size Registers

AWINPOS-Alpha Blend Window Position Register

Overlay Flip Instruction

AWINSZ-Alpha Blend Window Size Register

300

FENCE-Graphics Memory Fence Table Registers

Instruction, Memory, and Interrupt Control Registers

Instruction Control Registers

Reserved for address bits 31 downto

Tile walk

Fence size

Fence Pitch

PGTBLCTL-Page Table Control Register

Normal Invalidation Mechanism

PGTBLER-Page Table Error Register

Error Type

PGTBLERRMSK-Page Table Error Mask Register

Buffer Unit Page Table Error Mask

Command Streamer DMA Page Table Error Mask

Overlay Page Table Error Mask

Display Page Table Error Mask

RINGBUF-Ring Buffer Registers

Intel 810 Chipset and Intel815 Chipset Errata

Reserved

Ring Buffer Valid

HWSPGA-Hardware Status Page Address Register

DWord Description Offset

IPEIR-Instruction Parser Error Identification Register debug

IPEHR-Instruction Parser Error Header Register debug

This read only register reports engine done signals

INSTDONE-Instruction Stream Interface Done Register

NOPID-NOP Identification Register

INSTPM-Instruction Parser Mode Register

Disable State Variable Updates

INSTPS-Instruction Parser State Register debug

Cscpr State Machine Command Parser

BBPPTR-Batch Buffer Parser Pointer Register debug

ABBSTR-Active Batch Buffer Start Address Register debug

Current DMA Address Reserved User of the DMA Engine

ABBEND-Active Batch Buffer End Address Register debug

DMAFADD-DMA Engine Fetch Address debug

MEMMODE-Memory Interface Mode Register debug

Reserved Host Graphics Prefetch Mode

Graphics Address Translation Mode

Instruction Fifo Debug Mode

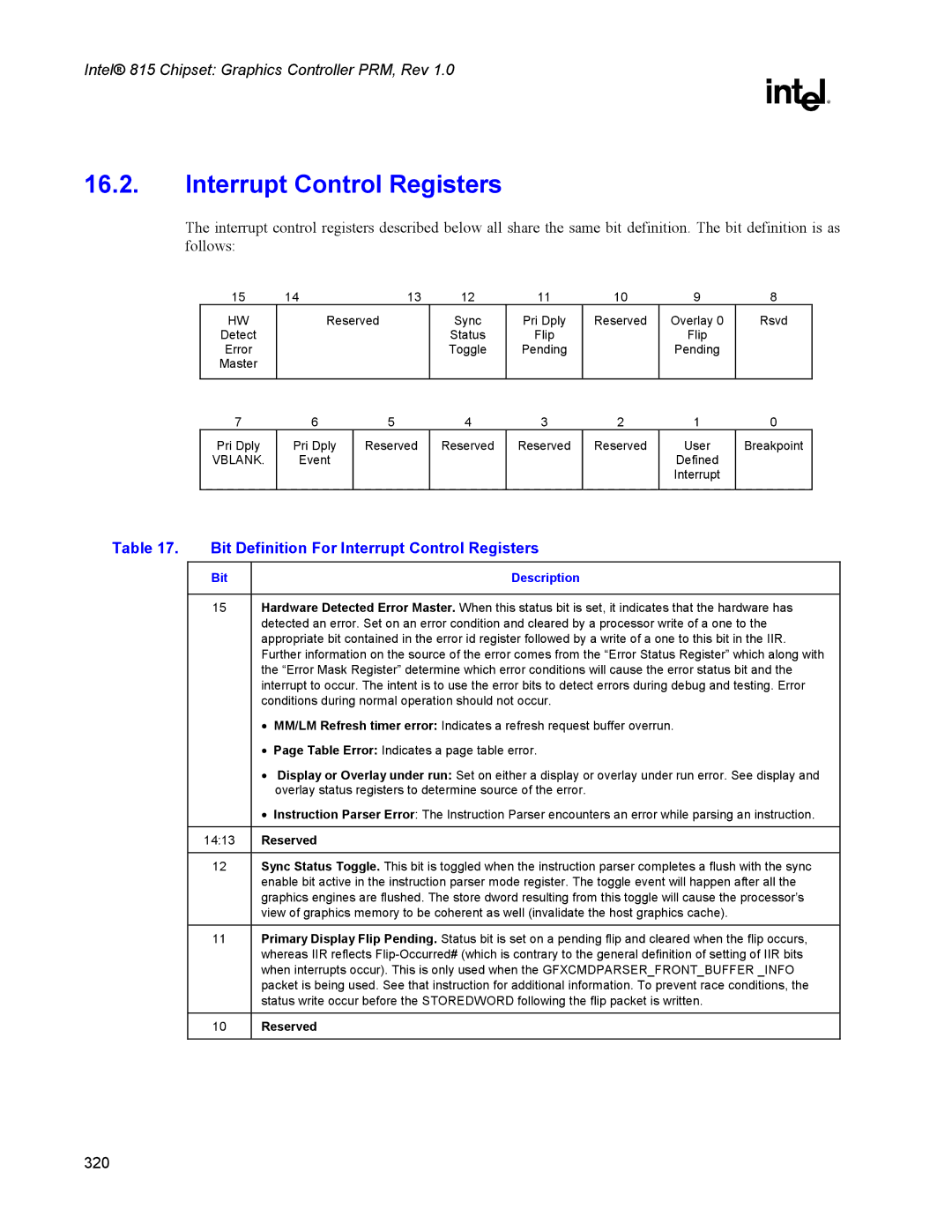

Interrupt Control Registers

Bit Definition For Interrupt Control Registers

321

HWSTAM-Hardware Status Mask Register

IER-Interrupt Enable Register

Interrupt Enables. See Table

IIR-Interrupt Identity Register

Interrupt Identity. See. Table

IMR-Interrupt Mask Register

Interrupt Mask Bits. See. Table

ISR-Interrupt Status Register

Error Identity, Mask and Status Registers

Table Error handling in Intel 815 Chipset

Resetting the Page Table Error

Table Error

EIR-Error Identity Register

EMR-Error Mask Register

ESR-Error Status Register

Display Interface Control

FWBLC-FIFO Watermark and Burst Length Control

332

LCD / TV-Out Register Description

HTOTAL-Horizontal Total Register

HBLANK-Horizontal Blank Register

HSYNC-Horizontal Sync Register

VTOTAL-Vertical Total Register

VBLANK-Vertical Blank Register

VSYNC-Vertical Sync Register

Sync Polarity Control

LCD / TV-Out Enable

LCDTVC-LCD/TV-Out Control Register

FP Vesa VGA Mode

FP / 740 Data Ordering

Fpvsync Control

Fphsync Control

Border Enable

Fphsync Output Control

Active Data Order

Active Data Polarity

OVRACT-Overlay Active Register

BCLRPAT- Border Color Pattern Register

Local Memory Interface

DRT-DRAM Row Type

Reserved Paging Mode Control PMC

Bit RAS#-to-CAS# delay t RCD

DRAMCL-DRAM Control Low

Bit RAS# act. To precharge t RAS Refresh to RAS# act. t RC

DRAMCH-DRAM Control High

346

HSYNC/VSYNC Control1916

19. I/O Control Registers

HVSYNC-HSYNC/VSYNC Control Register

Gpio Registers

GPIOAGeneral Purpose I/O Control Register a

Value .bit

GPIOBGeneral Purpose I/O Control Register B

351

352

Line Counter for Display

Display And Cursor Registers

DISPSL-Display Scan Line Count

DISPSLC-Display Scan Line Count Range Compare

Inclusive / Exclusive

PIXCONF-Pixel Pipeline Configuration

Reserved Display path Graphics Gamma Enable. See note

Overlay path Gamma Enable. See note

Pixel Pipeline Control

Display Color Mode

Bit DAC Enable

Enable Extended Status Read Mode

CRT Overscan Color

GUI Mode

Transition from VGA modes to hires mode or opposite

BLTCNTL-BLT Control

SWF13-Software Flag Registers

DPLYBASE-Display Base Address Register

Reserved Flat Panel Hot Plug Detect Enable

Vertical Sync Status Enable

Display Line Compare Enable

DPLYSTAS-Display Status Select Register

Vertical Blank Enable

Overlay Registers Upated Enable

Overlay Registers Updated Status

Vertical Sync Status

Reserved Cursor Coordinate System Origin Select

Hardware Cursor

CURCNTR-Cursor Control Register

CURBASE-Cursor Base Address Register

CURPOS-Cursor Position Register

Appendix a Mode Parameters

Parameters for Screen Resolution/Refresh Rate 320x20070Hz =

Parameters for Screen Resolution/Refresh Rate 320x24070Hz =

Parameters for Screen Resolution/Refresh Rate 352X48070Hz =

Parameters for Screen Resolution/Refresh Rate 352X57670Hz =

Parameters for Screen Resolution/Refresh Rate 400x30070Hz =

Parameters for Screen Resolution/Refresh Rate 512X38470Hz =

Parameters for Screen Resolution/Refresh Rate 640x35085Hz =

Parameters for Screen Resolution/Refresh Rate 640x40070Hz =

Parameters for Screen Resolution/Refresh Rate 640x40085Hz =

Parameters for Screen Resolution/Refresh Rate 640x48060Hz =

Parameters for Screen Resolution/Refresh Rate 640x48070Hz =

Parameters for Screen Resolution/Refresh Rate 640x48072Hz =

Parameters for Screen Resolution/Refresh Rate 640x48075Hz =

Parameters for Screen Resolution/Refresh Rate 640x48085Hz =

Parameters for Screen Resolution/Refresh Rate 720x40085Hz =

Parameters for Screen Resolution/Refresh Rate 720x48060Hz =

Parameters for Screen Resolution/Refresh Rate 720x48075Hz =

Parameters for Screen Resolution/Refresh Rate 720x48085Hz =

Parameters for Screen Resolution/Refresh Rate 720x57660Hz =

Parameters for Screen Resolution/Refresh Rate 720x57675Hz =

Parameters for Screen Resolution/Refresh Rate 720x57685Hz =

Parameters for Screen Resolution/Refresh Rate 800x60056Hz =

Parameters for Screen Resolution/Refresh Rate 800x60060Hz =

Parameters for Screen Resolution/Refresh Rate 800x60070Hz =

Parameters for Screen Resolution/Refresh Rate 800x60072Hz =

Parameters for Screen Resolution/Refresh Rate 800x60075Hz =

Parameters for Screen Resolution/Refresh Rate 800x60085Hz =

Parameters for Screen Resolution/Refresh Rate 854X48060Hz =

Parameters for Screen Resolution/Refresh Rate 854X48075Hz =

Parameters for Screen Resolution/Refresh Rate 854X48085Hz =

394

395

396

397

398

399

400

401

402

403

404

405

406

407

408

409

410

411

412

413

414

415

416

417

418

419

420

421

422

Intel around the world