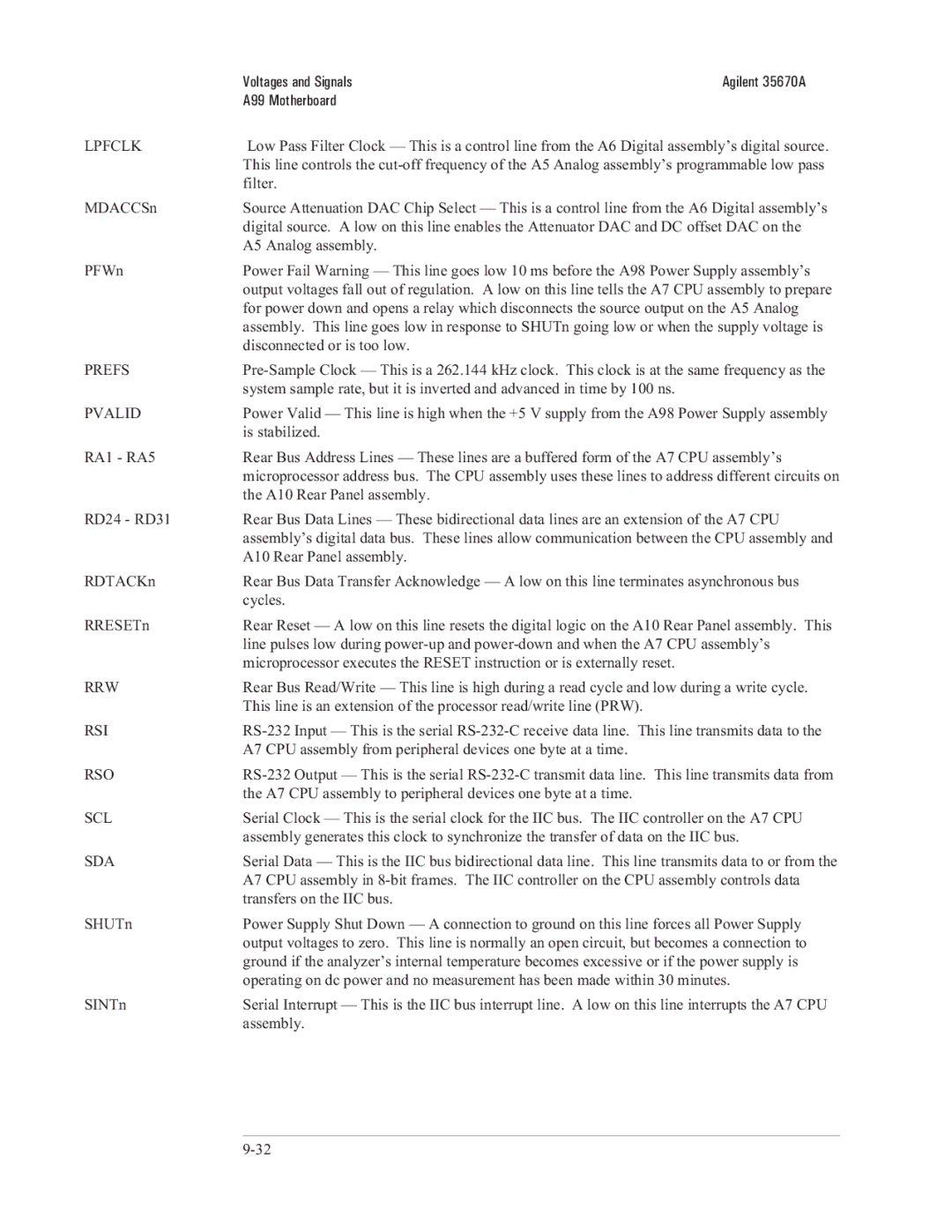

| Voltages and Signals | Agilent 35670A |

| A99 Motherboard |

|

LPFCLK | Low Pass Filter Clock — This is a control line from the A6 Digital assembly’s digital source. | |

| This line controls the | |

| filter. |

|

MDACCSn | Source Attenuation DAC Chip Select — This is a control line from the A6 Digital assembly’s | |

| digital source. A low on this line enables the Attenuator DAC and DC offset DAC on the | |

| A5 Analog assembly. |

|

PFWn | Power Fail Warning — This line goes low 10 ms before the A98 Power Supply assembly’s | |

| output voltages fall out of regulation. A low on this line tells the A7 CPU assembly to prepare | |

| for power down and opens a relay which disconnects the source output on the A5 Analog | |

| assembly. This line goes low in response to SHUTn going low or when the supply voltage is | |

| disconnected or is too low. |

|

PREFS | ||

| system sample rate, but it is inverted and advanced in time by 100 ns. |

|

PVALID | Power Valid — This line is high when the +5 V supply from the A98 Power Supply assembly | |

| is stabilized. |

|

RA1 - RA5 | Rear Bus Address Lines — These lines are a buffered form of the A7 CPU assembly’s | |

| microprocessor address bus. The CPU assembly uses these lines to address different circuits on | |

| the A10 Rear Panel assembly. |

|

RD24 - RD31 | Rear Bus Data Lines — These bidirectional data lines are an extension of the A7 CPU | |

| assembly’s digital data bus. These lines allow communication between the CPU assembly and | |

| A10 Rear Panel assembly. |

|

RDTACKn | Rear Bus Data Transfer Acknowledge — A low on this line terminates asynchronous bus | |

| cycles. |

|

RRESETn | Rear Reset — A low on this line resets the digital logic on the A10 Rear Panel assembly. This | |

| line pulses low during | |

| microprocessor executes the RESET instruction or is externally reset. |

|

RRW | Rear Bus Read/Write — This line is high during a read cycle and low during a write cycle. | |

| This line is an extension of the processor read/write line (PRW). |

|

RSI | ||

| A7 CPU assembly from peripheral devices one byte at a time. |

|

RSO | ||

| the A7 CPU assembly to peripheral devices one byte at a time. |

|

SCL | Serial Clock — This is the serial clock for the IIC bus. The IIC controller on the A7 CPU | |

| assembly generates this clock to synchronize the transfer of data on the IIC bus. | |

SDA | Serial Data — This is the IIC bus bidirectional data line. This line transmits data to or from the | |

| A7 CPU assembly in | |

| transfers on the IIC bus. |

|

SHUTn | Power Supply Shut Down — A connection to ground on this line forces all Power Supply | |

| output voltages to zero. This line is normally an open circuit, but becomes a connection to | |

| ground if the analyzer’s internal temperature becomes excessive or if the power supply is | |

| operating on dc power and no measurement has been made within 30 minutes. | |

SINTn | Serial Interrupt — This is the IIC bus interrupt line. A low on this line interrupts the A7 CPU | |

| assembly. |

|