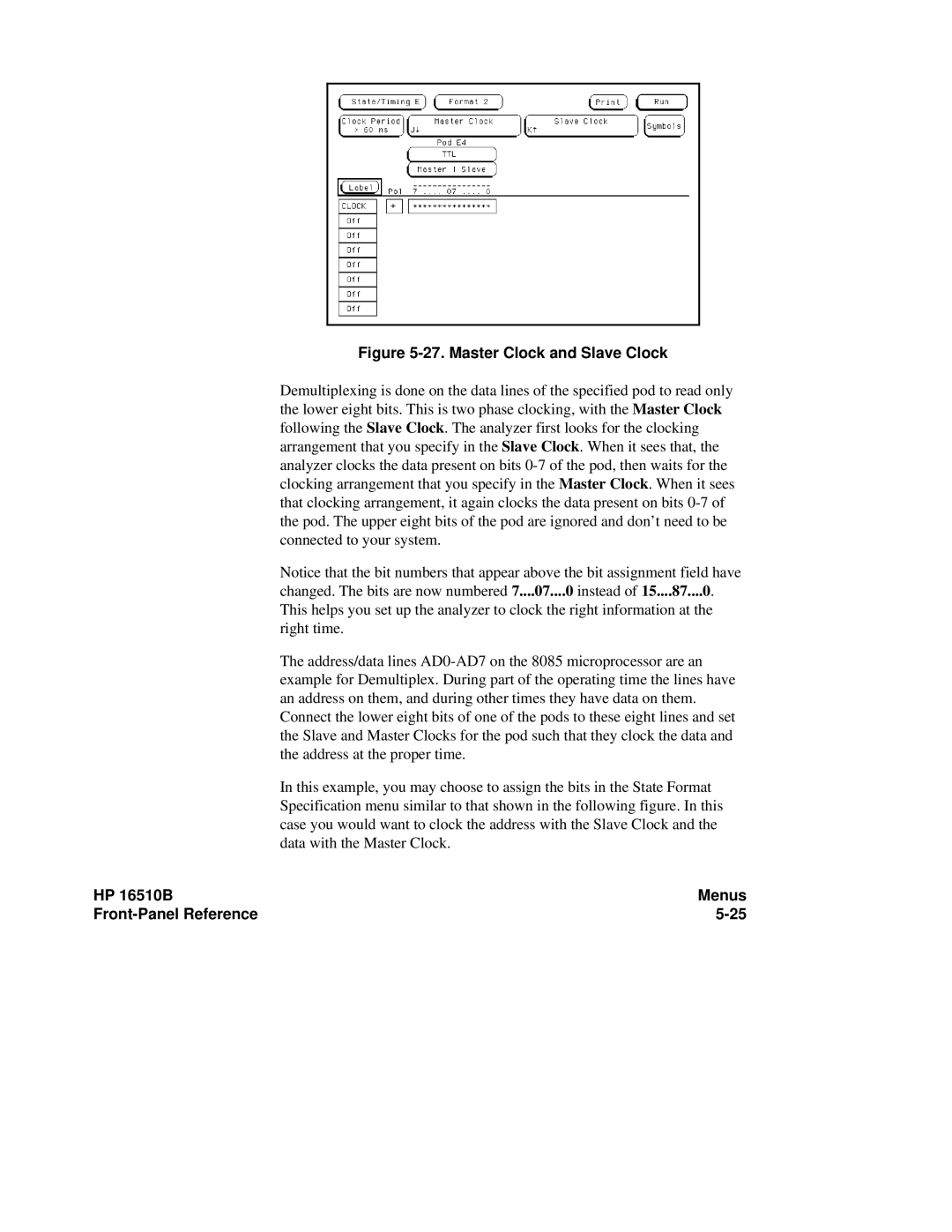

Figure 5-27. Master Clock and Slave Clock

Demultiplexing is done on the data lines of the specified pod to read only the lower eight bits. This is two phase clocking, with the Master Clock following the Slave Clock. The analyzer first looks for the clocking arrangement that you specify in the Slave Clock. When it sees that, the analyzer clocks the data present on bits

Notice that the bit numbers that appear above the bit assignment field have changed. The bits are now numbered 7....07....0 instead of 15....87....0.

This helps you set up the analyzer to clock the right information at the right time.

The address/data lines

In this example, you may choose to assign the bits in the State Format Specification menu similar to that shown in the following figure. In this case you would want to clock the address with the Slave Clock and the data with the Master Clock.

HP 16510B | Menus |