Development System Reference Guide

Development System Reference Guide

About This Guide

Guide Contents

Preface About This Guide

Typographical

Additional Resources

Conventions

Preface About This Guide Convention Meaning or Use Example

Online Document

Allow block blockname

Loc1 loc2 ... locn

Table of Contents

Tcl

PARTGen

MAP

Logical Design Rule Check

NGDBuild

PAR

Physical Design Rule Check

Development System Reference Guide

PIN2UCF

XPower

Trace Output Files

Trace

BitGen

Speedprint

BSDLAnno

IBISWriter

PROMGen

TAEngine

CPLDfit

Tsim

NetGen

Hprep6

Development System Reference Guide

Xflow

EDIF2NGD, and NGDBuild

Data2MEM

Introduction

Command Line Program Overview

1Command Line Programs in the Design Flow Design Flow Step

Command Line Options

Command Line Syntax

Execute Commands File

Introduction

Help

Command Line Options

Symbol Description

Intstyle Integration Style

Introduction Symbol Description

Programname -harchitecturename

Programname -h filename

Part Number

2Part Number Examples Specification

Introduction 2Part Number Examples Specification

Invoking Command Line Programs

Design Flow Overview

Design Flow

Xilinx Design Flow

Design Flow

2Xilinx Software Design Flow FPGAs

Design Flow Overview

3Xilinx Software Design Flow CPLDs

Design Entry and Synthesis

Design Entry and Synthesis

Hierarchical Design

Core Generator Tool FPGAs Only

Schematic Entry Overview

Library Elements

Functional Simulation

HDL Entry and Synthesis

Constraints

Mapping Constraints FPGAs Only

Timing Specifications

Block Placement

Design Implementation

Netlist Translation Programs

5Design Implementation Flow FPGAs

Design Implementation

6Design Implementation Flow CPLDs

Bitstream Generation FPGAs Only

Mapping FPGAs Only

Placing and Routing FPGAs Only

1Verification Tools Verification Type

Design Verification

7Three Verification Methods of the Design Flow FPGAs

Design Verification

Back-Annotation

Simulation

9Back-Annotation Flow for FPGAs

NetGen

Schematic-Based Simulation

Timing Simulation

HDL-Based Simulation

2Five Simulation Points in HDL Design Flow UniSim SimPrim

11Simulation Points for HDL Designs

Static Timing Analysis FPGAs Only

Design Rule Checker FPGAs Only

In-Circuit Verification

Xilinx Design Download Cables

Probe

Fpga Design Tips

3Global Clock Resources Fpga Family Number Destination Pins

Design Size and Performance

Global Clock Distribution

12 Gated Clock

Data Feedback and Clock Enable

Counters

13Synchronous Design Using Data Feedback

Q0. . . .Q7Q8. . . .Q15

Other Synchronous Design Considerations

Q0. . . .Q7 Q8. . . .Q15

Tcl Overview

Tcl

Xilinx Tcl Shell

Accessing Help

Tcl Fundamentals

Tcl Fundamentals

Xilinx Namespace

Xilinx Tcl Commands

1Xilinx Tcl Commands for General Usage Subcommands

Project create and manage projects

Partition support design preservation

Tcl Commands for General Usage

2Xilinx Tcl Commands for Advanced Scripting Subcommands

Delete delete a partition

Tcl Commands for General Usage

Get get partition properties

Partition delete /stopwatch/Instdcm1

Partition new /stopwatch/Instdcm1

New create a new partition

Partition get /stopwatch/Instdcm1 preserve

Partition properties

Properties list available partition properties

Rerun force partition synthesis and implementation

Set set partition preserve property

4Process Tasks

Process run and manage project processes

Run run process task

Project create and manage projects

Clean remove system-generated project files

Project clean

Get get project properties

Close close the ISE project

Getprocesses get project processes

Project close

Open open an ISE project

New create a new ISE project

Project getprocesses -instance Instdcm1

Project new watchver.ise

Project properties -process all

Properties list project properties

Set set project properties, values, and options

Set family set device family

Set device set device

Project set Map Effort Level high

Project set device xc2vp2

Set speed set device speed

Set package set device package

Project set family Virtex2p

Project set package fg256

Set top set the top-level module/entity

Timinganalysis generate timing analysis reports

Delete delete timing analysis

Project set speed

Disablecpt disable components for path tracing control

Disableconstraints disable timing constraints

Timinganalysis enableconstraints

Enablecpt enable components for path tracing control

Stopwatchtiming TSclk=PERIOD TIMEGROUP\sclk\

Ns High 50.00000%

Regsrclk ureg1 ureg2 ureg3

Timinganalysis enablecpt stopwatchtiming

Get get analysis property

Ascii

New new timing analysis

Timinganalysis reset stopwatchtiming

Reset reset path filters and constraints

Run run analysis

Saveas save analysis report

Setconstraint set constraint for custom analysis

Set set analysis properties

Timinganalysis set stopwatchtiming

Analysisspeed

Period 13 sclk

Setendpoints set source and destination endpoints

Timinganalysis setconstraint stopwatchtiming

Setfilter set filter for analysis

Setquery set up net or timegroup report

Timinganalysis setfilter stopwatchtiming nets

Exclude uregnet1 uregnet2 uregnet3

Xfile manage project files

Showsettings generate settings report

Add add file to project

Example

Remove remove file from project

Get get project file properties

Xfile add *.vhd /mysource/mysubdir timing.ucf

Xfile get timestamp stopwatch.vhd

Collection create and manage a collection

Tcl Commands for Advanced Scripting

Appendto add objects to a collection

Xfile remove stopwatch.vhd

Copy copy a collection

Tcl Commands for Advanced Scripting

Set colVar1 search * -type instance

Set colVar2 $colVar1

Set colVar2 collection copy $colVar1

Equal compare two collections

Set colVar2 search /top/T* -type instance

Collection equal $colVar1 $colVar2

Get get collection property

Foreach iterate over elements in a collection

Properties list available collection properties

Index extract a collection object

Set item collection index $colVar

Object name $item

Collection properties

Removefrom remove objects from a collection

Set set the property for all collections

Sizeof show the number of objects in a collection

Object get object information

Collection set displaytype true

Collection sizeof $colVar

Name name of the object

Get get object properties

Collection foreach obj $colVar set objProps

Object properties $obj foreach prop $objProps

Set colVar search * -type partition

Properties list object properties

Object name collection index $colVar

Object type collection index $colVar

Search search and return matching objects

Type type of object

Search /stopwatch -type instance

Project Properties and Options

6Project Properties Property Name Description

Option Name Synthesis Tool

Project Properties and Options

NGDBuild Options Option Name Implementation Tool

Option Name Implementation Tool

Tcl 10 PAR Options

Example Tcl Scripts

Example Tcl Scripts

Sample Tcl Script for General Usage

Tcl

Sample Tcl Script for Advanced Scripting

100

PARTGen Overview

PARTGen

PARTGen Syntax

Partgen options

PARTGen Output Files

PARTGen Input Files

PARTGen Options

Arch Print Information for Specified Architecture

PARTGen Options

Print a List of Devices, Packages, and Speeds

PARTGen Options

2s400e

Nopkgfile No Package File

Creates Package file and Partlist Files

Pname

Xcv400 Device V400bg432 Part

Creates Package and Partlist Files

Partlist File

Device Attributes

Header

Partlist File

Part architecture family partname diename packagefilename

Select RAM

PKG File

PKG File

Done

Logical DRC Overview

Logical Design Rule Check

Block Check

Logical DRC Checks

Net Check

Pad Check

Logical DRC Checks

Clock Buffer Check

Name Check

Primitive Pin Check

1Checked Primitive Pins NGD Primitive Pins Checked

NGDBuild Overview

NGDBuild

1NGDBuild Design Flow

Converting a Netlist to an NGD File

NGDBuild Input Files

NGDBuild Syntax

NGDBuild Syntax

Ngdbuild options designname ngdfile.ngd

120

NGDBuild Output Files

Add PADs to Top-Level Port Signals

NGDBuild Intermediate Files

NGDBuild Options

Bm Specify BMM Files

Aul Allow Unmatched LOCs

Dd Destination Directory

Ignore UCF File

Libraries to Search

Insertkeephierarchy

NGDBuild Options

Synopsys

Modular initial Initial Budgeting of Modular Design

Modular assemble Module Assembly

Modular assemble -pimpath pimdirectorypath

Usepimmodulename1 -usepimmodulename2

Nt Netlist Translation Type

Modular module Active Module Implementation

Modular module -active modulename

Pimcreate pimdirectory -ncd designnamerouted.ncd

Allow Unexpanded Blocks

Ignore LOC Constraints

Sd Search Specified Directory

Ur Read User Rules File

Uc User Constraints File

Verbose Report All Messages

Uc ucffile.ucf

128

MAP Overview

MAP

Map options infile.ngd pcffile.pcf

MAP Syntax

MAP Input Files

MAP Input Files

MAP Output Files

1Map Options and Architectures

MAP Options

Pack CLBs

Bp Map Slice Logic

MAP Options 1Map Options and Architectures

Cpackfactor

Detail Write Out Detailed MAP Report

Cm Cover Mode

Equivalentregisterremoval Remove Redundant Registers

Cm area speed balanced

Gm incremental Guide Mode incremental

Gm Guide Mode

Gf Guide NCD File

Globalopt Global Optimization

Ir Do Not Use RLOCs to Generate RPMs

Ignorekeephierarchy Ignore Keephierarchy Properties

Ise ISE Project File

Map to Input Functions

Output File Name

No logic replication

Olstdmedhigh

Ol Overall Effort Level

No Register Ordering

Pr Pack Registers in I/O

Registerduplication Duplicate Registers

Retiming Register Retiming During Global Optimization

Tx on off aggressive limit

Timing Timing-Driven Packing and Placement

Tx Transform Buses

Do Not Remove Unused Logic

MAP Process

Xe Extra Effort Level

MAP Process

Register Ordering

Data01 Addr02 Atod03 Dtoa04

Register Ordering

3Guided Mapping

Guided Mapping

Simulating Map Results

Simulating Map Results

4Logical Circuit Representation

MAP Report MRP File

MAP Report MRP File

148

Development System Reference Guide 149

Type Block GND Xstgnd

IOB

152

Halting MAP

Halting MAP

154

DRC Overview

Physical Design Rule Check

DRC Input File

DRC Syntax

DRC Output File

DRC Options

DRC Checks

DRC Checks

Report Incomplete Programming

DRC Errors and Warnings

Place and Route Overview

PAR

PAR Flow

Placing

PAR Process

Routing

Timing-driven PAR

Par -k previous.ncd reentrant.ncd pref.pcf

Command Line Examples

Par input.ncd output.ncd

Guided PAR

Guided PAR

PCI Cores

PAR Input Files

PAR Syntax

PAR Output Files

PAR Syntax

General Options Function Range Default

1Effort Level Options Function Range Default

PAR Options

Ol value for the router

Existingfile

PAR Options 2General Options Function Range Default

Guide Options Function Range Default

Gf Guide NCD File

Execute Commands File

Detailed Listing of Options

Intstyle Integration Style

Gm Guide Mode

Re-Entrant Routing

PAR Options

Number of PAR Iterations

Multi-Tasking Mode

Nopad No Pad

Ol Overall Effort Level

Power Power Aware PAR

No Placement

Pl Placer Effort Level

No Routing

Starting Placer Cost Table

Number of Results to Save

Ub Use Bonded I/Os

Overwrite Existing Files

PAR Reports

Performance Evaluation Mode

Xe Extra Effort Level

PAR Reports

Place and Route Report File

Development System Reference Guide 175

Ing score in parenthesis

Development System Reference Guide 177

Par -n 3 -pl high -rl std address.ncd output.dir

Multi Pass Place and Route Mppr

Placer effort levelrouter effort levelcost table number

Importing the PAD File Information

Select I/O Utilization and Usage Summary

Guide Reporting

Multi Pass Place and Route Mppr

Xplorer

Best Performance Mode

Xplorer

Timing Closure Mode

Xplorer Syntax

Xplorer Output Files

Xplorer Input Files

Xplorer Options

5Xplorer Options Function

Xplorer 5Xplorer Options Function

Xplorer Report

184

ReportGen Syntax

ReportGen

ReportGen Input Files

ReportGen Output Files

Option Usage Function

ReportGen Options

Isexflowsilent

Padfmt padcsvtxt

Turns Engine Overview

Turns Engine PAR Multi-Tasking Option

Turns Engine PAR Multi-Tasking Option

Par -m nodefilename -ol high -n 10 mydesign.ncd output.dir

Turns Engine Input Files

Turns Engine Syntax

System Requirements

Turns Engine Output Files

Limitations

Turns Engine Environment Variables

Rsh machinename

Debugging

Screen Output

Node Status JOB Time

Halting PAR

Halting PAR

196

XPower Overview

XPower

Files Used by XPower

XPower Syntax

Fpga Designs

Cpld Designs

VCD Data Entry

Using XPower

Using XPower

Other Methods of Data Entry

Rename Power Report

Limit

Ls List Supported Devices

Specify VCD file

Specify Settings XML Input File

Tb Turn On Time Based Reporting

Wx Write XML File

Standard Reports

Command Line Examples

Power Reports

Advanced Reports

Power Reports

Detailed Reports

204

PIN2UCF Overview

PIN2UCF

PIN2UCF Flow

PIN2UCF Input Files

PIN2UCF Syntax

PIN2UCF Output Files

PIN2UCF Syntax

PIN2UCF Scenarios

PIN2UCF Options

Write to a Report File

Outfile.ucf

Existing Pinlock section.

210

Trace Overview

Trace

Trace Input Files

Trace Syntax

Trce options design.ncd constraint.pcf

Trce -runmacro.xtm design.ncd constraint.pcf

Trace Output Files

Trace Output Files

Input files to Trace

Trace Options

Generate an Error Report

Advanced Analysis

Fastpaths Report Fastest Paths

Limit Timing Report

Nodatasheet No Data Sheet

Output Timing Report File Name

Trace Options

Change Speed

Run Run Timing Analyzer Macro

Skew Analyze Clock Skew for All Clocks

Skew

Report Uncovered Paths

Stamp Generates Stamp timing model files

Stampstampfile design.ncd

Ulimit

Generate a Verbose Report

Trace Command Line Examples

Xml XML Output File Name

Vlimit

Trace Reports

Trace Reports

Path Delay Constraints

Net Delay Constraints

Timing Verification with Trace

Net Skew Constraints

1Path Delay Constraint Terminology Definition

Clock Skew and Setup Checking

2Clock Skew Example

2Clock Skew and Setup Checking Terminology Terms Definition

3Clock Passing Through Multiple Buffers

Reporting with Trace

5Error reporting for failed timing constraints

Data Sheet Report

Development System Reference Guide 227

BSLOT0 D0S

Report Legend

Guaranteed Setup and Hold Reporting

Hold Times

Setup Times

Trce -o summary.twr ramb16s1.ncd

Summary Report Without a Physical Constraints File Specified

Trce -o summary1.twr ramb16s1.ncd clkperiod.pcf

Development System Reference Guide 233

Trce -e 3 ramb16s1.ncd clkperiod.pcf -o errorreport.twr

Development System Reference Guide 235

236

Development System Reference Guide 237

BUFGMUX.I0

Offset Constraints

Offset Constraints

Offset in Path Details

Offset in Constraint Examples

Offset in Header

Offset in Detailed Path Data

Offset in Detail Path Clock Path

Offset In with Phase Shifted Clock

Development System Reference Guide 243

Offset OUT Header

Offset OUT Constraint Examples

Offset OUT Detail Clock Path

Offset OUT Path Details

Offset OUT Detail Path Data

Period Constraints Examples

Period Constraints

Period Header

Period Constraints

Period Path

Period Path Details

Period Constraint with Phase

Period Path with Phase

Minimum Period Statistics

Halting Trace

Speedprint Overview

Speedprint

Speedprint Syntax

Specify Temperature

Speedprint Options

Min Display Minimum Speed Data

Speedprint Example Commands

Speedprint Example Commands

Command Description

Speedprint Example Reports

Lvttl Fast

BitGen Overview

BitGen

Loutfilename.ll Moutfilename.msk Boutfilename.rbt

BitGen Syntax

Option Output File

BitGen Input Files

BitGen Input Files

BitGen Output Files

Create Rawbits File

BitGen Options

Set Configuration

Bd Update Block Rams

Bitgen -goptionsetting design.ncd design.bit design.pcf

Do Not Run DRC

ActivateGCLK

ActiveReconfig

Binary

CclkPin

Compress

ConfigRate

DebugBitstream

DCIUpdateMode

DCMShutdown

DONEcycle

DisableBandgap

DonePin

DonePipe

Encrypt

DriveDone

Gclkdel0, Gclkdel1, Gclkdel2, Gclkdel3

GSRcycle

GTScycle

GWEcycle

HswapenPin

Key0, Key1, Key2, Key3, Key4, Key5

Keyseq0, Keyseq1, Keyseq2, Keyseq3, Keyseq4, Keyseq5

KeyFile

LCKcycle

M0Pin

M2Pin

M1Pin

Matchcycle

PartialGCLK

PartialLeft

PartialMask0, PartialMask1, PartialMask2

PartialRight

Persist

ProgPin

PowerdownPin

ReadBack

Security

StartCBC

SEURepair

StartKey

StartupClk

TdiPin

TckPin

TdoPin

TmsPin

UserID

No BIT File

UnusedPin

Generate a Mask File

Create a Logic Allocation File

Create a Partial Bit File

Overwrite Existing Output File

276

BSDLAnno Overview

BSDLAnno

BSDLAnno Input Files

BSDLAnno Syntax

BSDLAnno Output Files

BSDLAnno Options

Entity Declaration

BSDLAnno File Composition

Generic Parameter

BSDLAnno File Composition

Package Pin-Mapping

Logical Port Description

TAP Description

USE Statement

Scan Port Identification

Boundary Register Description

Bsdl File Modifications for Single-Ended Pins

Explanation

Modifications to the Designwarning Section

Boundary Scan Behavior in Xilinx Devices

Header Comments

BSDLAnno BSDLAnno version number

PROMGen Overview

PROMGen

PROMGen Input Files

PROMGen Syntax

PROMGen Output Files

Promgen options

PROMGen Options

Prom Format

Add BIT FIles

Load Prom File

File1.bit file2.bit

Template File

Prom Size

Load Upward

Ver Version

Bit Swapping in Prom Files

Enable Compression

PROMGen Examples

PROMGen Examples

292

IBISWriter Overview

IBISWriter

Ibiswriter options infile outfile.ibs

IBISWriter Syntax

IBISWriter Output Files

IBISWriter Input Files

IBISWriter Options

Set Reference Voltage

Architecture Option Value Description

Ml Multilingual Support

IBISWriter Options

Pin Generate Package Parasitics

298

CPLDfit Overview

CPLDfit

CPLDfit Output Files

CPLDfit Syntax

CPLDfit Input Files

CPLDfit Options

Iostd Specify I/O Standard

Inputs Number of Inputs to Use During Optimization

Keepio Prevent Optimization of Unused Inputs

Loc Keep Specified Location Constraints

Nogclkopt Disable Global Clock Optimization

Nofbnand Disable Use of Foldback Nands

Nogsropt Disable Global Set/Reset Optimization

Nogtsopt Disable Global Output-Enable Optimization

Optimize Optimize Logic for Density or Speed

Power Set Power Mode

Specify Xilinx Part

Pinfbk Use Pin Feedback

Unused Set Termination Mode of Unused I/Os

Terminate Set to Termination Mode

Slew Set Slew Rate

Wysiwyg Do Not Perform Optimization

306

Tsim Syntax

Tsim

Tsim Input Files

TAEngine Overview

TAEngine

1TAEngine Design Flow

TAEngine Syntax

Detail Detail Report

TAEngine Options

Iopath Trace Paths

Specify Output Filename

312

1Hprep6 Design Flow

Hprep6

Autosig Automatically Generate Signature

Hprep6 Syntax

Hprep6 Options

Specify Signature Value for Readback

Nopullup Disable Pullups

Produce ISC File

Tmv Specify Test Vector File

316

NetGen Overview

NetGen

1NetGen Output File Types Input Design File

NetGen

NetGen Functional Simulation Flow

NetGen Simulation Flow

NetGen Supported Flows

NetGen Simulation Flow

Syntax for NetGen Functional Simulation

NetGen Timing Simulation Flow

Output files for NetGen Functional Simulation

Ngcbuildoptions toplevelnetlistfile outputngcfile

NetGen Timing Simulation Flow

Syntax for NetGen Timing Simulation

Fpga Timing Simulation

Cpld Timing Simulation

Output files for Fpga Timing Simulation

Input files for Cpld Timing Simulation

Output files for Cpld Timing Simulation

Options for NetGen Simulation Flow

Module Simulation of Active Module

Insertppbuffers Insert Path Pulse Buffers

Mhf Multiple Hierarchical Files

Pcf PCF File

Ofmt Output Format

Change Speed

Sim Generate Simulation Netlist

Tm Top Module Name

Ti Top Instance Name

Tp Bring Out Global 3-State Net as Port

Insertglbl Insert glbl.v Module

Pf Generate PIN File

Ne No Name Escaping

Sdfanno Include $sdfannotate

Sdfpath Full Path to SDF File

VHDL-Specific Options for Functional and Timing Simulation

Xon Select Output Behavior for Timing Violations

NetGen Equivalence Checking Flow

NetGen Equivalence Checking Flow

Xon truefalse

Input files for NetGen Equivalence Checking

Syntax for NetGen Equivalence Checking

Ecn Equivalence Checking

Output files for NetGen Equivalence Checking

Options for NetGen Equivalence Checking Flow

Module Verification of Active Module

NetGen Static Timing Analysis Flow

NetGen Static Timing Analysis Flow

Ngm Design Correlation File

Syntax for NetGen Static Timing Analysis

Input files for Static Timing Analysis

Output files for Static Timing Analysis

Options for NetGen Static Timing Analysis Flow

336

Sta Generate Static Timing Analysis Netlist

Preserving and Writing Hierarchy Files

Preserving and Writing Hierarchy Files

Modulename .sim Modulename .ecn Modulename .sta

Hierarchy Information File

Dedicated Global Signals in Back-Annotation Simulation

Testbench File

Dedicated Global Signals in Back-Annotation Simulation

Global Signals in Verilog Netlist

Global Signals in Vhdl Netlist

340

Xflow Overview

Xflow

1XFLOW Design Flow

Xflow Syntax

Xflow Input Files

Xflow Input Files

Xflow Output Files

1XFLOW Output Files FPGAs and CPLDs

Xflow Output Files

2XFLOW Output Files FPGAs

Xflow Flow Types

Assemble Module Assembly

Xflow Flow Types

3XFLOW Output Files CPLDs

Configoptionfile

Config Create a BIT File for FPGAs

Ecn Create a File for Equivalence Checking

4Option Files for -assemble Flow Type Description

Fsim Create a File for Functional Simulation

Fit Fit a Cpld

5Option Files for -ecn Flow Type Description

6Option Files for -fit Flow Type Description

7Option Files for -fsim Flow Type

Implement Implement an Fpga

Xflow -p xc2v250fg256-5 -fsim genericverilog.opt testclk.v

Implement optionfile

Xflow Flow Types 8Option Files for -implement Flow Type

Initial Initial Budgeting of Modular Design

Initial budget.opt

Xflow -p xc2v250fg256-5 -initial budget.opt top.edf

9Option Files for -module Flow Type

Module Active Module Implementation

Moduleoptionfile -activemodulename

Sta Create a File for Static Timing Analysis

Mppr Multi-Pass Place and Route for FPGAs

10Option Files for -mppr Flow Type Description

11Option Files for -sta Flow Type Description

Synthoptionfile

Synth

Synthesis Types

Option Files for -synth Flow Types

Tsim Create a File for Timing Simulation

12Option Files for -synth Flow Type Description

Testclk.prj

13Option Files for -tsim Flow Type Description

Flow Files

Fpga

Flow File Format

Triggers

Flag Enabled Disabled

Exports

Reports

End Program programname

User Command Blocks

Option File Format

Xflow Option Files

Active Active Module

Xflow Options

Ed Copy Files to Export Directory

Specify a Global Variable

Change Output File Name

Norun Creates a Script File Only

Ooutputfilename

Xflow -implement balanced.opt -o newname testclk.edf

Rd Copy Report Files

Pd PIMs Directory

Pdpimdirectory

Rdreportdirectory

Running Xflow

Using Xflow Flow Types in Combination

Wd Specify a Working Directory

Running Smart Flow

Running Xflow

Using the SCR, BAT, or TCL File

Using the Xilxflowpath Environment Variable

366

Data2MEM Overview

Data2MEM

Data2MEM Input and Output Files

Data2MEM Syntax

Block RAM Memory Map .bmm files

Executable and Linkable Format .elf files

Memory .mem files

Debugging Information Format Dwarf .drf files

Bit .bit files

Verilog .v files

Data2MEM Options

1Data2MEM Command Line Options Description

Vhdl .vhd files

UCF .ucf files

Data2MEM Options 1Data2MEM Command Line Options

Pp filename

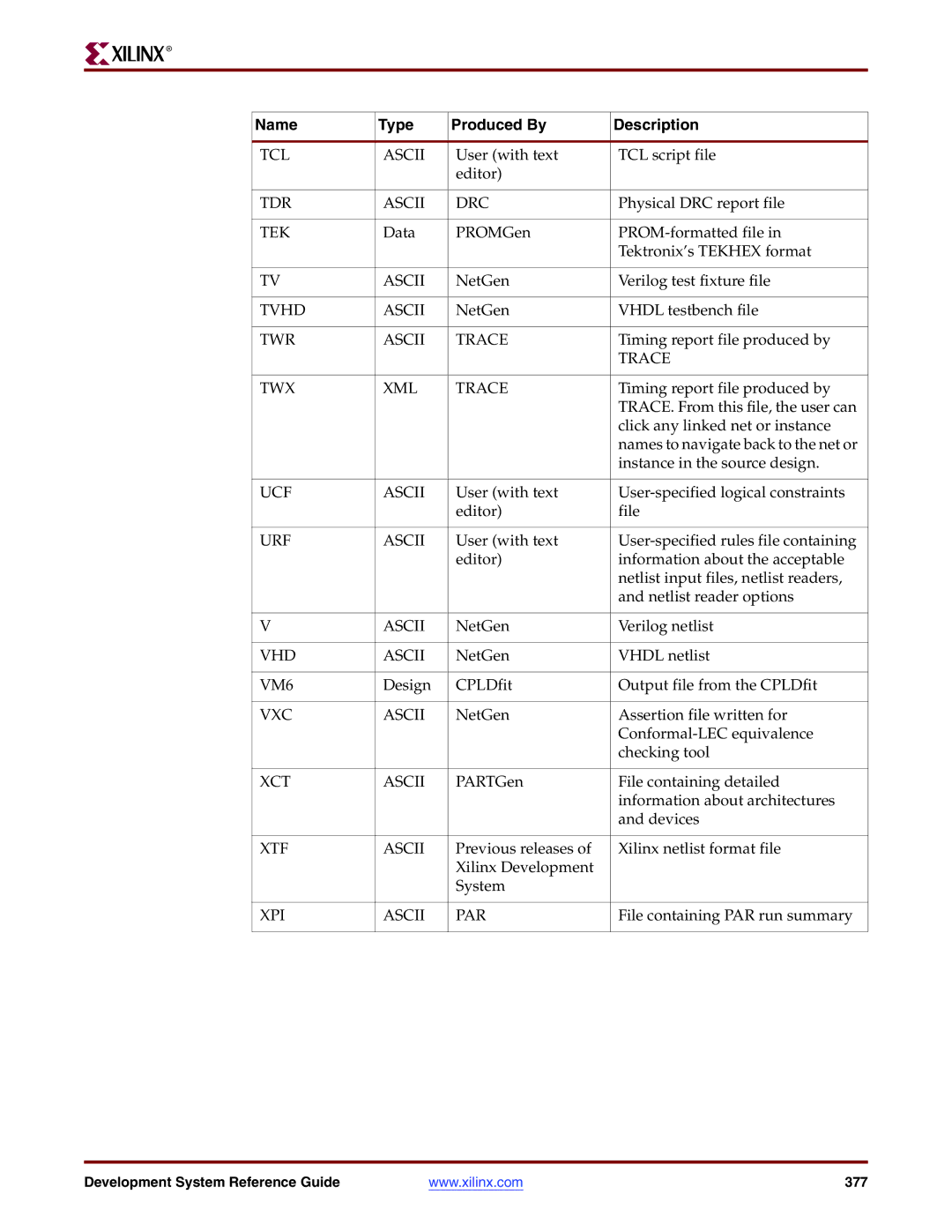

Name Type Produced By Description

Xilinx Development System Files

Appendix

MOD Ascii Trace

NKY

TCL Ascii

378

EDIF2NGD

EDIF2NGD, and NGDBuild

EDIF2NGD Design Flow

EDIF2NGD Input Files

EDIF2NGD Syntax

EDIF2NGD Output Files

Edif2ngd options ediffile ngofile

Aul Allow Unmatched LOCs

Add PADs to Top-Level Port Signals

EDIF2NGD Options

Part Number

Libraries to Search

Ignore LOC Constraints

Llibname

NGDBuild and the Netlist Readers

NGDBuild

NGDBuild

Bus Matching

Netlist Launcher Netlister

Bus Naming Conventions

Busnameindex DI3

Netlist Launcher Netlister

User Rules File

Netlist Launcher Rules Files

User Rules and System Rules

User Rules Format

Development System Reference Guide 389

Value Types in Key Statements

System Rules File

Example 1 Edfrule System Rule

Rules File Examples

Example 3 User Rule

Example 2 User Rule

NGDBuild File Names and Locations

NGDBuild File Names and Locations

Example 4 User Rule

394

Abel

Glossary

Asic

Block

Bitstream

Bonded

Boundary scan

CAE

Buft

Cmos

CLB

Contention

Configuration

Combinatorial logic

Compiler

Daisy chain

Cpld

Dangling bus

Dangling net

DSP

DRC

Edif

EDA

Fifo

Eprom

Fdsd

Fpga

Fmap

Gate array

Global Set/Reset net

Global buffers

Global 3-state net

Ibuf

HDL

IFD

Ieee

Jedec

LSB

MSB

NGM

NCD

PAL

PLD

PIM

RAM

Prom

RTL

ROM

RPM

Set/reset

SDF standard delay format

Signal

Startup symbol

TCL

Tsim

Trace

TTL

Vhdl

Wire

Vital

Xtclsh

422