Intel PXA255 Processor

Intel PXA255 Processor Developer’s Manual

Contents

Power Manager General Configuration Register Pcfr

Contents

Expansion Card Interface Timing Diagrams and Parameters

DMA

10-1

11-1

12.6

14.3

15.5

Figures

BitBurst-of-Eight ROM or Flash Read Timing Diagram MSC0RDF =

10-25

Tables

Clocks Manager Register Summary

Sxcnfg

10-6

10-8

12-26

15-7

Revision History

Date Revision Description

Xxiv

Intel XScale Microarchitecture Features

System Integration Features

Memory Controller

Clocks and Power Controllers

Universal Serial Bus USB Client

DMA Controller Dmac

LCD Controller

6 AC97 Controller

Inter-IC Sound I2S Controller

Synchronous Serial Protocol Controller Sspc

Inter-Integrated Circuit I2C Bus Interface Unit

Gpio

UARTs

OS Timers

Real-Time Clock RTC

Pulse-Width Modulator PWM

Interrupt Control

Introduction

System Architecture

Overview

Intel XScale Microarchitecture Implementation Options

Coprocessor 7 Register 4 Psfs Bit

Coprocessor 14 Register 6 and 7- Clock and Power Management

CPU Core Fault Register Bit Definitions

Coprocessor 14 Registers 0-3 Performance Monitoring

Coprocessor 15 Register 0 ID Register Definition

Coprocessor 15 Register 1 P-Bit

ID Bit Definitions

PXA255 Processor ID Values

ARM ID Jtag ID

Semaphores

I/O Ordering

Interrupts

Reset

Unit Sleep Mode Gpio Reset Watchdog Reset Hard Reset

USB

ICP

Internal Registers

Selecting Peripherals vs. General Purpose I/O

Power on Reset and Boot Operation

Power Management

Pin List

Processor Pin Types

Pin & Signal Descriptions for the PXA255 Processor Sheet 1

Pin Name Type Signal Descriptions Reset State Sleep State

Pin & Signal Descriptions for the PXA255 Processor Sheet 2

Pin & Signal Descriptions for the PXA255 Processor Sheet 3

Psktsel

Pin & Signal Descriptions for the PXA255 Processor Sheet 4

Pin & Signal Descriptions for the PXA255 Processor Sheet 5

Pin & Signal Descriptions for the PXA255 Processor Sheet 6

Pin & Signal Descriptions for the PXA255 Processor Sheet 7

Pin & Signal Descriptions for the PXA255 Processor Sheet 8

Bootsel

Rtcclk Icocz

Pwren

Pin & Signal Descriptions for the PXA255 Processor Sheet 9

Pin Description Notes Sheet 1

Memory Map

Pin Description Notes Sheet 2

Memory Map Part One From 0x80000000 to 0xFFFF Ffff

Memory Map Part Two From 0x00000000 to 0x7FFF Ffff

System Architecture Register Summary

Unit Address Register Symbol Register Description

System Architecture Register Address Summary Sheet 1

System Architecture Register Address Summary Sheet 2

System Architecture Register Address Summary Sheet 3

System Architecture Register Address Summary Sheet 4

System Architecture Register Address Summary Sheet 5

Unit

System Architecture Register Address Summary Sheet 6

System Architecture Register Address Summary Sheet 7

Unit Address

System Architecture Register Address Summary Sheet 8

System Architecture Register Address Summary Sheet 9

System Architecture Register Address Summary Sheet 10

System Architecture Register Address Summary Sheet 11

System Architecture Register Address Summary Sheet 12

Clocks and Power Manager

Clock Manager Introduction

Power Manager Introduction

Clock Manager

Retains Power in Sleep

PWM SSP

OST

Ficp I2C MMC

1 32.768 kHz Oscillator

Core Phase Locked Loop

2 3.6864 MHz Oscillator

4 95.85 MHz Peripheral Phase Locked Loop

5 147.46 MHz Peripheral Phase Locked Loop

Core PLL Output Frequencies for 3.6864 MHz Crystal

Sdram

Hardware Reset

Resets and Power Modes

Clock Gating

Watchdog Reset

Gpio Reset

Completing a Watchdog Reset

Invoking Gpio Reset

Behavior During Gpio Reset

Run Mode

Turbo Mode

Completing Gpio Reset

Entering Turbo Mode

Idle Mode

Behavior in Turbo Mode

Exiting Turbo Mode

Entering Idle Mode

Behavior in Idle Mode

Exiting Idle Mode

Frequency Change Sequence

Preparing for a Frequency Change Sequence

Invoking the Frequency Change Sequence

Behavior During the Frequency Change Sequence

8 33-MHz Idle Mode

Completing the Frequency Change Sequence

Entering 33-MHz Idle Mode

Behavior in 33-MHz Idle Mode

Exiting 33-MHz Idle Mode

Sleep Mode

Sleep Mode External Voltage Regulator Requirements

Preparing for Sleep Mode

Entering Sleep Mode

Clocks and Power Manager

Behavior in Sleep Mode

Exiting Sleep Mode

Clocks and Power Manager

Power Mode Summary

Power Mode Entry Sequence Table

Power Mode Exit Sequence Table Sheet 1

Idle

Power Mode Exit Sequence Table Sheet 2

Power Manager Registers

Power Mode Supply Source Module Turbo Run

Power Manager Control Register Pmcr

Pmcr Bit Definitions

Pmcr

Idae

Power Manager General Configuration Register Pcfr

Pcfr Bit Definitions

Pcfr

Opde

Power Manager Wake-Up Enable Register Pwer

Pwer Bit Definitions

Wertc

Pwer

Power Manager Rising-Edge Detect Enable Register Prer

10. Prer Bit Definitions

0x40F00010

Prer

Power Manager Falling-Edge Detect Enable Register Pfer

11. Pfer Bit Definitions

0x40F00014

Pfer

Power Manager Gpio Edge Detect Status Register Pedr

12. Pedr Bit Definitions

0x40F00018

Pedr

Power Manager Sleep Status Register Pssr

13. Pssr Bit Definitions Sheet 1

Pssr

RDH

Power Manager Scratch Pad Register Pspr

13. Pssr Bit Definitions Sheet 2

14. Pspr Bit Definitions

CPU VFS

Power Manager Fast Sleep Walk-up Configuration Register Pmfw

15. Pmfw Register Bitmap and Bit Definitions

16. PGSR0 Bit Definitions

17. PGSR1 Bit Definitions

PGSR0

SS9 SS8 SS7 SS6 SS5 SS4 SS3 SS2 SS1 SS0

Reset Controller Status Register Rcsr

Bit Reset 0x40F00028

18. PGSR2 Bit Definitions

PGSR2

Core Clock Configuration Register Cccr

Clocks Manager Registers

19. Rcsr Bit Definitions

Rcsr

20. Cccr Bit Definitions

0x41300000

Bit Reserved

Multiplier =

Clock Enable Register Cken

21. Cken Bit Definitions Sheet 1

Description I2S Unit Clock Enable

21. Cken Bit Definitions Sheet 2

CKEN8

CKEN5

Oscillator Configuration Register Oscc

Coprocessor 14 Clock and Power Management

22. Oscc Bit Definitions

23. Coprocessor 14 Clock and Power Management Summary

Core Clock Configuration Register Cclkcfg

24. Cclkcfg Bit Definitions

Power Mode Register Pwrmode

Power-On-Reset Considerations

Power Supply Connectivity

External Hardware Considerations

Clocks and Power Manager Register Summary

Driving the Crystal Pins from an External Clock Source

Power Manager Register Summary

Clocks Manager Register Locations

27. Power Manager Register Summary

General-Purpose I/O

Gpio Operation

General-Purpose I/O Block Diagram

Gpio Alternate Functions

Gpio Alternate Functions Sheet 1

Gpio Alternate Functions Sheet 2

MMCCS0 ALTFN1OUT

Gpio Alternate Functions Sheet 3

Mbgnt ALTFN1OUT

Gpio Alternate Functions Sheet 4

Gpio Register Definitions

Gpio Register Definitions Sheet 1

Gpio Pin-Level Registers GPLR0, GPLR1, GPLR2

Gpio Register Definitions Sheet 2

GPLR0 Bit Definitions

GPLR0

Gpio Pin Direction Registers GPDR0, GPDR1, GPDR2

GPLR1 Bit Definitions

GPLR2 Bit Definitions

GPLR1

GPDR1 Bit Definitions

GPDR0 Bit Definitions

GPDR2 Bit Definitions

GPSR0 Bit Definitions

10. GPSR1 Bit Definitions

GPSR0

PS9 PS8 PS7 PS6 PS5 PS4 PS3 PS2 PS1 PS0

12. GPCR0 Bit Definitions

11. GPSR2 Bit Definitions

13. GPCR1 Bit Definitions

GPCR2 Bit Definitions

GPCR2

16. GRER1 Bit Definitions

15. GRER0 Bit Definitions

17. GRER2 Bit Definitions

19. GFER1 Bit Definitions

18. GFER0 Bit Definitions

GFER2 Bit Definitions

21. GEDR0 Bit Definitions

Gpio Edge Detect Status Register GEDR0, GEDR1, GEDR2

22. GEDR1 Bit Definitions

GEDR2 Bit Definitions

GEDR2

24. GAFR0L Bit Definitions

25. GAFR0U Bit Definitions

GAFR0L

AF9 AF8 AF7 AF6 AF5 AF4 AF3 AF2 AF1 AF0

26. GAFR1L Bit Definitions

27. GAFR1U Bit Definitions

GAFR1L

GAFR1U

28. GAFR2L Bit Definitions

29. GAFR2U Bit Definitions

GAFR2L

GAFR2U

Interrupt Controller

Interrupt Controller Operation

Interrupt Controller Block Diagram

Interrupt Controller Register Definitions

Interrupt Controller Mask Register Icmr

Interrupt Controller Level Register Iclr

30. Icmr Bit Definitions

Icmr

31. Iclr Bit Definitions

Interrupt Controller Control Register Iccr

32. Iccr Bit Definitions

33. Icip Bit Definitions

34. Icfp Bit Definitions

Interrupt Controller Pending Register Icpr

35. Icpr Bit Definitions Sheet 1

Icpr

IS9 IS8

Network SSP Service Request Interrupt Pending

35. Icpr Bit Definitions Sheet 2

IS14 IS13 IS12 IS11 IS10

IS16

35. Icpr Bit Definitions Sheet 3

36. List of First-Level Interrupts Sheet 1

System Integration Unit

Bit Position Source Unit

Real-Time Clock Operation

Real-Time Clock RTC

36. List of First-Level Interrupts Sheet 2

RTC Register Definitions

RTC Trim Register Rttr

Rttr Bit Definitions

RTC Alarm Register Rtar

38. Rtar Bit Definitions

RTC Counter Register Rcnr

RTC Status Register Rtsr

39. Rcnr Bit Definitions

Rcnr

Oscillator Frequency Calibration

Trim Procedure

40. Rtsr Bit Definitions

Trim Example #1 Measured Value Has No Fractional Component

Rttr Value Calculations

Trim Example #2 Measured Value Has a Fractional Component

Operating System OS Timer

Maximum Error Calculation Versus RTC Accuracy

OS Timer Register Definitions

Watchdog Timer Operation

OS Timer Match Register 0-3 OSMRx

OS Timer Interrupt Enable Register Oier

41. OSMRx Bit Definitions

42. Oier Bit Definitions

OSMR3, OSMR2, OSMR1

OS Timer Watchdog Match Enable Register Ower

OS Timer Count Register Oscr

OS Timer Status Register Ossr

43. Ower Bit Definitions

0x40A00014 Bit Reset ? ? ? ? ? ? ? ? Bits

Pulse Width Modulator

Pulse Width Modulator Operation

Ossr Bit Definitions

PWMn Block Diagram

1.1 Interdependencies

Reset Sequence

Power Management Requirements

Register Descriptions

PWM Control Registers PWMCTRLn

PWM Duty Cycle Registers PWMDUTYn

46. PWMCTRLn Bit Definitions

0x40B00000

Prescale

PWM Period Control Register PWMPERVALn

47. PWMDUTYn Bit Definitions

PWMDUTY0, PWMDUTY1

Fdcycle Dcycle

48. PWMPERVALn Bit Definitions

Pulse Width Modulator Output Wave Example

0x40B00008

Gpio Register Locations

System Integration Unit Register Summary

49. Gpio Register Addresses Sheet 1

Interrupt Controller Register Locations

OS Timer Register Locations

Real-Time Clock Register Locations

Pulse Width Modulator Register Locations

52. OS Timer Register Addresses Sheet 2

53. Pulse Width Modulator Register Addresses

Dmac Block Diagram

DMA Description

Signal Descriptions

DREQ10 and PREQ370 Signals

Dmac Signal List

Signal Signal Type To/From Definition In/Out

Dmairq Signal

DMA Channel Priority Scheme

Channel Priority if all channels are running concurrently

Channel Priority

No-Descriptor Fetch Mode

DMA Descriptors

Priority Schemes Examples

DMA Channel Priority

Descriptor Fetch Mode

No-Descriptor Fetch Mode Channel State

DMA Controller

Channel States

Servicing an Interrupt

Read and Write Order

Byte Transfer Order

Trailing Bytes

Little Endian Transfers

Transferring Data

Servicing Internal Peripherals

Dcmdincsrcaddr = Dcmdflowsrc = Dcmdflowtrg =

Quick Reference for DMA Programming

DMA Quick Reference for Internal Peripherals Sheet 1

Dcmd

Drcmr

Servicing Companion Chips and External Peripherals

DMA Quick Reference for Internal Peripherals Sheet 2

Unit Function Fifo Address Width

Burst Size Source

DMA Controller

Memory-to-Memory Moves

Dmac Registers

DMA Interrupt Register Dint

DMA Channel Control/Status Register DCSRx

Dint Bit Definitions

DCSRx Bit Definitions Sheet 1

RUN

Reqpend

Stopstate Endintr Startintr Buserrintr

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

DCSRx Bit Definitions Sheet 2

DMA Request to Channel Map Registers DRCMRx

DMA Descriptor Address Registers DDADRx

DRCMRx Bit Definitions

Chlnum

DMA Source Address Registers

DDADRx Bit Definitions

Descriptor Address

Stop

DMA Target Address Registers DTADRx

10. DSADRx Bit Definitions

Source Address

Srcaddr

DMA Command Registers DCMDx

11. DTADRx Bit Definitions

Target Address

Trgaddr

12. DCMDx Bit Definitions Sheet 1

Incsrcaddr

Endian Width

Size

12. DCMDx Bit Definitions Sheet 2

Endian

Width

Length

Example 1. How to set up and start a channel

Examples

Struct longddadr longdsadr longdtadr shortlength shortdcmd

DMA Controller Register Summary

13. DMA Controller Register Summary Sheet 1

13. DMA Controller Register Summary Sheet 2

13. DMA Controller Register Summary Sheet 3

13. DMA Controller Register Summary Sheet 4

13. DMA Controller Register Summary Sheet 5

Memory Controller

Functional Description

Sdram Interface Overview

Static Memory Interface / Variable Latency I/O Interface

Memory System Examples

3 16-Bit PC Card / Compact Flash Interface

Sdram Memory System Example

Static Memory System Example

Memory Accesses

Device Transactions

Bus Operation Burst Size

Words Bits

Synchronous Dram Memory Interface

Reads and Writes

Aborts and Nonexistent Memory

Sdram Mdcnfg Register Mdcnfg

Mdcnfg Bit Definitions Sheet 1

Mdcnfg Bit Definitions Sheet 2

Mdcnfg Bit Definitions Sheet 3

DNB2

DADDR2

DLATCH2

Sdram Mode Register Set Configuration Register Mdmrs

Mdmrs Bit Definitions Sheet 1

Low-Power Sdram Mode Register Set Configuration Register

Mdmrs Bit Definitions Sheet 2

Sdram Mdrefr Register Mdrefr

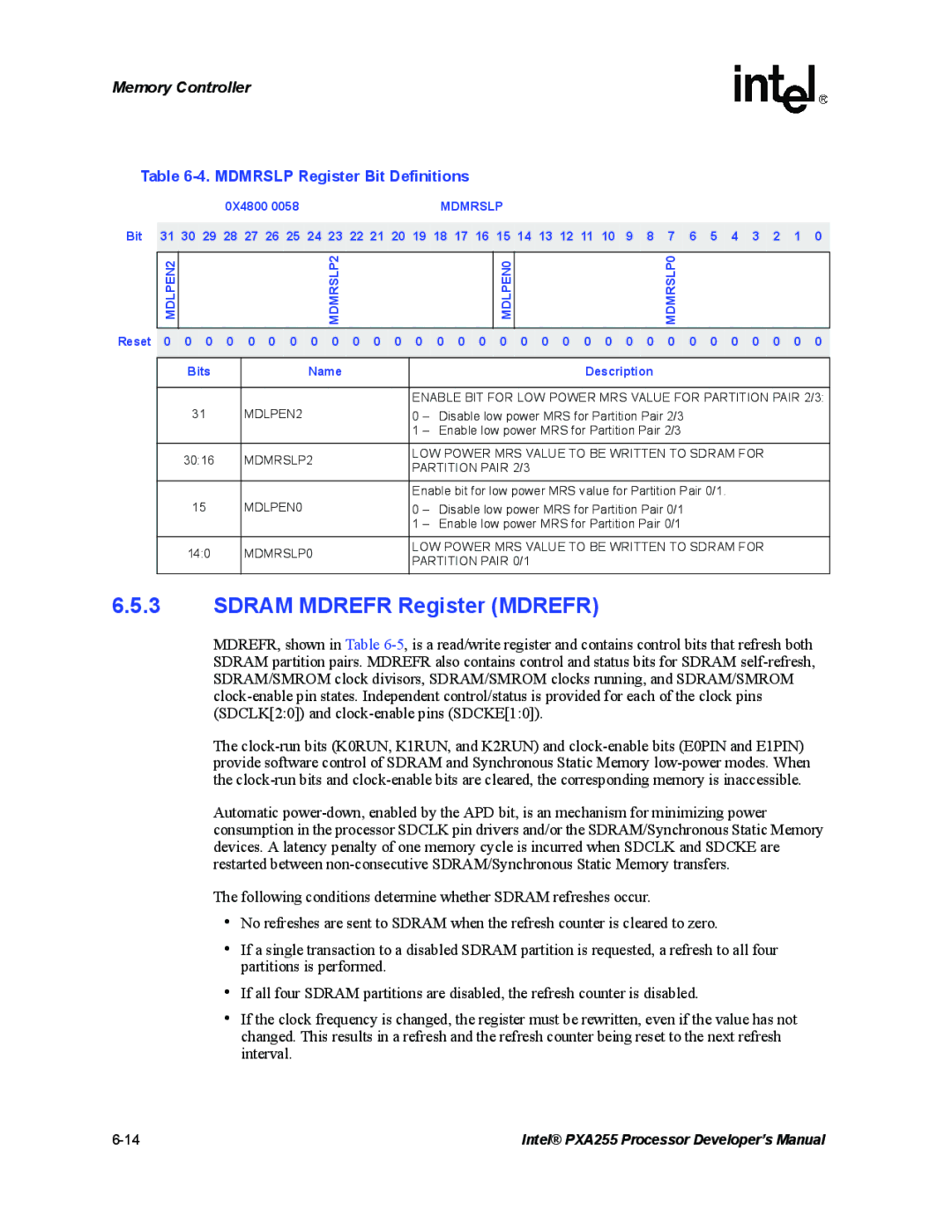

Mdmrslp Register Bit Definitions

0X4800

Mdmrslp

Mdrefr Bit Definitions Sheet 1

Mdrefr

APD K2DB2 K2RUN K1DB2 K1RUN E1PIN K0DB2 K0RUN E0PIN

DRI

0 1 0 0 1 * * 1

Mdrefr Bit Definitions Sheet 2

1 1 1 1 1 1 1

Mdrefr Bit Definitions Sheet 3

Fixed-Delay or Return-Clock Data Latching

APD

Sdram Memory Options

Sdram Addressing Modes

Sample Sdram Memory Size Options

Number Chips Partition Size

‘0’

# Bits

1x12x8x32 ‘0’ 1x12x8x16 1x12x9x32 1x12x9x16 1x12x10x32

MA2410

Col Data

2x13x10x16 ‘0’

# Bits External Address pins at Sdram RAS Time

Not Valid illegal addressing combination

MA24 MA23

MA20

BA0

A10

MA24

BA1 BA0

A11 A10

Memory Controller

Sdram Command Overview

A12

12. Sdram Mode Register Opcode Table

11. Sdram Command Encoding

Sdram Waveforms

Sdclk

Data

SDRAMreadsamebankdiffrow

SDRAMwrite

SDCLK1 SDCKE1

Synchronous Static Memory Configuration Register Sxcnfg

Synchronous Static Memory Interface

13. Sxcnfg Bit Definitions Sheet 1

0x4800001C

Sxcnfg

SXLATCH2 SXTP2 SXCA2 SXRA2 SXRL2 SXCL2 SXEN2

Sxcnfg Bit Definitions Sheet 2

SXLATCH2

SXRL2 SXCL2 SXEN2

SXLATCH0

13. Sxcnfg Bit Definitions Sheet 3

Smrom Memory Options

Sxcnfg Bit Definitions Sheet 4

SXCL0

SXEN0

Smrom

Synchronous Static Memory Timing Diagrams

16. Sxmrs Bit Definitions

Sxmrs

SXMRS2

Non-SDRAM Timing Sxmem Operation

Sdclk Sdcke

17. Read Configuration Register Programming Values

Memclk SDCLK0 Mdrefr

Non-SDRAM Timing Flash Read Timing Diagram

12shows the burst-of-eight read timing diagram

Asynchronous Static Memory

4.2 K3 Synchronous StrataFlash Reset

Static Memory Interface

Sram

19 -Bit Bus Write Access

20 -Bit Bus Write Access

Data Size MA10 DQM30

Data Size MA0 DQM10

22 -Bit Byte Address Bit MA0 for Reads Based on DQM10

21 -Bit Byte Address Bits MA10 for Reads Based on DQM30

23. SA-1111 Register Bit Definitions

Asynchronous Static Memory Control Registers MSCx

24. MSC0/1/2 Bit Definitions Sheet 1

MSC0

MSC1

MSC2

Bits Access Name

RRR1/3/5 RDN1/3/5 Reset RDF1/3/5

24. MSC0/1/2 Bit Definitions Sheet 2

24. MSC0/1/2 Bit Definitions Sheet 3

Sram

ROM Interface

Timing Memory Clocks MSCxRTx Device

NOE

NWE NOE

ROM Timing Diagrams and Parameters

Clkmem

RDN+1

Sram Timing Diagrams and Parameters

Sram Interface Overview

20shows the timing for Sram writes

Variable Latency I/O Vlio Interface Overview

Variable Latency I/O Timing Diagrams and Parameters

RDF+1+Waits RRR*2+1

RDF+1+Waits

Flash Memory Timing Diagrams and Parameters

Flash Memory Interface

23. Asynchronous 32-Bit Flash Write Timing Diagram 2 Writes

CMD Data

Expansion Memory Timing Configuration Register

16-Bit PC Card/Compact Flash Interface

26. MCMEM0/1 Bit Definitions

MCMEM0

27. MCATT0/1 Bit Definitions

28. MCIO0/1 Bit Definitions

MCATT0

MCATT1

29. Card Interface Command Assertion Code Table

MCMEMxASST XASSTHOLD XASSTWAIT +

Expansion Memory Configuration Register Mecr

30. Mecr Bit Definition

Mecr

CIT NOS

3 16-Bit PC Card Overview

26 -Bit PC Card Memory Map

31. Common Memory Space Write Commands

32. Common Memory Space Read Commands

33. Attribute Memory Space Write Commands

34. Attribute Memory Space Read Commands

38 -Bit I/O Space Read Commands nIOIS16 =

37 -Bit I/O Space Write Commands nIOIS16 =

External Logic for 16-Bit PC Card Implementation

DIR

Socket

Expansion Card Interface Timing Diagrams and Parameters

29 -Bit PC Card Memory or I/O 16-Bit Half-word Access

30 -Bit PC Card I/O 16-Bit Access to 8-Bit Device

Companion Chip Interface

31. Alternate Bus Master Mode

32. Variable Latency IO

Alternate Bus Master Mode

NVDDFAULT/nBATTFAULT with Pmcridae Disabled

Gpio Reset

NVDDFAULT/nBATTFAULT with Pmcridae Enabled

Options and Settings for Boot Memory

Alternate Booting

Boot Time Defaults

Bootdef Read-Only Register Bootdef

40. Bootdef Bitmap

41. Valid Boot Configurations Based on Processor Type

Bootdef

PKG Type Boot SEL

Boot-Time Configurations

Sxcnfg

34. Smrom Boot Time Configurations and Register Defaults

Smrom

Memory Interface Reset and Initialization

Mdrefr 03CA 7FFF

42. Memory Controller Pin Reset Values

Hardware, Watchdog, or Sleep Reset Operation

Pin Name PXA255 Processor Reset Value

Memory Controller

Gpio Reset Procedure

Physical Address Symbol Register Name

Memory Controller Register Summary

43. Memory Controller Register Summary Sheet 1

43. Memory Controller Register Summary Sheet 2

LCD Controller

Features

LCD Controller

LCD Controller Block Diagram

LCD Controller Operation

Pin Descriptions

Enabling the Controller

Pin Descriptions

Resetting the Controller

Detailed Module Descriptions

Disabling the Controller

Input FIFOs

Lookup Palette

Temporal Modulated Energy Distribution Tmed Dithering

Compare Range for Tmed

Output FIFOs

LCD Controller Pin Usage

Pixel Data Pins LDDx

6 DMA

Passive Display Timing

Active Display Timing

LCD External Palette and Frame Buffers

External Palette Buffer

External Frame Buffer

Palette Buffer Format

Bits Per Pixel Data Memory Organization

10 Bits Per Pixel Data Memory Organization Passive Mode

Functional Timing

FrameBufferSize =

12. Passive Mode Start-of-Frame Timing

Vsync

Hsync Lbias

Register Descriptions

Lfclk Vsync Llclk Hsync Lbias

LCD Controller Control Register 0 LCCR0

LCD Controller

LDD

LCD Controller Data Pin Utilization Sheet 1

Single Passive Screen Portion Pins

LCD Controller Data Pin Utilization Sheet 2

Reset X X X X X X X X X X X

LCCR0 Bit Definitions Sheet 1

LCCR0

0x44000000 Bit Reserved

LCD Controller Control Register 1 LCCR1

LCCR0 Bit Definitions Sheet 2

QDM DIS DPD

PAS EFM IUM SFM LDM SDS CMS ENB

LCD Controller

LCD Controller Control Register 2 LCCR2

LCCR1 Bit Definitions

BLW ELW HSW PPL

BLW

LCD Controller

LCD Controller Control Register 3 LCCR3

LCCR2 Bit Definitions

BFW EFW VSW LPP

BFW

LCD Controller

LCD Controller

Reset X X X X 0 0 0

LCCR3 Bit Definitions Sheet 1

0x4400000C Bit Reserved

DPC BPP

Reset X X X

LCD Controller DMA

Frame Descriptors

LCCR3 Bit Definitions Sheet 2

LCD DMA Frame Descriptor Address Registers FDADRx

LCD DMA Frame Source Address Registers FSADRx

FDADRx Bit Definitions

FDADR0

FSADRx Bit Definitions

LCD DMA Frame ID Registers FIDRx

FIDRx Bit Definitions

LCD DMA Command Registers LDCMDx

10. LDCMDx Bit Definitions

LDCMD0

LDCMD1

PAL

LCD DMA Frame Branch Registers FBRx

11. FBRx Bit Definitions

Bint BRA

0 0 0 0 X X 0 Bits Name Description

LCD Controller Status Register Lcsr

LCD Controller

0x44000038 Bit Reset X X

Lcsr Bit Definitions Sheet 1

X X

EOF IUU IUL ABC BER SOF LDD

LCD Controller Interrupt ID Register Liidr

12. Lcsr Bit Definitions Sheet 2

13. Liicr Bit Definitions

Sint BS EOF QD OU IUU IUL ABC BER SOF LDD

Tmed RGB Seed Register Trgbr

14. Trgbr Bit Definitions

TBS

TRS

Tmed Control Register TCR

15. TCR Bit Definitions

LCD Controller Register Summary

16. LCD Controller Register Summary Sheet 1

16. LCD Controller Register Summary Sheet 2

LCD Controller

Signal Description

External Interface to Synchronous Serial Peripherals

External Interface to Codec

Name Direction Description

Data Transfer

Data Formats

Serial Data Formats for Transfer to/from Peripherals

SSP Format Details

SPI Format Details

Sspsclk Sspsfrm

Sspsclk Sspsfrm MSB

LSB

Microwire Format Details

Sspsclk Sspsfrm Ssptxd Ssprxd

National Microwire* Frame Format

Parallel Data Formats for Fifo Storage

Using Programmed I/O Data Transfers

Using DMA Data Transfers

Fifo Operation and Data Transfers

Baud-Rate Generation

SSP Serial Port Registers

SSP Control Register 0 SSCR0

Data Size Select DSS

SSCR0 Bit Definitions

SSP Control Register 0 SSCR0

SCR

Frame Format FRF

Synchronous Serial Port Enable SSE

External Clock Select ECS

Serial Clock Rate SCR

SSP Control Register 1 SSCR1

SSCR1 Bit Definitions Sheet 1

Receive Fifo Interrupt Enable RIE

Transmit Fifo Interrupt Enable TIE

Loop Back Mode LBM

SSCR1 Bit Definitions Sheet 2

Serial Clock Polarity SPO

Serial Clock Phase SPH

Sspsclk SPO=0 Sspsclk SPO=1 Sspsfrm Ssptxd

Microwire Transmit Data Size Mwds

Transmit Fifo Interrupt/DMA Threshold TFT

Receive Fifo Interrupt/DMA Threshold RFT

Ssprxd Sspsclk SPO=0 Sspsclk SPO=1 Sspsfrm Ssptxd

TFT and RFT Values for DMA Servicing

SSP Data Register Ssdr

Ssdr Bit Definitions

SSP Status Register Sssr

Transmit Fifo Not Full Flag TNF

Sssr Bit Definitions

RFL TFL ROR RFS TFS BSY RNE TNF

RFL

Transmit Fifo Service Request Flag TFS

Receive Fifo Service Request Flag RFS

Receive Fifo Not Empty Flag RNE

SSP Busy Flag BSY

SSP Controller Register Summary

Receive Fifo Level RFL

SSP Controller Register Summary

Address Abbreviation Full Name

Synchronous Serial Port Controller

I2C Signal Description

Signal Name Input/Output Description

SDA

SCL

I2C Bus Definitions

2C Device Definition

Mode Description

Operational Blocks

2 I2C Bus Interface Modes

Modes of Operation

Start and Stop Bus States

Start and Stop Bit Definitions

Stop Star

Condition

No Start or Stop Condition

Start Condition

Stop Condition

ACK NAK

Start

ACK

ACK Stop NAK

Serial Clock Line SCL Generation

I2C Bus Operation

Data and Addressing Management

3 I2C Acknowledge

Addressing a Slave Device

Polling

Arbitration

SCL Arbitration

SDA Arbitration

Arbitration Procedure of Two Masters

Master Operations

2C Master Mode Definition Action Operation

Master Transactions Sheet 1

Master Transactions Sheet 2

Slave Operations

Master-Receiver Read from Slave-Transmitter

2C Slave Action Mode Definition Operation

Slave Transactions

ACK Stop

General Call Address

NAK Stop

General Call Address Second Byte Definitions

Least Second

Slave Mode Programming Examples

Initialize Unit

Write n Bytes as a Slave

Read n Bytes as a Slave

Master Programming Examples

Write 1 Byte as a Master

Read 1 Byte as a Master

Write 2 Bytes and Repeated Start Read 1 Byte as a Master

Read 2 Bytes as a Master Send Stop Using the Abort

Reset Conditions

Glitch Suppression Logic

Register Definitions

1 I2C Bus Monitor Register Ibmr

2 I2C Data Buffer Register Idbr

Ibmr Bit Definitions

Idbr Bit Definitions

3 I2C Control Register ICR

10. ICR Bit Definitions Sheet 1

40301690 Bit Reset

Disable interrupt

10. ICR Bit Definitions Sheet 2

Beie Irfie Iteie GCD IUE

4 I2C Status Register ISR

Receive mode

10. ICR Bit Definitions Sheet 3

11. ISR Bit Definitions Sheet 1

2C Status Register

40301698 Bit

BED SAD

5 I2C Slave Address Register Isar

11. ISR Bit Definitions Sheet 2

12. Isar Bit Definitions

BED SAD Gcad IRF ITE ALD SSD IBB

I2C Bus Interface Unit

Feature List

UARTs

Bluetooth Uart

Full Function Uart

Standard Uart

Compatibility with

Signal Descriptions

Uart Signal Descriptions Sheet 1

Name Type Description

RXD

Uart Operational Description

Uart Signal Descriptions Sheet 2

LSB MSB

Reset

Internal Register Descriptions

Register Accessed

Receive Buffer Register RBR

Uart Register Addresses as Offsets of a Base

RBR Bit Definitions

Divisor Latch Registers DLL and DLH

Transmit Holding Register THR

THR Bit Definitions

DLL Bit Definitions

Interrupt Enable Register IER

DLH Bit Definitions

Interrupt Identification Register IIR

IER Bit Definitions

Interrupt Conditions

IIR Bit Definitions Sheet 1

Priority Level Interrupt origin

FIFOES10

Interrupt ID Bits Interrupt SET/RESET Function

Fcrresetrf

IIR Bit Definitions Sheet 2

10. Interrupt Identification Register Decode Sheet 1

Fifo Control Register FCR

10. Interrupt Identification Register Decode Sheet 2

11. FCR Bit Definitions Sheet 1

ITL

Line Control Register LCR

11. FCR Bit Definitions Sheet 2

Base+0x0C

12. LCR Bit Definitions

Uart Dlab Stkyp EPS PEN STB WLS1 WLS0

Line Status Register LSR

13. LSR Bit Definitions Sheet 1

Fifoe

Temt

13. LSR Bit Definitions Sheet 2

Tdrq

13. LSR Bit Definitions Sheet 3

Modem Control Register MCR

14. MCR Bit Definitions Sheet 1

Uart

Loop OUT2 OUT1 RTS DTR

14. MCR Bit Definitions Sheet 2

Modem Status Register MSR

Base+0x10 Modem Control Register

15. MSR Bit Definitions

Fifo Interrupt Mode Operation

Character Timeout Indication Interrupt

Scratchpad Register SPR

Receive Interrupt

DMA Requests

Fifo Polled Mode Operation

Transmit Interrupt

Trailing Bytes in the Receive Fifo

Slow Infrared Asynchronous Interface

Infrared Selection Register ISR

Operation

17. ISR Bit Definitions

IR Transmit and Receive Example

Uart Register Summary

18. Ffuart Register Summary

19. Btuart Register Summary Sheet 1

Dlab Bit Name Description

19. Btuart Register Summary Sheet 2

20. Stuart Register Summary

Uart Register Differences

21. Flow Control Registers in Btuart and Stuart

Btmcr

Btmsr

Ficp Signal Description

Ficp Operation

11.2.1 4PPM Modulation

PPM Modulation Encodings

Frame Format

Address Field

Control Field

Data Field

Baud Rate Generation

CRC Field

Receive Operation

Transmit Operation

Transmit and Receive FIFOs

Trailing or Error Bytes in the Receive Fifo

Ficp Register Definitions

Ficp Control Register 0 ICCR0

ICCR0 Bit Definitions Sheet 1

ICCR0 Bit Definitions Sheet 2

TXE

TUS

LBM

Ficp Control Register 1 ICCR1

ICCR1 Bit Definitions

Ficp Control Register 2 ICCR2

ICCR2 Bit Definitions

Ficp Data Register Icdr

Icrd Bit Definitions

Ficp Status Register 0 ICSR0

ICSR0 Bit Definitions Sheet 1

FRE

RFS

TUR

ICSR0 Bit Definitions Sheet 2

EIF

Ficp Status Register 1 ICSR1

ICSR1 Bit Definitions

Ficp Register Summary

Ficp Register Summary

USB Device Controller

USB Overview

Device Configuration

Endpoint Configuration

USB Protocol

IN/OUT

Signalling Levels

Bit Encoding

USB States

Bus State UDC+/UDC- Pin Levels

Field Formats

Nrzi Bit Encoding Example

IN, OUT, and Setup Token Packet Format

Packet Formats

Token Packet Type

Start of Frame Packet Type

Transaction Formats

Data Packet Type

Handshake Packet Type

Bulk Transaction Type

Isochronous Transaction Type

Control Transaction Type

Bulk Transaction Formats

Isochronous Transaction Formats

Interrupt Transaction Type

UDC Device Requests

10. Interrupt Transaction Formats

11. Host Device Request Summary

Configuration

Request Name

Self-Powered Device

UDC Hardware Connection

When GPIOn and GPIOx are Different Pins

When GPIOn and GPIOx are the Same Pin

UDC Operation

Bus-Powered Devices

Case 1 EP0 Control Read

Case 2 EP0 Control Read with a Premature Status Stage

12-14 Intel PXA255 Processor Developer’s Manual

Software Enables the DMA

Case 4 EP0 No Data Command

Case 5 EP1 Data Transmit BULK-IN

Software Enables the EP1 Interrupt

Case 6 EP2 Data Receive BULK-OUT

Case 7 EP3 Data Transmit ISOCHRONOUS-IN

Software Enables DMA

Software Allows the Megacell to Handle the Transaction

Software Enables the SOF Interrupt

Software Enables the EP3 Interrupt

Case 8 EP4 Data Receive ISOCHRONOUS-OUT

Intel PXA255 Processor Developer’s Manual 12-19

Case 10 Reset Interrupt

Case 9 EP5 Data Transmit INTERRUPT-IN

Case 11 Suspend Interrupt

UDC Register Definitions

Case 12 Resume Interrupt

UDC Control Register Udccr

UDC Enable UDE

12. Udccr Bit Definitions

Reset Interrupt Request Rstir

Reset Interrupt Mask REM

UDC Active UDA

UDC Resume RSM

ACK Control Mode

ACK Response Enable

UDC Control Function Register Udccfr

13. UDC Control Function Register

UDC Endpoint 0 Control/Status Register UDCCS0

OUT Packet Ready OPR

Packet Ready IPR

14. UDCCS0 Bit Definitions

Device Remote Wakeup Feature Drwf

Flush Tx Fifo FTF

Sent Stall SST

Force Stall FST

Setup Active SA

Transmit Fifo Service TFS

UDC Endpoint x Control/Status Register UDCCS1/6/11

15. UDCCS1/6/11 Bit Definitions

Transmit Underrun TUR

Transmit Packet Complete TPC

Bit 6 Reserved

Transmit Short Packet TSP

UDC Endpoint x Control/Status Register UDCCS2/7/12

16. UDCCS2/7/12 Bit Definitions

Receive Fifo Service RFS

DMA Enable DME

Receive Packet Complete RPC

Bit 2 Reserved

Receive Short Packet RSP

UDC Endpoint x Control/Status Register UDCCS3/8/13

17. UDCCS3/8/13 Bit Definitions

UDC Endpoint x Control/Status Register UDCCS4/9/14

Bits 64 Reserved

Receive Overflow ROF

18. UDCCS4/9/14 Bit Definitions

Bits 54 Reserved

UDC Endpoint x Control/Status Register UDCCS5/10/15

19. UDCCS5/10/15 Bit Definitions Sheet 1

19. UDCCS5/10/15 Bit Definitions Sheet 2

UDC Interrupt Control Register 0 UICR0

Interrupt Mask Endpoint x IMx, Where x is 0 through

20. UICR0 Bit Definitions

UICR0

IM7 IM6 IM5 IM4 IM3 IM2 IM1 IM0

Interrupt Mask Endpoint x IMx, where x is 8 through

UDC Interrupt Control Register 1 UICR1

21. UICR1 Bit Definitions

UICR1

UDC Status/Interrupt Register 0 USIR0

Endpoint 0 Interrupt Request IR0

Endpoint 1 Interrupt Request IR1

22. USIR0 Bit Definitions

Endpoint 2 Interrupt Request IR2

Endpoint 3 Interrupt Request IR3

Endpoint 4 Interrupt Request IR4

Endpoint 5 Interrupt Request IR5

UDC Status/Interrupt Register 1 USIR1

Endpoint 8 Interrupt Request IR8

Endpoint 9 Interrupt Request IR9

Endpoint 10 Interrupt Request IR10

UDC Frame Number High Register Ufnhr

Isochronous Packet Error Endpoint 4 IPE4

Isochronous Packet Error Endpoint 9 IPE9

UDC Frame Number MSB Fnmsb

24. Ufnhr Bit Definitions

Isochronous Packet Error Endpoint 14 IPE14

UDC Frame Number Low Register Ufnlr

UDC Byte Count Register x UBCR2/4/7/9/12/14

Start of Frame Interrupt Mask SIM

Endpoint x Byte Count BC

UDC Endpoint 0 Data Register UDDR0

26. UBCR2/4/7/9/12/14 Bit Definitions

UDC Endpoint x Data Register UDDR1/6/11

UDC Endpoint x Data Register UDDR2/7/12

27. UDDR0 Bit Definitions

28. UDDR1/6/11 Bit Definitions

UDC Endpoint x Data Register UDDR3/8/13

UDC Endpoint x Data Register UDDR4/9/14

29. UDDR2/7/12 Bit Definitions

30. UDDR3/8/13 Bit Definitions

USB Device Controller Register Summary

UDC Endpoint x Data Register UDDR5/10/15

31. UDDR4/9/14 Bit Definitions

32. UDDR5/10/15 Bit Definitions

Ufnhr

33. USB Device Controller Register Summary Sheet 2

Ufnlr

33. USB Device Controller Register Summary Sheet 3

AC’97 Controller Unit

Signal Configuration Steps

Example AC-link

External Interface to CODECs

Name Direction Description summary

AC-link Digital Serial Interface Protocol

Supported Data Stream Formats Sheet 1

SDATAIN0 SDATAIN1

Channel Slots Comments

Supported Data Stream Formats Sheet 2

AC-link Audio Output Frame Sdataout

Sync

AC-link Audio Output Frame

Slot 0 Tag Phase

Slot 1 Command Address Port

Slot 2 Command Data Port

Slot 3 PCM Playback Left Channel

Slot 1 Bit Definitions

Slot 2 Bit Definitions

AC-link Audio Input Frame Sdatain

Slot 4 PCM Playback Right Channel

Slot 5 Modem Line Codec

Slots 6-11 Reserved

Sync

Input Slot 1 Bit Definitions Sheet 1

Slot 1 Status Address Port/SLOTREQ bits

Bit Description

Slot 2 Status Data Port

Slot 3 PCM Record Left Channel

Slot 4 PCM Record Right Channel

Slot 5 Optional Modem Line Codec

AC-link Low Power Mode

Powering Down the AC-link

Slots 7-11 Reserved

Slot 12 I/O Status

Waking up the AC-link

Wake up triggered by the Codec

Cold AC’97 Reset

Warm AC’97 Reset

Acunit Operation

Wake Up Triggered by the Acunit

Initialization

13-16 Intel PXA255 Processor Developer’s Manual

Operational Flow for Accessing Codec Registers

Clocks and Sampling Frequencies

Receive Fifo Errors

Transmit Fifo Errors

FIFOs

Interrupts

Registers

Global Control Register GCR

GCR Bit Definitions Sheet 1

Global Status Register GSR

GCR Bit Definitions Sheet 2

Warmrst

Coldrst

GSR Bit Definitions Sheet 1

Cdone Sdone

Rdcs

Secres Prires SCR PCR Mint Point Piint

GSR Bit Definitions Sheet 2

PCM-Out Control Register Pocr

Pocr Bit Definitions Sheet 1

Pocr Bit Definitions Sheet 2

PCM-In Control Register Picr

10. Picr Bit Definitions

PCM-Out Status Register Posr

PCMIn Status Register Pisr

11. Posr Bit Definitions

12. Pisr Bit Definitions

Codec Access Register CAR

PCM Data Register Pcdr

13. CAR Bit Definitions

14. Pcdr Bit Definitions

Mic-In Control Register Mccr

Mic-In Status Register Mcsr

15. Mccr Bit Definitions

Mccr Register

Mic-In Data Register Mcdr

16. Mcsr Bit Definitions

17. Mcdr Bit Definitions

Micindat

Modem-Out Control Register Mocr

Modem-In Control Register Micr

18. Mocr Bit Definitions

Mocr Register

Modem-Out Status Register Mosr

Modem-In Status Register Misr

19. Micr Bit Definitions

20. Mosr Bit Definitions

Modem Data Register Modr

21. Misr Bit Definitions

22. Modr Bit Definitions

Modemdat

Accessing Codec Registers

11. Modem Transmit and Receive Operation

Processor Bit Physical

23. Address Mapping for Codec Registers Sheet 1

Address for a Primary Secondary Audio Codec Modem Codec

23. Address Mapping for Codec Registers Sheet 2

13.9 AC’97 Register Summary

24. Register Mapping Summary

13-36 Intel PXA255 Processor Developer’s Manual

Inter-Integrated-Circuit Sound I2S Controller

GP32/SYSCLK

GP29/SDATAIN

Controller Operation

Disabling and Enabling Audio Replay

Disabling and Enabling Audio Record

Receive Fifo Errors

Transmit Fifo Errors

Serial Audio Clocks and Sampling Frequencies

Fifo and Memory Format

14.5.2 I2S and MSB-Justified Serial Audio Formats

Supported Sampling Frequencies

Sysclk = Bitclk =

I2S Data Formats 16 bits

Registers

Serial Audio Controller Global Control Register SACR0

Special purpose Fifo Read/Write function

SACR0 Bit Definitions

Suggested Tfth and Rfth for DMA servicing

Fifo Write/Read table

Tfth and Rfth Values for DMA Servicing

Efwr Strf

SACR1 Bit Definitions

Enlbf

Drpl

Drec

Serial Audio Clock Divider Register Sadiv

SASR0 Bit Definitions

RFL

TFL

Sadiv Bit Definitions

Serial Audio Interrupt Clear Register Saicr

Saicr Bit Definitions

Serial Audio Interrupt Mask Register Saimr

Serial Audio Data Register Sadr

10. Saimr Bit Descriptions

11. Sadr Bit Descriptions

Transmit and Receive Fifo Accesses Through the Sadr

14.8 I2S Controller Register Summary

12. Register Memory Map

Address Register Description Paddr90 Name

MultiMediaCard Controller

MMC Data Token Format

Command Token Format

SPI Data Token Format

Mmcmd

Mmdat

MMC Controller Functional Description

CRC

Intel PXA255 Processor Developer’s Manual 15-5

Signal Description

MMC Controller Reset

MMC Signal Description

Card Initialization Sequence

MMC Mode

Error Detection

SPI Mode

Clock Control

Response Data Fifo Mmcres

Data FIFOs

Receive Data FIFO, Mmcrxfifo

Transmit Data FIFO, Mmctxfifo

Card Communication Protocol

DMA and Program I/O

Basic, No Data, Command and Response Sequence

Mmcclkrt Mmcspi Mmcresto

Block Data Write

Block Data Read

Stream Data Write

Busy Sequence

Stream Data Read

Enabling SPI Mode

MultiMediaCard Controller Operation

SPI Functionality

Start and Stop Clock

Erase

No Data Command and Response Sequence

Single Data Block Write

Single Block Read

Multiple Block Write

Multiple Block Read

Stream Write

Stream Read

MMC Controller Registers

Mmcstrpcl Register

MMCStatus Register Mmcstat

Mmcstrpcl Bit Definitions

Mmcstat Bit Definitions Sheet 1

Strpcl

Mmcclkrt Register Mmcclkrt

Mmcstat Bit Definitions Sheet 2

Mmcclk Bit Definitions

Mmcspi Register Mmcspi

Mmcspi Bit Definitions Sheet 1

Mmcspi Bit Definitions Sheet 2

Mmccmdat Register Mmccmdat

Mmccmdat Bit Definitions Sheet 1

Mmccmdat Bit Definitions Sheet 2

Mmcresto Register Mmcresto

10. Mmcresto Bit Definitions

Mmcrdto Register Mmcrdto

11. Mmcrdto Register

Readto

Specifies the length of time before a data read time-out

Mmcblklen Register Mmcblklen

Mmcnob Register Mmcnob

12. Mmcblklen Bit Definitions

13. Mmcnob Bit Definitions

Mmcprtbuf Register Mmcprtbuf

Mmcimask Register Mmcimask

14. Mmcprtbuf Bit Definitions

15. Mmcimask Bit Definitions Sheet 1

Mmcireg Register Mmcireg

15. Mmcimask Bit Definitions Sheet 2

Mmcimask Register MultiMediaCard Controller

4 3 2 1

16. Mmcireg Bit Definitions

18. Command Index Values Sheet 1

CMD Comm Mode Abbreviation Index

Mmccmd Register Mmccmd

17. Mmccmd Register

18. Command Index Values Sheet 2

18. Command Index Values Sheet 3

Mmcargh Register Mmcargh

Mmcargl Register Mmcargl

19. Mmcargh Bit Definitions

Mmcres Fifo

21. MMCRES, Fifo Entry

22. MMCRXFIFO, Fifo Entry

Responsedata

MultiMediaCard Controller Register Summary

23. MMCTXFIFO, Fifo Entry

24. MMC Controller Registers Sheet 1

Writedata

24. MMC Controller Registers Sheet 2

Features

Network SSP Serial Port

SSP Serial Port I/O Signals

Processor and DMA Fifo Access

Operation

Trailing Bytes in the Receive Fifo

Data Formats

16-4 Intel PXA255 Processor Developer’s Manual

TI Synchronous Serial Protocol* Details

SPI Protocol Details

Serial Clock Phase SPH

Motorola SPI* Frame Protocol multiple transfers

16-8 Intel PXA255 Processor Developer’s Manual

Microwire* Protocol Details

PSP Details

Programmable Serial Protocol multiple transfers

Programmable Serial Protocol PSP Parameters

Sspspscmode

Sspspsfrmp

Sspspstrtdly

Hi-Z on Ssptxd

11. TI SSP with SSCRTTE=1 and SSCRTTELP=0

Motorola SPI

Programmable Serial Protocol

16-16 Intel PXA255 Processor Developer’s Manual

Fifo Operation

Baud-Rate Generation

16-18 Intel PXA255 Processor Developer’s Manual

SSCR0 Bit Definitions Sheet 1

SSCR0

SCR SSE

FRF DSS

SSCR0 Bit Definitions Sheet 2

Edss SCR SSE

Data Size Select

Edss DSS

Ttelp TTE Ebcei

Sclkdir Sfrmdir Scfr

SSCR1

SPH SPO LBM TIE RIE

SSP Programmable Serial Protocol Register Sspsp

Sspsp Bit Definitions Sheet 1

SSP Time Out Register Ssto

SSP Interrupt Test Register Ssitr

Sspsp Bit Definitions Sheet 2

Ssto Bit Definitions

Test Receive Fifo Service Request Trfs

Test Transmit Fifo Service Request Ttfs

Ssitr Bit Definitions

Ssitr

Sssr Bit Definitions Sheet 1

Sssr

BCE CSS TUR

Tint

Sssr Bit Definitions Sheet 2

Transmit Fifo Service Request

Sssr Bit Definitions Sheet 3

SSP Busy

Receive Fifo not Empty

Network SSP Serial Port Register Summary

10. Nssp Register Address Map

Ssdr

Data TRANSMIT/RECEIVE Data

16-30 Intel PXA255 Processor Developer’s Manual

Hardware Uart

Hardware Uart

Uart Signal Descriptions

Operation

17-4 Intel PXA255 Processor Developer’s Manual

Fifo Interrupt Mode Operation

Fifo Polled Mode Operation

Character Timeout Interrupt

Receive Interrupt

DMA Receive Programming Errors

Fifo DMA Mode Operation

DMA Error Handling

Autoflow Control

Removing Trailing Bytes In DMA Mode

Auto-Baud-Rate Detection

17-8 Intel PXA255 Processor Developer’s Manual

Intel PXA255 Processor Developer’s Manual 17-9

Receive Buffer Register RBR

Transmit Holding Register THR

Divisor Latch Registers DLL and DLH

Bit Reserved Byte Bits Name Description 318

Interrupt Enable Register IER

Divisor Latch Register High DLH Bit Definitions

DLL

DLH

0x41600004 Bit Reset ? ? ? ? ? ? ? Bits Name

Physical Address Interrupt Enable Register IER

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 0 0 0 0 0 0 0 Description

Interrupt Identification Register IIR

IIR

ABL TOD IID

NIP

Priority Type Source Reset Control

Interrupt Identification Register Decode Sheet 1

0x41600008

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 0 0 ? 0 0 0 0

Interrupt Identification Register Decode Sheet 2

Fifo Control Register FCR

10. FCR Bit Definitions Sheet 1

10. FCR Bit Definitions Sheet 2

Receive Fifo Occupancy Register for

11. for Bit Definitions

Auto-Baud Control Register ABR

Auto-Baud Count Register ACR

12. ABR Bit Definitions

ABT

Line Control Register LCR

13. ACR Bit Definitions

14. LCR Bit Definitions Sheet 1

ACR

Line Status Register LSR

14. LCR Bit Definitions Sheet 2

Line Control Register LCR PXA255 Processor Hardware Uart

Dlab Stkyp EPS PEN STB WLS

0x41600014 Bit

15. LSR Bit Definitions Sheet 1

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 0 1 1 0 0 0 0 Bits

Modem Control Register MCR

15. LSR Bit Definitions Sheet 2

Line Status Register LSR PXA255 Processor Hardware Uart

0 0 0 0 Bits Name Description

0x41600010 Bit Reset ? ? ? ? ? ? ? Bits

16. MCR Bit Definitions Sheet 1

Physical Address Modem Control Register MCR

AFE

16. MCR Bit Definitions Sheet 2

Modem Status Register MSR

17. MSR Bit Definitions Sheet 1

Scratchpad Register SCR

Infrared Selection Register ISR

17. MSR Bit Definitions Sheet 2

18. SCR Bit Definitions

Hardware Uart Register Summary

19. ISR Bit Definitions

20. Hwuart Register Locations Sheet 1

Rxpl Txpl Xmode Rcveir Xmitir

20. Hwuart Register Locations Sheet 2

Intel PXA255 Processor Developer’s Manual 17-27