8XC196NP, 80C196NU Microcontroller User’ Manual

8XC196NP, 80C196NU Microcontroller User’s Manual

Intel Corporation

Contents

Chapter Programming Considerations

Contents

Chapter Ports

EPA Functional Overview

Programming the Serial Port

8XC196NP, 80C196NU USER’S Manual

Chapter Interfacing with External Memory

Appendix C Registers Glossary Index

Figures

10-7 Valid EPA Input Events

13-16

Tables

10-5 Example Control Register Settings and EPA Operations

8XC196NP and 80C196NU Signals Arranged by Function

Guide to This Manual

Page

Chapter Guide to this Manual

Manual Contents

8XC196NP, 80C196NU USER’S Manual

Addresses

Notational Conventions and Terminology

Italics

Related Documents

Units of measure

Application Notes, Application Briefs, and Article Reprints

Handbooks and Product Information

Title Order Number

MCS 96 Microcontroller Datasheets Automotive

MCS 96 Microcontroller Datasheets Commercial/Express

8XC196NP, 80C196NU USER’S Manual

Intentionally Left Blank

Intentionally Left Blank

Technical Support

World Wide Web

Product Literature

Page

Architectural Overview

Page

Typical Applications

Chapter Architectural Overview

ROM

Device Features

Block Diagram

Features of the 8XC196NP and 80C196NU

Register File

CPU Control

Code Execution

Register Arithmetic-logic Unit Ralu

Instruction Format

Memory Controller

Multiply-accumulate 80C196NU Only

Interrupt Service

Clock Circuitry 8XC196NP

Internal Timing

Clock Circuitry 80C196NU

50 MHz

State Times at Various Frequencies

12.5 MHz

25 MHz

Multiplier State Time

PLLEN21

Serial I/O SIO Port

Event Processor Array EPA and Timer/Counters

Internal Peripherals

1 I/O Ports

Pulse-width Modulator PWM

Reducing Power Consumption

Special Operating Modes

Design Considerations for 80C196NP to 80C196NU Conversions

Testing the Printed Circuit Board

8XC196NP, 80C196NU USER’S Manual

Advanced Math Features

Page

Enhanced Multiplication Instructions

Chapter Advanced Math Features

Instructions Execution Time

Saturation Mode

Operating Modes

Multiply/Accumulate Example Code

Fractional Mode

Accumulator Register ACC0x

Accstat

Accumulator Control and Status Register Accstat

Bit Function Number Mnemonic

SME FME

Effect of SME and FME Bit Combinations

Description

Programming Considerations

Page

Restrictions

Overview of the Instruction SET

Operand Type Definitions

Operand Type No. Signed Possible Values Addressing

Byte Operands

BIT Operands

SHORT-INTEGER Operands

Integer Operands

Word Operands

DOUBLE-WORD Operands

Conditional Jumps

LONG-INTEGER Operands

QUAD-WORD Operands

Converting Operands

Extended Instructions

Floating Point Operations

Addressing Modes

EST

Definition of Temporary Registers

Direct Addressing

Immediate Addressing

Indirect Addressing

Indirect Addressing with Autoincrement

Extended Indirect Addressing

Extended Indirect Addressing with Autoincrement

Long-indexed Addressing

Indexed Addressing

Indirect Addressing with the Stack Pointer

Short-indexed Addressing

Zero-indexed Addressing

Extended Indexed Addressing

Extended Zero-indexed Addressing

Software Standards and Conventions

Assembly Language Addressing Mode Selections

Extended Addressing

Design Considerations for 1-MBYTE Devices

Addressing 32-bit Operands

Using Registers

Addressing 64-bit Operands

Linking Subroutines

Software Protection Features and Guidelines

Memory Partitions

Page

Memory MAP Overview

Chapter Memory Partitions

F0H

FFH 2FH 1FH 0FH F1H

FFH

Memory Partitions

80C196NP/NU External 83C196NP ROM

Hex Description Addressing Modes

XC196NP and 80C196NU Memory Map

Program Memory in Page FFH

Program Memory Access for the 83C196NP

External Memory

Program and Special-purpose Memory

Special-purpose Memory

Special-purpose Memory Access for the 83C196NP

XC196NP and 80C196NU Special-purpose Memory Addresses

Interrupt and PTS Vectors

Chip Configuration Bytes

Peripheral Special-function Registers SFRs

Reserved Memory Locations

Peripheral SFRs

1F4EH

1F7EH

1F7CH

1F7AH

CPU SFRs

Stack Pointer

Address Description Addressing Modes Range

Register File Memory Addresses

General-purpose Register RAM

Stack Pointer SP

80C196NU CPU SFRs Address High Odd Byte Low Even Byte

CPU Special-function Registers SFRs

CPU SFRs

8XC196NP CPU SFRs Address High Odd Byte Low Even Byte

8XC196NP

Windowing

Bit Function

Selecting a Window

WSR

Hlden

Selecting a Window of the Upper Register File

Addressing a Location Through a Window

Upper Register File

10. Windows

Base WSR or WSR1 Value WSR Value for

Peripheral SFRs

2.3 128-byte Windowing Example

11. Windowed Base Addresses

2.1 32-byte Windowing Example

2.2 64-byte Windowing Example

Unsupported Locations Windowing Example 8XC196NP Only

Using the Linker Locator to Set Up a Window

Type Base Length Alignment

Windowing and Addressing Modes

This listing shows the disassembled code

Remapping Internal ROM 83C196NP only

Epcpc

Accessing Data

Fetching Code and Data in the 1-MBYTE and 64-KBYTE Modes

Fetching Instructions

Formation of Extended and Nonextended Addresses

Code Fetches in the 64-Kbyte Mode

Code Fetches in the 1-Mbyte Mode

80C196NP and 80C196NU

Data Fetches in the 1-Mbyte and 64-Kbyte Modes

CE#

Memory Configuration Examples

Example 1 Using the 64-Kbyte Mode

RD# WR#

80C196NP and 80C196NU Unimplemented

12. Memory Map for the System in Figure

Address Description

80C196NP and 80C196NU External flash memory

02FFFFH

Example 2 a 64-Kbyte System with Additional Data Storage

RD# WR# CE#

Ffffffh D70 OE# WE#

80C196NP and 80C196NU External RAM

13. Memory Map for the System in Figure

01FFFFH

Example 3 Using 1-Mbyte Mode

OE# WE# OE# WRH# WRL# RD#

80C196NP and 80C196NU External memory

14. Memory Map for the System in Figure

Fbffffh

Standard and PTS Interrupts

Page

Overview of Interrupts

Chapter Standard and PTS Interrupts

Flow Diagram for PTS and Standard Interrupts

Interrupt Signals

Interrupt Signals and Registers

Interrupt and PTS Control and Status Registers

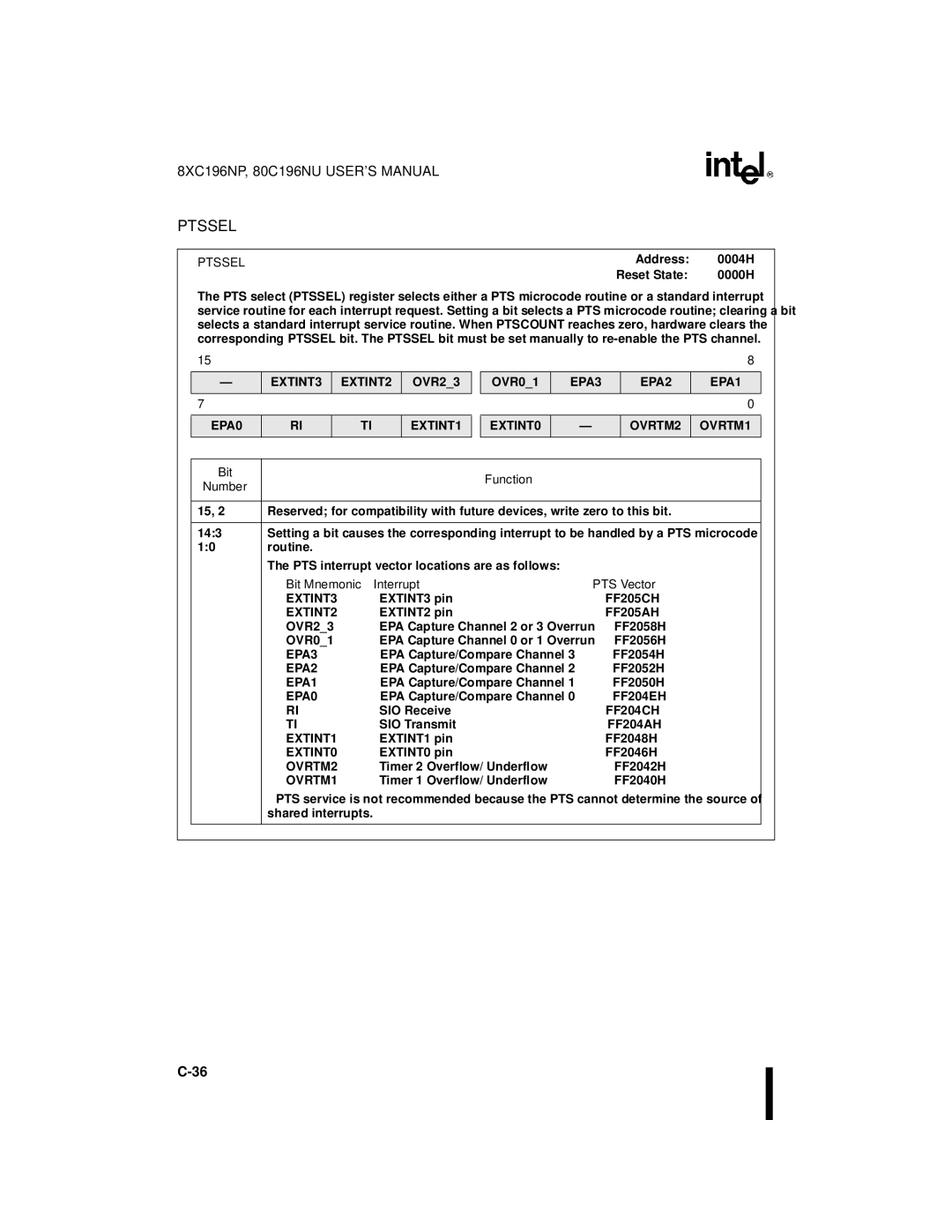

Ptssel

Interrupt Sources and Priorities

Special Interrupts

Intpend

Software Trap

Interrupt Controller PTS Service

Interrupt Sources, Vectors, and Priorities

Unimplemented Opcode

1.3 NMI

External Interrupt Pins

Multiplexed Interrupt Sources

End-of-PTS Interrupts

Situations that Increase Interrupt Latency

Interrupt Latency

Standard Interrupt Latency

Calculating Latency

Standard Interrupt Response Time PTS Interrupt Latency

Programming the Interrupts

PTS Mode Execution Time in State Times

Execution Times for PTS Cycles

Ptssel

Programming Considerations for Multiplexed Interrupts

Bit Mnemonic Interrupt PTS Vector

EPA0 EXTINT1 EXTINT0 OVRTM2 OVRTM1

Intmask

Bit Mnemonic Interrupt Standard Vector

EPA3 EPA2 EPA1

Modifying Interrupt Priorities

INTMASK1

NMI EXTINT3 EXTINT2

RET Cseg AT 0FF200CH

Determining the Source of an Interrupt

Intpend

Interrupt Pending Intpend Register

INTPEND1

Initializing the PTS Control Blocks

Single Transfer

PWM Toggle Mode

PWM Remap Mode

Specifying the PTS Count

Ptssrv

Selecting the PTS Mode

EPA3 EPA2 EPA1 EXTINT0 OVRTM1 OVRTM2

Ptscon

Single Transfer Mode

Address Ptspcb +

Ptsdst Ptscb +

PTS Single Transfer Mode Control Block

Ptsdst HI Ptsdst LO Ptssrc HI Ptssrc LO Ptscon Ptscount

Register Location Function

8XC196NP, 80C196NU USER’S Manual

Ptscount = 09H

Block Transfer Mode

Single Transfer Mode Ptscb

Block Transfer Mode Ptscb

Ptsblock Ptscb +

PTS Block Transfer Mode Control Block

Increment the contents of Ptssrc after each byte or word

PTSCONST2

PWM Toggle Mode PWM Remap Mode

PWM Modes

Comparison of PWM Modes

14. a Generic PWM Waveform

PWM Toggle Mode Example

PTSCONST1 HI = T1 HI PTSCONST1 LO = T1 LO PTSPTR1 HI = 1FH

PWM Toggle Mode Ptscb

PTSCONST1 L

PTSCONST2 H

PTSCONST2 L

PTSCONST1 H

Tmod

Ptscon Ptscb +

16. EPA and PTS Operations for the PWM Toggle Mode Example

PWM Remap Mode Example

PWM Remap Mode Ptscb

PTSCONST1 HI PTSCONST1 LO PTSPTR1 HI PTSPTR1 LO Ptscon

PTS PWM Remap Mode Control Block

PWM Tmod

PTS PWM Remap Mode Control Block Register

18. EPA and PTS Operations for the PWM Remap Mode Example

Ports

Page

Port Bits Type

I/O Ports Overview

Bidirectional Ports

Device I/O Ports

Port Pin Special-function Associated Signals

Bidirectional Port Pins

Bidirectional Port Control and Status Registers

Bidirectional Port Operation

8XC196NP, 80C196NU USER’S Manual

Bidirectional Port Structure

Sfdir

Logic Table for Bidirectional Ports in I/O Mode

Bidirectional Port Pin Configurations

Control Register Values for Each Configuration

Bidirectional Port Pin Configuration Example

Port Configuration Example

HZ1

Bidirectional Port Considerations

P2.7/CLKOUT

Eport

Eport Pins

Port Pin Extended-address Signal Type

Design Considerations for External Interrupt Inputs

10. Eport Control and Status Registers

Eport Operation

Eport Block Diagram

Open-drain Output Mode

Reset

Output Enable

Complementary Output Mode

Eport Structure

Epmode Epdir Epreg

Input Mode

11. Logic Table for Eport in I/O Mode

12. Logic Table for Eport in Address Mode

13. Configuration Register Settings for Eport Pins

Configuring Eport Pins

Configuring Eport Pins for Extended-address Functions

Configuring Eport Pins for I/O

Eport Status During Instruction Execution

Eport Considerations

Design Considerations

Page

Serial I/O SIO Port

Page

Serial I/O SIO Port Functional Overview

SIO Block Diagram

Serial

Serial I/O Port Signals and Registers

Serial Port Signals

Serial Port Control and Status Registers

Spbaud 1FBCH,1FBDH

P1REG 1FD4H

Sbufrx 1FB8H

Sbuftx 1FBAH

Serial Port Modes

Synchronous Mode Mode

Spstatus 1FB9H

Asynchronous Modes Modes 1, 2,

Mode 0 Timing

Mode

Serial Port Frames for Mode

Mode 2 and 3 Timings

Serial Port Frames in Mode 2

Programming the Baud Rate and Clock Source

Configuring the Serial Port Pins

Programming the Serial Port

Programming the Control Register

PAR TB8 PRS REN PEN

Spcon

PAR

Spcon

Spbaud

Baud Rate Spbaud Register Value Note Error Mode Mode 1, 2

Spbaud Values When Using the Internal Clock at 25 MHz

8A2BH

8A2CH

Baud Rate Spbaud Register Value † Error Mode

Enabling the Serial Port Interrupts

Determining Serial Port Status

RPE/RB8 TXE

Spstatus

RPE/RB8

Serial I/O SIO Port

Page

Pulse-width Modulator

Page

PWM Functional Overview

PWM Block Diagram 8XC196NP Only

PWM Signals

PWM Signals and Registers

PWM Control and Status Registers

PWM Operation

8XC196NP, 80C196NU USER’S Manual

FFH

Enabled

Programming the Frequency and Period

E6H

CLK1 CLK0

PWM Output Frequencies 8XC196NP

PWM Output Frequencies 80C196NU

CLK0

CLK1 CLK0

Programming the Duty Cycle

CONREG0

FEH

PWM Duty Cycle

Disabled

Clock Prescaler

PWM xCONTROL Address

PWM Output Alternate Functions

PWM Output Alternate Port Function PWM Output Enabled When

Sample Calculations

Enabling the PWM Outputs

D/A Buffer Block Diagram

Event Processor Array EPA

Page

EPA Functional Overview

Chapter Event Processor Array EPA

EPA

EPA and TIMER/COUNTER Signals and Registers

EPA and Timer/Counter Signals

Port Pin EPA Signals

EPA Control and Status Registers

TIMER2

TIMER1

EPA Timer/Counters

TIMER/COUNTER Functional Overview

Quadrature Clocking Mode

Cascade Mode Timer 2 Only

Quadrature Mode Interface Quadrature Mode Truth Table

EPA Channel Functional Overview

Quadrature Mode Timing and Count

A Single EPA Capture/Compare Channel

Operating in Capture Mode

EPA Simplified Input-capture Structure

EPAxCON.0

Action Taken when a Valid Edge Occurs

Action taken when a valid edge occurs

EPA Overruns

Preventing EPA Overruns

Operating in Compare Mode

Generating a Low-speed PWM Output

Generating a Medium-speed PWM Output

Generating a High-speed PWM Output

Generating the Highest-speed PWM Output

Programming the EPA and TIMER/COUNTERS

Configuring the EPA and Timer/Counter Port Pins

Programming the Timers

T1CONTROL

Prescaler Divisor Resolution †

Clock Source Direction Source

T2CONTROL

Prescaler Resolution †

Mode ROT ON/RT

Example Control Register Settings and EPA Operations

Programming the Capture/Compare Channels

= 1 = 0

EPA xCON Address Reset State 00H

ROT ON/RT

Compare Mode Action

Capture Mode Event

Compare Mode RT

Capture Mode on

ROT

Determining Event Status

Enabling the EPA Interrupts

Epamask

Epapend †

12. EPA Interrupt Pending Epapend Register

Programming Examples for EPA Channels

EPA Capture Event Program

Unsigned char Unused Ptscon

EPA PWM Output Program

10-27

Page

Minimum Hardware Considerations

Page

Signal

Minimum Required Signals

Minimum Connections

11.1.2 I/O Port Pin Connections

I/O Port Configuration Guide

Port Where to Find Configuration Information

Unused Inputs

Minimum Hardware Connections

Noise Protection Tips

Applying and Removing Power

On-chip Oscillator Circuit

ON-CHIP Oscillator Circuitry

External Crystal Connections

External Clock Connections

Using AN External Clock Source

Reset Timing Sequence

Resetting the Device

Internal Reset Circuitry

Generating an External Reset

Minimum Reset Circuit

Issuing an Illegal Idlpd Key Operand

Issuing the Reset RST Instruction

Page

Special Operating Modes

Page

Once

Special Operating Mode Signals and Registers

Operating Mode Control Signals

Port Pin Signal Type Description Name

CCR0

Operating Mode Control and Status Registers

Port Pin Signal Type Description

PLLEN21

P2REG 1FD5H

Reducing Power Consumption

P2DIR 1FD3H

P2MODE 1FD1H

Clock Control During Power-saving Modes 8XC196NP

Clock Control During Power-saving Modes 80C196NU

Idle Mode

Enabling and Disabling Standby Mode

Standby Mode 80C196NU only

Entering Standby Mode

Entering Powerdown Mode

Exiting Standby Mode

Powerdown Mode

Enabling and Disabling Powerdown Mode

Generating a Hardware Reset

Exiting Powerdown Mode

Asserting an External Interrupt Signal

External RC Circuit

Selecting C1

Typical Voltage on the RPD Pin While Exiting Powerdown

Reserved Test Modes 80C196NU only

Once Mode

PLLEN2 PLLEN1

C196NU Clock Modes

Page

Interfacing with External Memory

Page

Example of Internal and External Addresses

Internal and External Addresses

Bit Demultiplexed Mode

External Memory Interface Signals

External Memory Interface Signals

Bit Multiplexed Bus Mode

BHE#

Bytes Accessed

Description Multiplexed With

ALE

Ready

Name Type Description Multiplexed With

EA#

Inst

WRL#

CHIP-SELECT Unit

WRH#

Register Address Description Mnemonic

Chip-select Registers

Defining Chip-select Address Ranges

Addrcom Address Reset State

Register Address

Register Address Reset Value

Addrmsk Address Reset State

Address Mbyte Kbyte Bytes

Base Addresses for Several Sizes of the Address Range

FFB00H FFE00H FFD00H FFF00H

Wait States

Buscon Address Reset State

Controlling Wait States, Bus Width, and Bus Multiplexing

WS1 WS0

Chip-select Unit Initial Conditions

BUSCONx Addresses and Reset Values

Initializing the Chip-select Registers

Example of a Chip-select Setup

Buscon

Chip Contents

Sram

Uart

Addrcom Addrmsk

Chip Configuration Registers and Chip Configuration Bytes

Chip Address Size Number Contents

Results for the Chip-select Example

WS1 WS0 Demux BHE#

CCR0

WS0 WS1

Remap MODE64

CCR1

Remap

13-17

BUS Width and Multiplexing

Bit Multiplexed Bus

Bit Demultiplexed Bus

ALE ALE

Bit Demultiplexed Bus

Bit Multiplexed Bus

13.5.1 a 16-bit Example System

CS#

13.5.2 16-bit Bus Timings

Clkout ALE

13.5.3 8-bit Bus Timings

A190 Address AD158 High Address

Wait States Ready Control

Comparison of Multiplexed and Demultiplexed Buses

Bus Description Demultiplexed Bus ns† Multiplexed Bus ns†

Symbol Definition

11. Ready Signal Timing Definitions

BHE#, Inst

Ready ALE

14. Ready Timing Diagram Demultiplexed Mode 8XC196NP

BUS-HOLD Protocol

15. Ready Timing Diagram Demultiplexed Mode 80C196NU

12. HOLD#, HLDA# Timing Definitions

Symbol Parameter

Disabling the Bus-hold Protocol

Enabling the Bus-hold Protocol

Hold Latency

Bus Cycle Type

Regaining Bus Control

WRITE-CONTROL Modes

13. Maximum Hold Latency

Bus Word/Byte Standard Write Strobe

14. Write Signals for Standard and Write Strobe Modes

ALE WR# WRL#

BHE# WRH#

18. Decoding WRL# and WRH#

RD# WRH# WRL#

System BUS AC Timing Specifications

WE# OE#

20. Multiplexed System Bus Timing 8XC196NP

21. Multiplexed System Bus Timing 80C196NU

22. Demultiplexed System Bus Timing 8XC196NP

23. Demultiplexed System Bus Timing 80C196NU

Deferred Bus-cycle Mode 80C196NU Only

24. Deferred Bus-cycle Mode Timing Diagram 80C196NU

Conditions

Explanation of AC Symbols

15. AC Timing Symbol Definitions Signals

AC Timing Definitions

Symbol Definition 8XC196Nx Meets These Specifications

13-44

13-45

Page

Instruction Set Reference

Page

Appendix a Instruction SET Reference

Opcode

Table A-1. Opcode Map Left Half

Table A-1. Opcode Map Right Half

Instruction Quotient Stored Flag Set if Quotient is

Table A-2. Processor Status Word PSW Flags

Mnemonic Description

Value of Bits Shifted Off

Symbol Description

Table A-4. PSW Flag Setting Symbols

Instruction Jumps to Destination if Continues if

Variable Description

Table A-5. Operand Variables

C V VT ST

PSW Flag Settings

Table A-6. Instruction Set

Mnemonic Operation

Dest ← Dest and SRC

Instruction Format

Andb

PTRS, Cntreg

PC ← Dest

Mnemonic Operation Instruction Format

Count ← Count

Dest

Clear WORD. Clears the value

Compare BYTES. Subtracts the source

Dest MOD SRC

Djnz Decrement and Jump if not Zero

← Dest MOD SRC

Djnzw Decrement and Jump if not Zero

Dpts Disable Peripheral Transaction

EBR

Ebmovi Extended Interruptable Block PTRS, Cntreg

Count ← Cntreg

Dstptr ← Ptrs + Dstptr ← Srcptr Ptrs ← Srcptr +

Onto the stack, then adds to the program

Epts Enable Peripheral Transaction

EXT SIGN-EXTEND Integer Into Long

SRC, Dest

Extb SIGN-EXTEND SHORT-INTEGER Into

Increment WORD. Increments the value Word operand by

JGE Jump if Signed Greater than or

JLE Jump if Signed Less than or Equal

Negative flag is set, this instruction adds

JNV Jump if Overflow Flag is Clear

Jnvt Jump if OVERFLOW-TRAP Flag is

JVT Jump if OVERFLOW-TRAP Flag is SET

Mbyte mode

Kbyte mode

Mulb

MUL

Mulu

Negate INTEGER. Negates the value

Dest ← Dest PSW Flag Settings

Mulub

NEG

Dest ← not Dest

Dest ← Dest or SRC

PSW/INTMASK ← SP

INTMASK1/WSR ← SP

SP ← INTMASK1/WSR INTMASK1 ←

SP ← PSW/INTMASK PSW/INTMASK ←

Scall

Wreg,#count

SHR

Range of 0 to 31 1FH, inclusive. If

Shral Arithmetic Right Shift Double

Skip

Shrl Logical Right Shift DOUBLE-WORD

SUB

Rightmost operand

Subcb Subtract Bytes with Borrow DEST, SRC

Subb

Subc Subtract Words with Borrow DEST, SRC

Subc

Index and #MASK = Offset × Offset + Tbase = Dest PC ← Dest

Tijmp TBASE, INDEX, #MASK

SRC

Dest ← Dest XOR SRC

XOR

Decb Extb Incb Shrb Shlb Shrab

Table A-7. Instruction Opcodes

Hex Code Instruction Mnemonic

Clrb Notb Negb

Hex Code

Instruction SET Reference

8XC196NP, 80C196NU USER’S Manual

ST Direct

ELD Indirect

Arithmetic Group Direct Immediate Indirect Indexed Mnemonic

Table A-8. Instruction Lengths and Hexadecimal Opcodes

Subc Subcb

Logical Direct Immediate Indirect

Opcode Length

Stack Direct Immediate Indirect Indexed Mnemonic

POP Popa Popf Push Pusha Pushf

Direct Immediate

Data Direct Immediate

Extended

Ebmovi ELD Eldb EST Estb

Lcall RET

Jump Direct Immediate

EBR Ejmp

Call Direct Immediate

JGE JGT JLE JLT JNC JNE JNH Jnst JNV Jnvt JST JVT

Djnz Djnzw JBC

PTS

Shift Mnemonic Direct Immediate Indirect Indexed

Length Opcode

Special Mnemonic Direct Immediate Indirect

Mem Reg

Table A-9. Instruction Execution Times in State Times

Arithmetic Group Indirect

Normal Autoinc Short Long Reg Mem

DIV Divb Divu Divub

Mnemonic Direct Immed Normal Autoinc Short Long Reg Mem

Logical

Normal Autoinc Short

Stack Register Indirect

Reg Mem

Autoinc Short Long Reg Mem

Data Mnemonic Extended-indirect Normal

Extended-indexed

Indexed Mnemonic

Ljmp Sjmp Tijmp

Mnemonic Direct Immed

Autoinc Short Long

Indirect Indexed Mnemonic Direct Immed

Mnemonic Direct

Conditional Jump

Mnemonic Short-Indexed

Shift

Immed Indirect Indexed

Special Mnemonic Direct Immed Indirect Indexed

Clrc Clrvt Idlpd

NOP RST Setc Skip

Page

Signal Descriptions

Page

Table B-1 XC196NP and 80C196NU Signals Arranged by Function

Functional Groupings of Signals

X8XC196NP

Figure B-1 XC196NP 100-lead Sqfp Package

Figure B-2 XC196NP 100-lead QFP Package

X8XC196NU

Figure B-3 C196NU 100-lead Sqfp Package

Figure B-4 C196NU 100-lead QFP Package

Column Heading Description Name

Signal Descriptions

Table B-3. Signal Descriptions

Table B-2. Description of Columns of Table B-3

WRH# BREQ#

Byte High Enable†

EXTINT30

VSS

PLLEN1 PLLEN2

VSS if either of the following conditions are true

Asserted only during external memory writes

RESET#

Default Conditions

Table B-4. Definition of Status Symbols

RESET# NP/NU

BHE# WK1

Ready WK1 RESET# RPD

WK1 EPORT.30

ALE WK0

Registers

Page

Interrupts

Chip Configuration

Table C-1. Modules and Related Registers

CPU EPA

Table C-2. Register Name, Address, and Reset Status

1FD6H Xxxx P1REG

EPA3CON

EPA2TIME

EPA3TIME

WSR1 NU

Xxxx Spbaud

ACC0x

Table C-3. ACC0x Addresses and Reset Values

ACC0x

Accstat

Table C-4. Effect of SME and FME Bit Combinations

ADDRCOMx

Table C-5. ADDRCOMx Addresses and Reset Values

Addrcom Address

ADDRMSKx Address Table C-6 Reset State

Table C-6. ADDRMSKx Addresses and Reset Values

ADDRMSKx

BUSCONx

Table C-7. BUSCONx Addresses and Reset Values

Buscon Address

CCR0

CCR1

CONREG0

PIN3 PIN2 PIN1 PIN0

Epdir

Epmode

XXH

Eppin

X0H

Epreg

Epamask

Epapend

Epapend

EPA xCON Address

EPAxCON

EPAxCON Address Table C-8

Bit Function Number

Table C-8. EPAxCON Addresses and Reset Values

EPAxTIME

Table C-9. EPAxTIME Addresses and Reset Values

Intmask

FF203EH EXTINT3

INTMASK1

FF203CH EXTINT2

Intpend

INTPEND1

150 One These bits are always equal to Ffffh

Onesreg

Onesreg

Ffffh

PIN7 PIN6 PIN5 PIN4 PIN3 PIN2 PIN1 PIN0

Table C-10. PxDIR Addresses and Reset Values

PxDIR

XDIR Address

Table C-12. Special-function Signals for Ports

Table C-11. PxMODE Addresses and Reset Values

PxMODE

Bit Number

Table C-13. PxPIN Addresses and Reset Values

PxPIN

XPIN Address

P1REG 1FD4H FFH P2REG 1FD5H P3REG 1FDCH P4REG 1FDDH

Table C-14. PxREG Addresses and Reset Values

PxREG

PxREG Address Table C-14

PSW

PSW

PSE

PSW

Ptssel

FF200AH EXTINT1

Ptssrv

PWMxCONTROL

Table C-15. PWMxCONTROL Addresses and Reset Values

Sbufrx

Sbufrx

Data Received

Sbuftx

Sbuftx

Data to Transmit

Xxxxh

Spbaud

Baud Rate Spbaud Register Value Note Error Mode

Spcon

Spstatus

T1CONTROL

T2CONTROL

Table C-17. TIMERx Addresses and Reset Values

TIMERx

Timer Address

Mnemonic Location

WSR

Byte Windows

Register Memory 00E0-00FFH

Register Memory 00E0-00FFH 00C0-00FFH

PWM1CONTROL 1FB2H 7DH

TIMER1 †

TIMER2 †

P4DIR 1FDBH 7EH 00FBH 3FH 00DBH 1FH P4MODE 1FD9H

Register Memory 0060-007FH 0040-007FH Mnemonic Location

WSR1

0060-007FH 0040-007FH Mnemonic Location

Spcon 1FBBH 7DH

PWM0CONTROL 1FB0H 7DH

Sbuftx 1FBAH 7DH

Spbaud 1FBCH 7DH

Zeroreg

Zeroreg

150 Zero This register is always equal to zero

Page

Glossary

Page

Glossary

DOUBLE-WORD

FET

ISR

PIC PLL

PTS

SFR

Uart

Index

Page

Index

Index-2

Index-3

Index-4

Index-5

Index-6

Index-7

Index-8

Index-9

Index-10

Index-11

Index-12