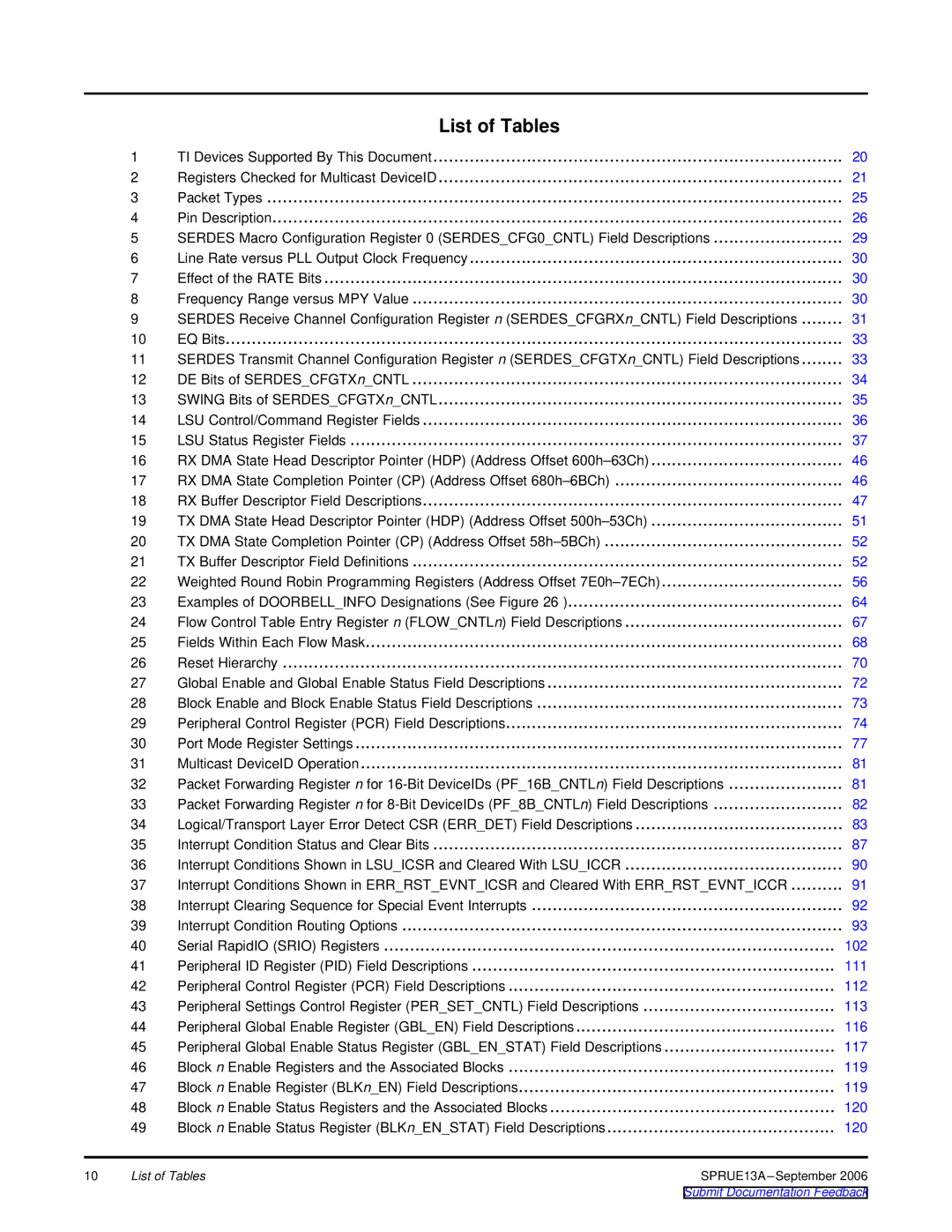

List of Tables

| 1 | TI Devices Supported By This Document | 20 | |

| 2 | Registers Checked for Multicast DeviceID | 21 | |

| 3 | Packet Types | 25 | |

| 4 | Pin Description | 26 | |

| 5 | SERDES Macro Configuration Register 0 (SERDES_CFG0_CNTL) Field Descriptions | 29 | |

| 6 | Line Rate versus PLL Output Clock Frequency | 30 | |

| 7 | Effect of the RATE Bits | 30 | |

| 8 | Frequency Range versus MPY Value | 30 | |

| 9 | SERDES Receive Channel Configuration Register n (SERDES_CFGRXn_CNTL) Field Descriptions | 31 | |

| 10 | EQ Bits | 33 | |

| 11 | SERDES Transmit Channel Configuration Register n (SERDES_CFGTXn_CNTL) Field Descriptions | 33 | |

| 12 | DE Bits of SERDES_CFGTXn_CNTL | 34 | |

| 13 | SWING Bits of SERDES_CFGTXn_CNTL | 35 | |

| 14 | LSU Control/Command Register Fields | 36 | |

| 15 | LSU Status Register Fields | 37 | |

| 16 | RX DMA State Head Descriptor Pointer (HDP) (Address Offset | 46 | |

| 17 | RX DMA State Completion Pointer (CP) (Address Offset | 46 | |

| 18 | RX Buffer Descriptor Field Descriptions | 47 | |

| 19 | TX DMA State Head Descriptor Pointer (HDP) (Address Offset | 51 | |

| 20 | TX DMA State Completion Pointer (CP) (Address Offset | 52 | |

| 21 | TX Buffer Descriptor Field Definitions | 52 | |

| 22 | Weighted Round Robin Programming Registers (Address Offset | 56 | |

| 23 | Examples of DOORBELL_INFO Designations (See Figure 26 ) | 64 | |

| 24 | Flow Control Table Entry Register n (FLOW_CNTLn) Field Descriptions | 67 | |

| 25 | Fields Within Each Flow Mask | 68 | |

| 26 | Reset Hierarchy | 70 | |

| 27 | Global Enable and Global Enable Status Field Descriptions | 72 | |

| 28 | Block Enable and Block Enable Status Field Descriptions | 73 | |

| 29 | Peripheral Control Register (PCR) Field Descriptions | 74 | |

| 30 | Port Mode Register Settings | 77 | |

| 31 | Multicast DeviceID Operation | 81 | |

| 32 | Packet Forwarding Register n for | 81 | |

| 33 | Packet Forwarding Register n for | 82 | |

| 34 | Logical/Transport Layer Error Detect CSR (ERR_DET) Field Descriptions | 83 | |

| 35 | Interrupt Condition Status and Clear Bits | 87 | |

| 36 | Interrupt Conditions Shown in LSU_ICSR and Cleared With LSU_ICCR | 90 | |

| 37 | Interrupt Conditions Shown in ERR_RST_EVNT_ICSR and Cleared With ERR_RST_EVNT_ICCR | 91 | |

| 38 | Interrupt Clearing Sequence for Special Event Interrupts | 92 | |

| 39 | Interrupt Condition Routing Options | 93 | |

| 40 | Serial RapidIO (SRIO) Registers | 102 | |

| 41 | Peripheral ID Register (PID) Field Descriptions | 111 | |

| 42 | Peripheral Control Register (PCR) Field Descriptions | 112 | |

| 43 | Peripheral Settings Control Register (PER_SET_CNTL) Field Descriptions | 113 | |

| 44 | Peripheral Global Enable Register (GBL_EN) Field Descriptions | 116 | |

| 45 | Peripheral Global Enable Status Register (GBL_EN_STAT) Field Descriptions | 117 | |

| 46 | Block n Enable Registers and the Associated Blocks | 119 | |

| 47 | Block n Enable Register (BLKn_EN) Field Descriptions | 119 | |

| 48 | Block n Enable Status Registers and the Associated Blocks | 120 | |

| 49 | Block n Enable Status Register (BLKn_EN_STAT) Field Descriptions | 120 | |

10 | List of Tables | SPRUE13A | ||