www.ti.com

SRIO Registers

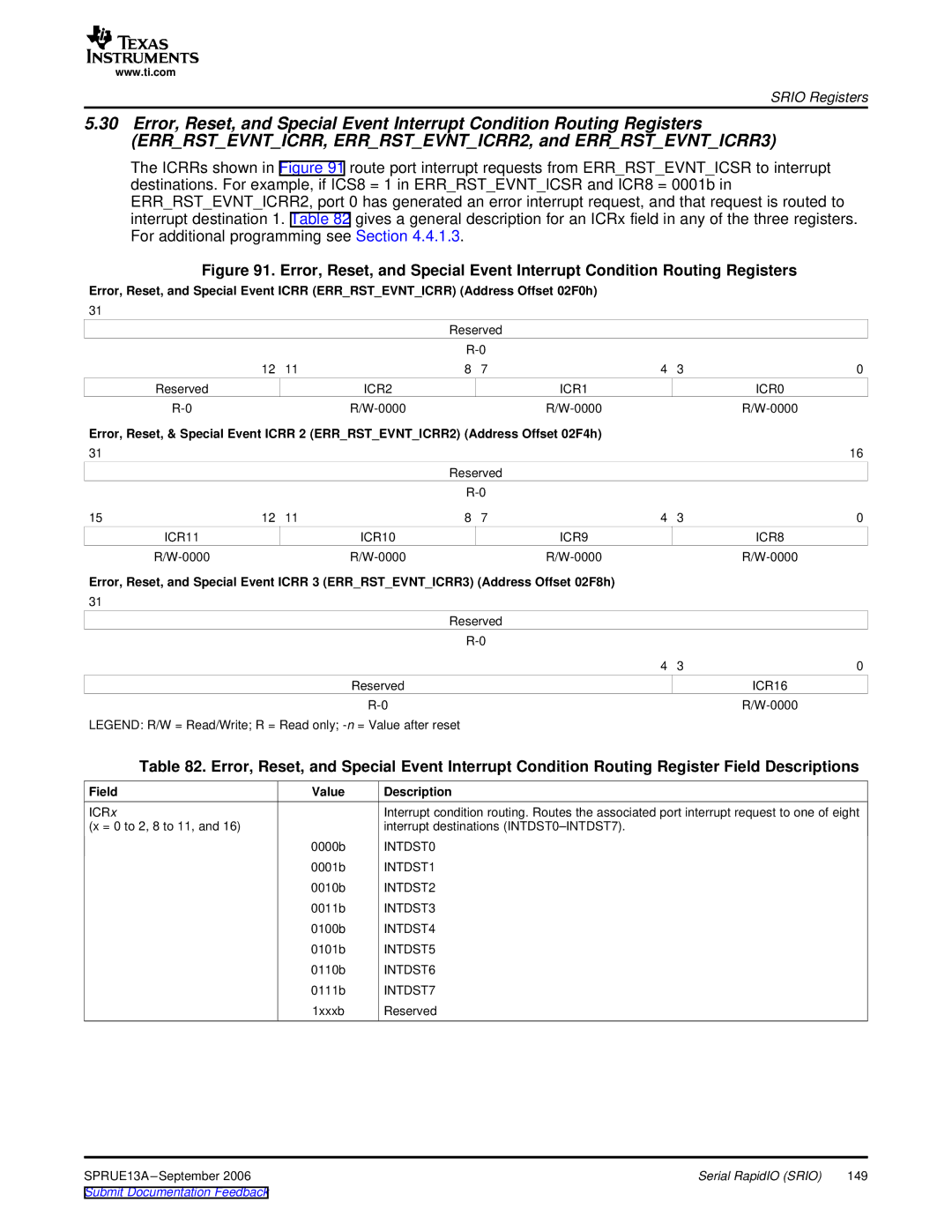

5.30 Error, Reset, and Special Event Interrupt Condition Routing Registers (ERR_RST_EVNT_ICRR, ERR_RST_EVNT_ICRR2, and ERR_RST_EVNT_ICRR3)

The ICRRs shown in Figure 91 route port interrupt requests from ERR_RST_EVNT_ICSR to interrupt destinations. For example, if ICS8 = 1 in ERR_RST_EVNT_ICSR and ICR8 = 0001b in ERR_RST_EVNT_ICRR2, port 0 has generated an error interrupt request, and that request is routed to interrupt destination 1. Table 82 gives a general description for an ICRx field in any of the three registers. For additional programming see Section 4.4.1.3.

Figure 91. Error, Reset, and Special Event Interrupt Condition Routing Registers

Error, Reset, and Special Event ICRR (ERR_RST_EVNT_ICRR) (Address Offset 02F0h)

31 |

|

|

|

|

|

|

|

|

|

| Reserved |

|

|

| |

|

|

|

|

|

| ||

| 12 | 11 | 8 | 7 | 4 | 3 | 0 |

| Reserved |

| ICR2 |

| ICR1 |

| ICR0 |

|

|

|

| ||||

Error, Reset, & Special Event ICRR 2 (ERR_RST_EVNT_ICRR2) (Address Offset 02F4h) |

|

| |||||

31 |

|

|

|

|

|

| 16 |

|

|

| Reserved |

|

|

| |

|

|

|

|

|

| ||

15 | 12 | 11 | 8 | 7 | 4 | 3 | 0 |

| ICR11 |

| ICR10 |

| ICR9 |

| ICR8 |

|

|

|

| ||||

Error, Reset, and Special Event ICRR 3 (ERR_RST_EVNT_ICRR3) (Address Offset 02F8h) |

|

| |||||

31 |

|

|

|

|

|

|

|

|

|

| Reserved |

|

|

| |

|

|

|

|

|

| ||

|

|

|

|

| 4 | 3 | 0 |

|

|

| Reserved |

|

|

| ICR16 |

|

|

|

|

|

| ||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

|

| |||

Table 82. Error, Reset, and Special Event Interrupt Condition Routing Register Field Descriptions

Field | Value | Description |

ICRx |

| Interrupt condition routing. Routes the associated port interrupt request to one of eight |

(x = 0 to 2, 8 to 11, and 16) |

| interrupt destinations |

| 0000b | INTDST0 |

| 0001b | INTDST1 |

| 0010b | INTDST2 |

| 0011b | INTDST3 |

| 0100b | INTDST4 |

| 0101b | INTDST5 |

| 0110b | INTDST6 |

| 0111b | INTDST7 |

| 1xxxb | Reserved |

SPRUE13A | Serial RapidIO (SRIO) | 149 |