www.ti.com

SRIO Registers

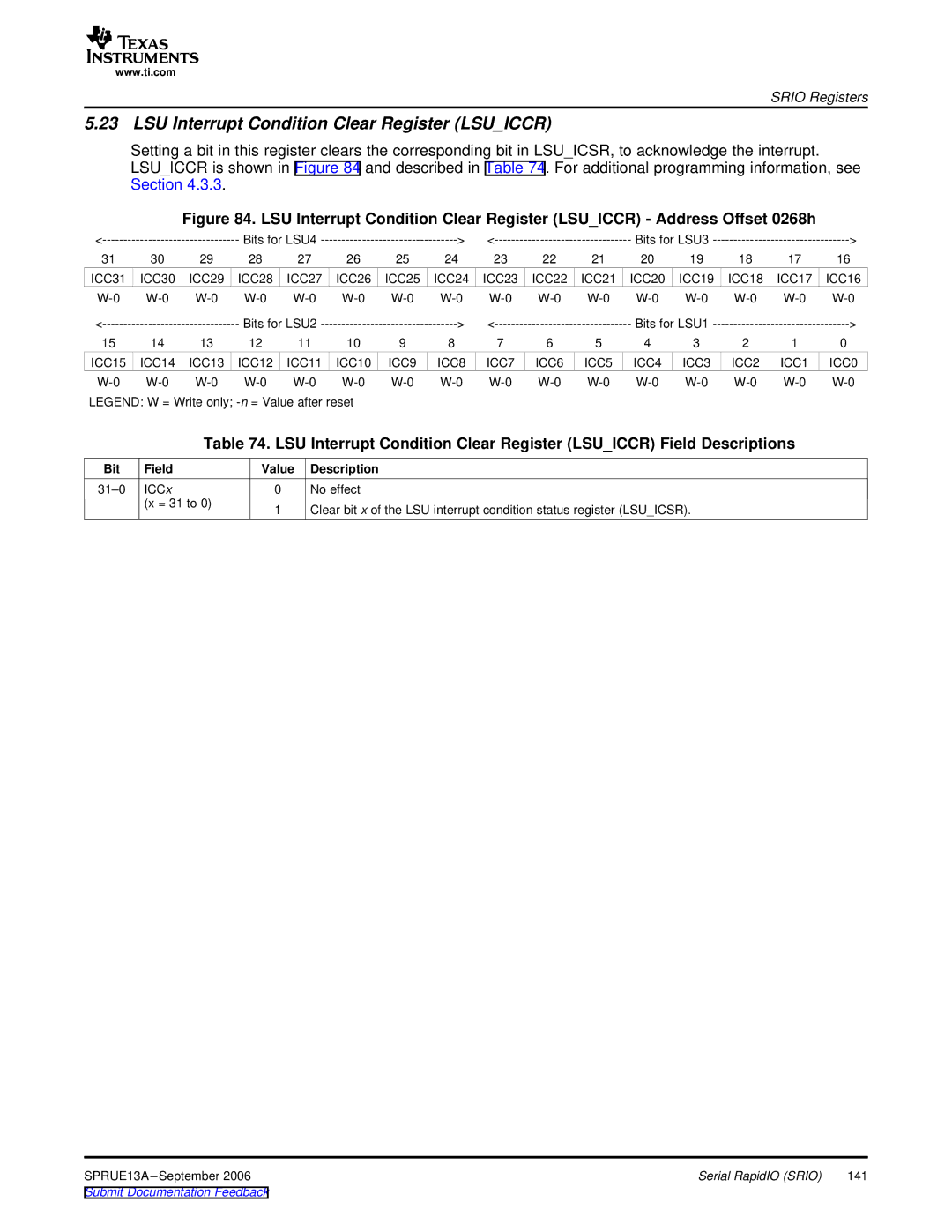

5.23 LSU Interrupt Condition Clear Register (LSU_ICCR)

Setting a bit in this register clears the corresponding bit in LSU_ICSR, to acknowledge the interrupt.

LSU_ICCR is shown in Figure 84 and described in Table 74. For additional programming information, see Section 4.3.3.

Figure 84. LSU Interrupt Condition Clear Register (LSU_ICCR) - Address Offset 0268h

| Bits for LSU4 |

| > |

| Bits for LSU3 |

| > | ||||||||

31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

ICC31 | ICC30 | ICC29 | ICC28 | ICC27 | ICC26 | ICC25 | ICC24 | ICC23 | ICC22 | ICC21 | ICC20 | ICC19 | ICC18 | ICC17 | ICC16 |

| Bits for LSU2 |

| > |

| Bits for LSU1 |

| > | ||||||||

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

ICC15 | ICC14 | ICC13 | ICC12 | ICC11 | ICC10 | ICC9 | ICC8 | ICC7 | ICC6 | ICC5 | ICC4 | ICC3 | ICC2 | ICC1 | ICC0 |

LEGEND: W = Write only;

Table 74. LSU Interrupt Condition Clear Register (LSU_ICCR) Field Descriptions

Bit | Field | Value | Description |

ICCx | 0 | No effect | |

| (x = 31 to 0) | 1 | Clear bit x of the LSU interrupt condition status register (LSU_ICSR). |

|

|

SPRUE13A | Serial RapidIO (SRIO) | 141 |

Submit Documentation Feedback |

|

|