www.ti.com

SRIO Registers

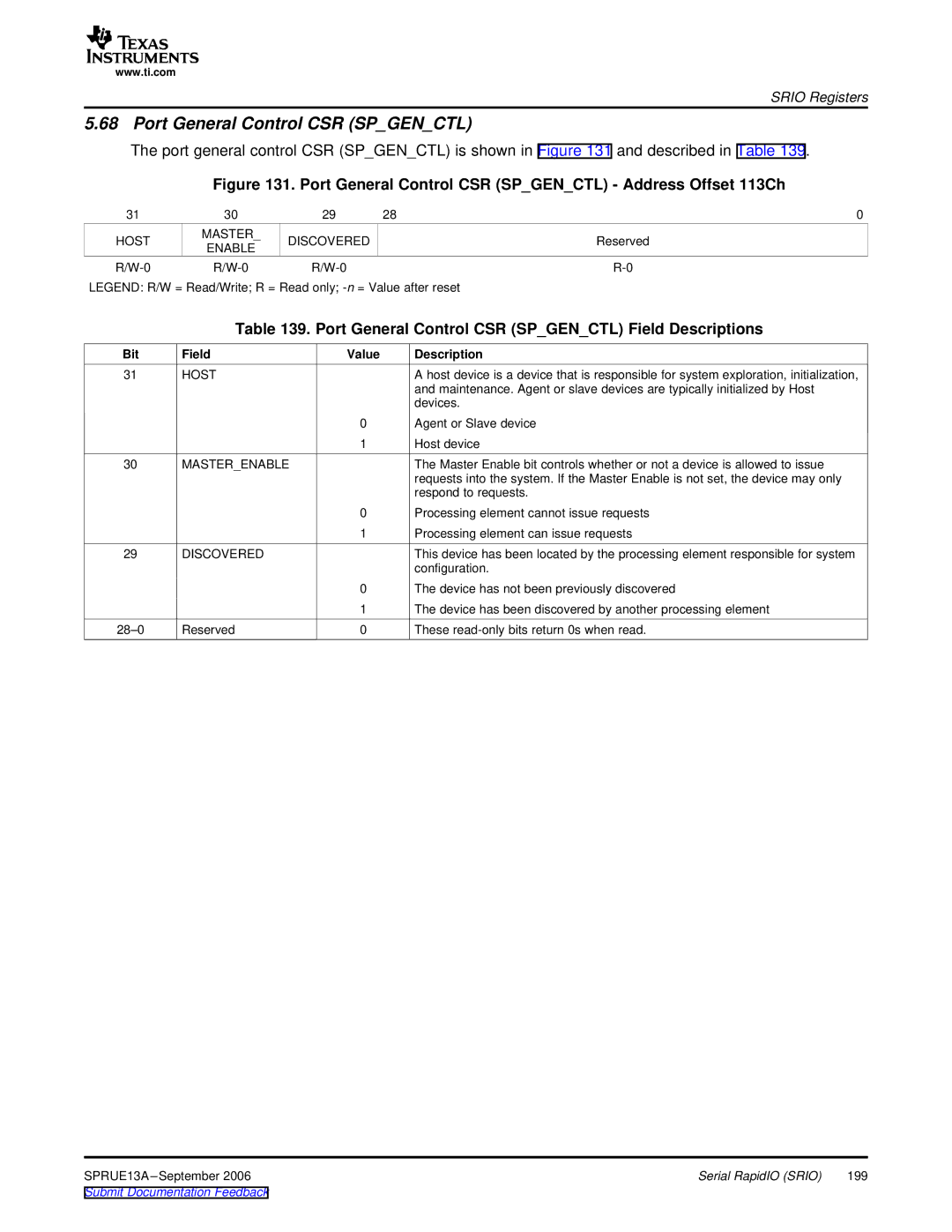

5.68 Port General Control CSR (SP_GEN_CTL)

The port general control CSR (SP_GEN_CTL) is shown in Figure 131 and described in Table 139.

Figure 131. Port General Control CSR (SP_GEN_CTL) - Address Offset 113Ch

31 | 30 | 29 | 28 | 0 |

HOST | MASTER_ | DISCOVERED |

| Reserved |

ENABLE |

| |||

|

|

|

| |

|

LEGEND: R/W = Read/Write; R = Read only;

Table 139. Port General Control CSR (SP_GEN_CTL) Field Descriptions

Bit | Field | Value | Description |

31 | HOST |

| A host device is a device that is responsible for system exploration, initialization, |

|

|

| and maintenance. Agent or slave devices are typically initialized by Host |

|

|

| devices. |

|

| 0 | Agent or Slave device |

|

| 1 | Host device |

30 | MASTER_ENABLE |

| The Master Enable bit controls whether or not a device is allowed to issue |

|

|

| requests into the system. If the Master Enable is not set, the device may only |

|

|

| respond to requests. |

|

| 0 | Processing element cannot issue requests |

|

| 1 | Processing element can issue requests |

29 | DISCOVERED |

| This device has been located by the processing element responsible for system |

|

|

| configuration. |

|

| 0 | The device has not been previously discovered |

|

| 1 | The device has been discovered by another processing element |

Reserved | 0 | These |

SPRUE13A | Serial RapidIO (SRIO) | 199 |

Submit Documentation Feedback |

|

|