www.ti.com

SRIO Registers

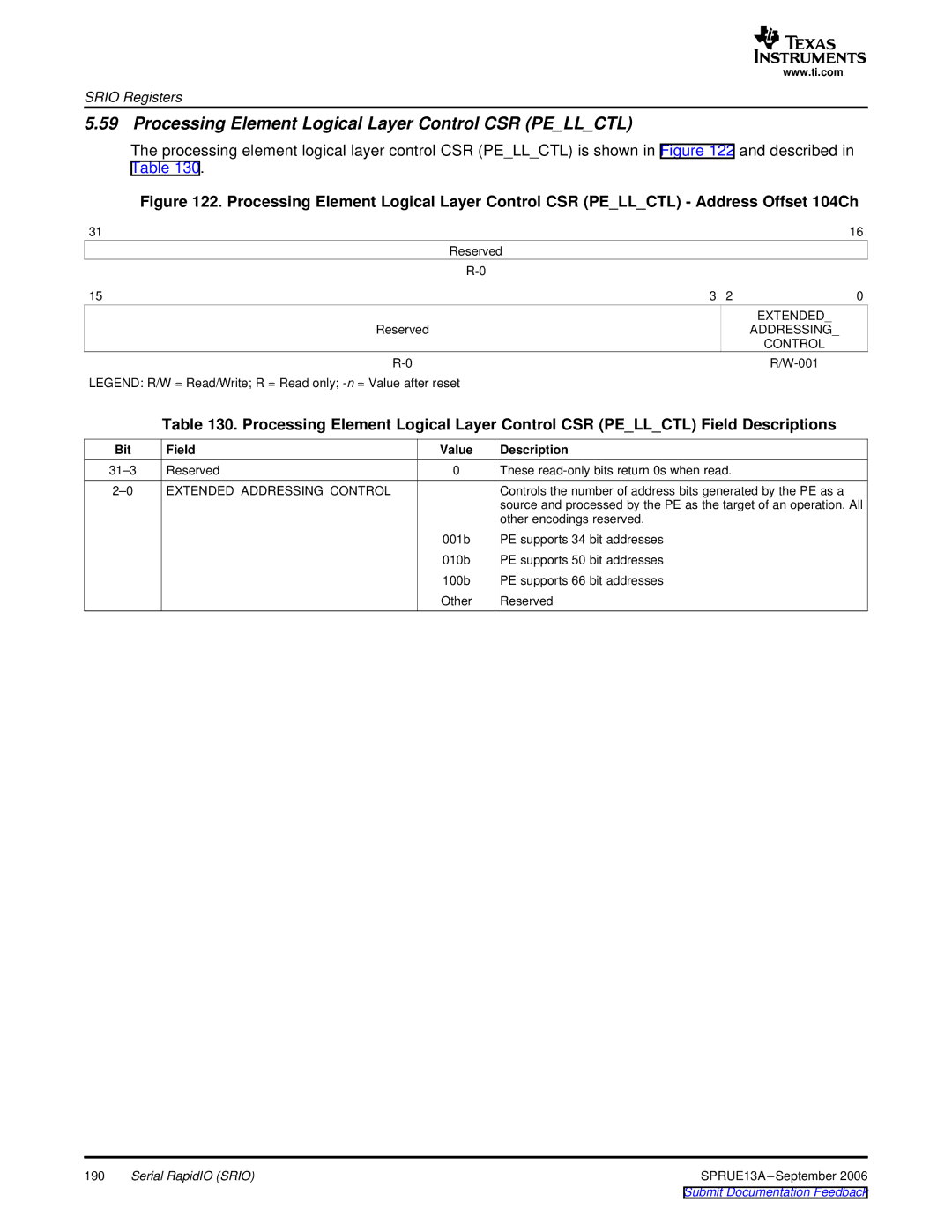

5.59 Processing Element Logical Layer Control CSR (PE_LL_CTL)

The processing element logical layer control CSR (PE_LL_CTL) is shown in Figure 122 and described in Table 130.

Figure 122. Processing Element Logical Layer Control CSR (PE_LL_CTL) - Address Offset 104Ch

31 |

|

| 16 |

Reserved |

|

|

|

|

|

| |

15 | 3 | 2 | 0 |

|

|

| EXTENDED_ |

Reserved |

|

| ADDRESSING_ |

|

|

| CONTROL |

|

| ||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

|

Table 130. Processing Element Logical Layer Control CSR (PE_LL_CTL) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | These | |

EXTENDED_ADDRESSING_CONTROL |

| Controls the number of address bits generated by the PE as a | |

|

|

| source and processed by the PE as the target of an operation. All |

|

|

| other encodings reserved. |

|

| 001b | PE supports 34 bit addresses |

|

| 010b | PE supports 50 bit addresses |

|

| 100b | PE supports 66 bit addresses |

|

| Other | Reserved |

190 | Serial RapidIO (SRIO) | SPRUE13A |