www.ti.com

SRIO Registers

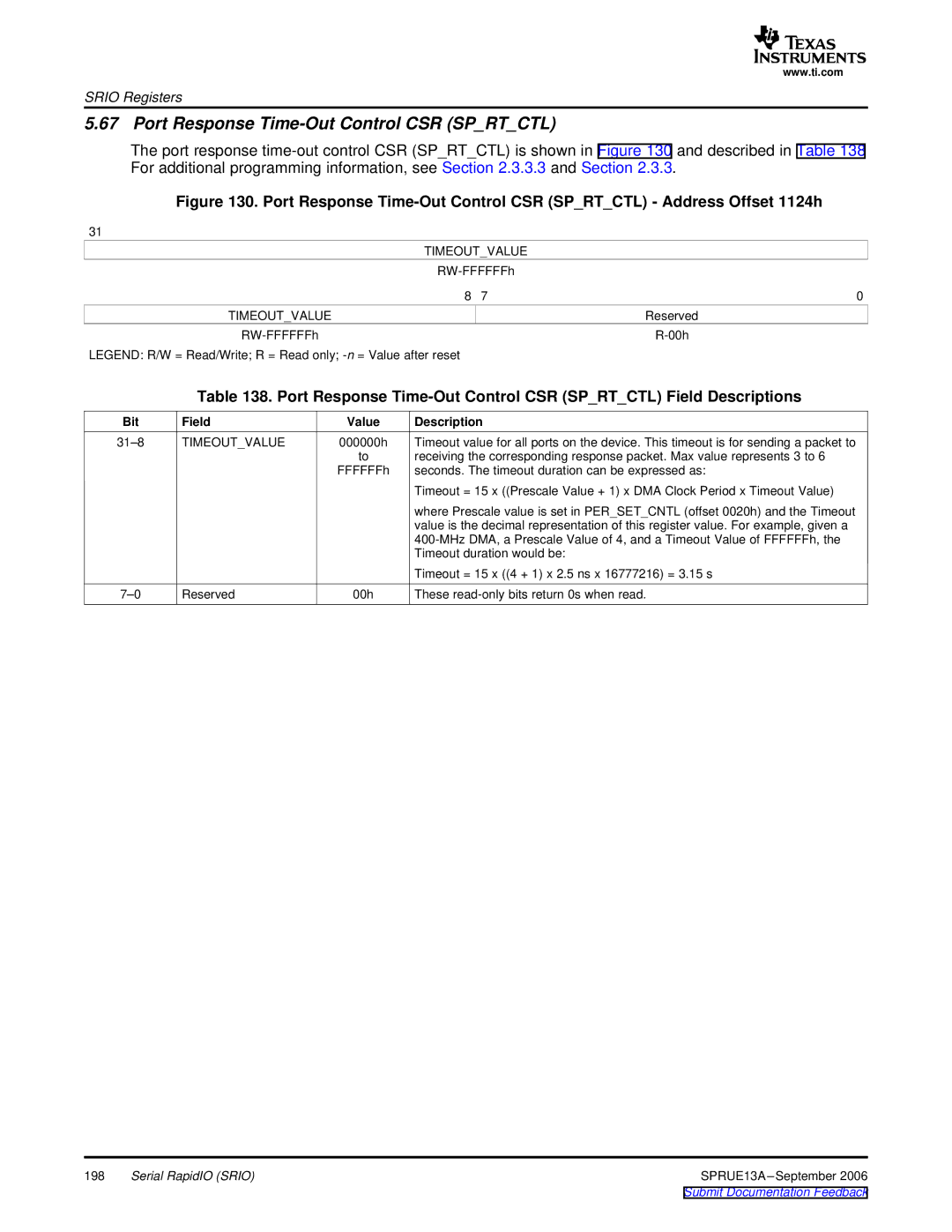

5.67 Port Response Time-Out Control CSR (SP_RT_CTL)

The port response

Figure 130. Port Response Time-Out Control CSR (SP_RT_CTL) - Address Offset 1124h

31

TIMEOUT_VALUE

8 | 7 | 0 |

TIMEOUT_VALUE |

| Reserved |

|

LEGEND: R/W = Read/Write; R = Read only;

Table 138. Port Response

Bit | Field | Value | Description |

TIMEOUT_VALUE | 000000h | Timeout value for all ports on the device. This timeout is for sending a packet to | |

|

| to | receiving the corresponding response packet. Max value represents 3 to 6 |

|

| FFFFFFh | seconds. The timeout duration can be expressed as: |

|

|

| Timeout = 15 x ((Prescale Value + 1) x DMA Clock Period x Timeout Value) |

|

|

| where Prescale value is set in PER_SET_CNTL (offset 0020h) and the Timeout |

|

|

| value is the decimal representation of this register value. For example, given a |

|

|

| |

|

|

| Timeout duration would be: |

|

|

| Timeout = 15 x ((4 + 1) x 2.5 ns x 16777216) = 3.15 s |

Reserved | 00h | These |

198 | Serial RapidIO (SRIO) | SPRUE13A |