www.ti.com

SRIO Functional Description

Table 9. SERDES Receive Channel Configuration Register n (SERDES_CFGRXn_CNTL) Field

Descriptions (continued)

Bit | Field | Value | Description |

BUSWIDTH | 000b | Bus width. Always write 000b to this field, to indicate a | |

|

|

| the clock. All other values are reserved. See Section 2.3.2.1 for an explanation of |

|

|

| the bus. |

1 | Reserved | 0 | Always write 0 to this reserved bit. |

0 | ENRX |

| Enable receiver |

|

| 0 | Disable this receiver. |

|

| 1 | Enable this receiver. |

Table 10. EQ Bits

| Low Freq Gain | Zero Freq (at e28 (min)) |

0000b | Maximum | – |

0001b | Adaptive | Adaptive |

001xb |

| Reserved |

01xxb |

| Reserved |

1000b | Adaptive | 1084MHz |

1001b |

| 805MHz |

1010b |

| 573MHz |

1011b |

| 402MHz |

1100b |

| 304MHz |

1101b |

| 216MHz |

1110b |

| 156MHz |

1111b |

| 135MHz |

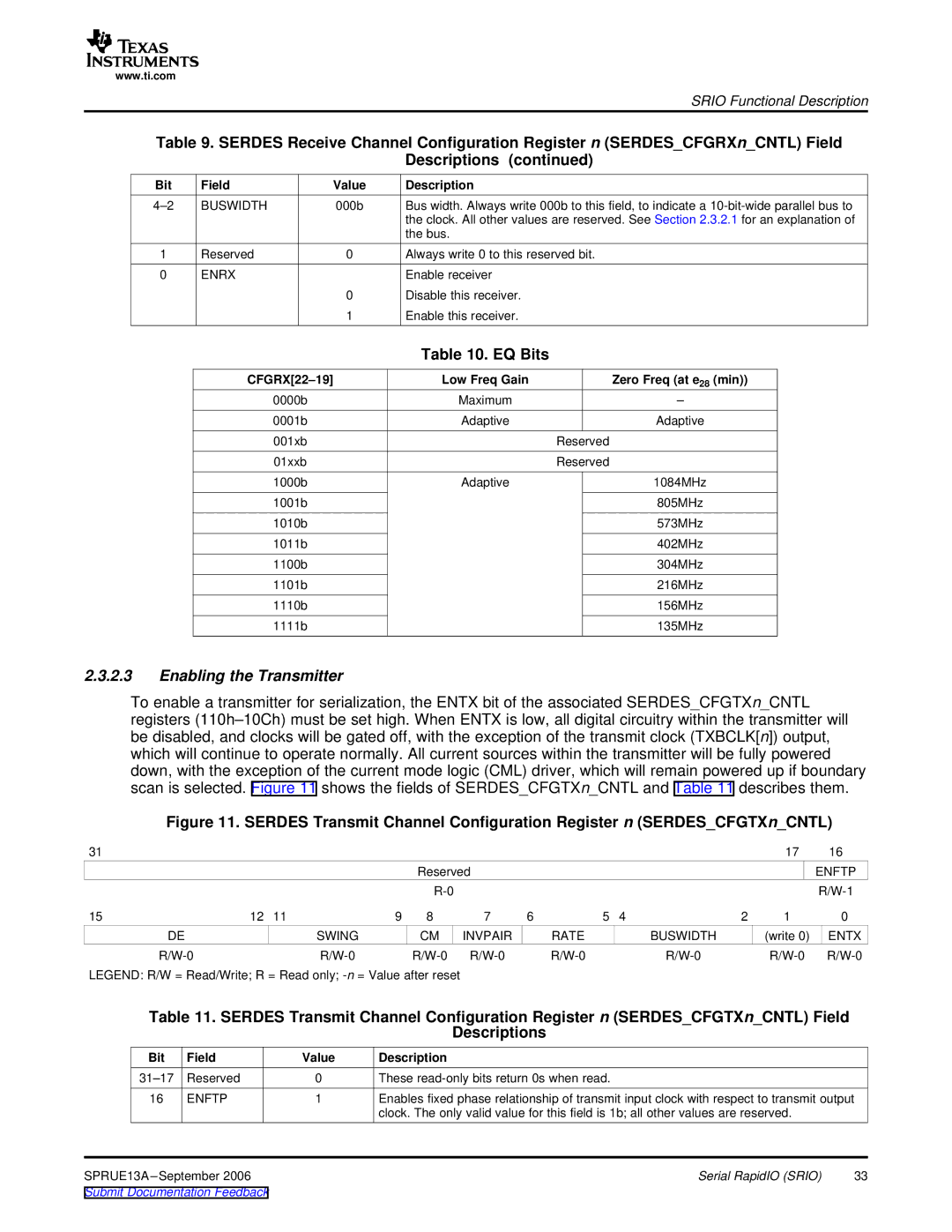

2.3.2.3Enabling the Transmitter

To enable a transmitter for serialization, the ENTX bit of the associated SERDES_CFGTXn_CNTL registers

Figure 11. SERDES Transmit Channel Configuration Register n (SERDES_CFGTXn_CNTL)

31 |

|

|

|

|

|

|

|

|

| 17 | 16 |

|

|

|

| Reserved |

|

|

|

|

| ENFTP | |

|

|

|

|

|

|

|

|

|

| ||

15 | 12 | 11 | 9 | 8 | 7 | 6 | 5 | 4 | 2 | 1 | 0 |

DE |

| SWING |

| CM | INVPAIR |

| RATE |

| BUSWIDTH | (write 0) | ENTX |

|

|

|

| ||||||||

LEGEND: R/W = Read/Write; R = Read only;

Table 11. SERDES Transmit Channel Configuration Register n (SERDES_CFGTXn_CNTL) Field

Descriptions

Bit | Field | Value | Description |

|

Reserved | 0 | These |

| |

16 | ENFTP | 1 | Enables fixed phase relationship of transmit input clock with respect to transmit output | |

|

|

| clock. The only valid value for this field is 1b; all other values are reserved. |

|

SPRUE13A |

| Serial RapidIO (SRIO) | 33 | |

Submit Documentation Feedback |

|

|

| |