www.ti.com

SRIO Registers

5.83 Port Error Rate Enable CSR n (SPn_RATE_EN)

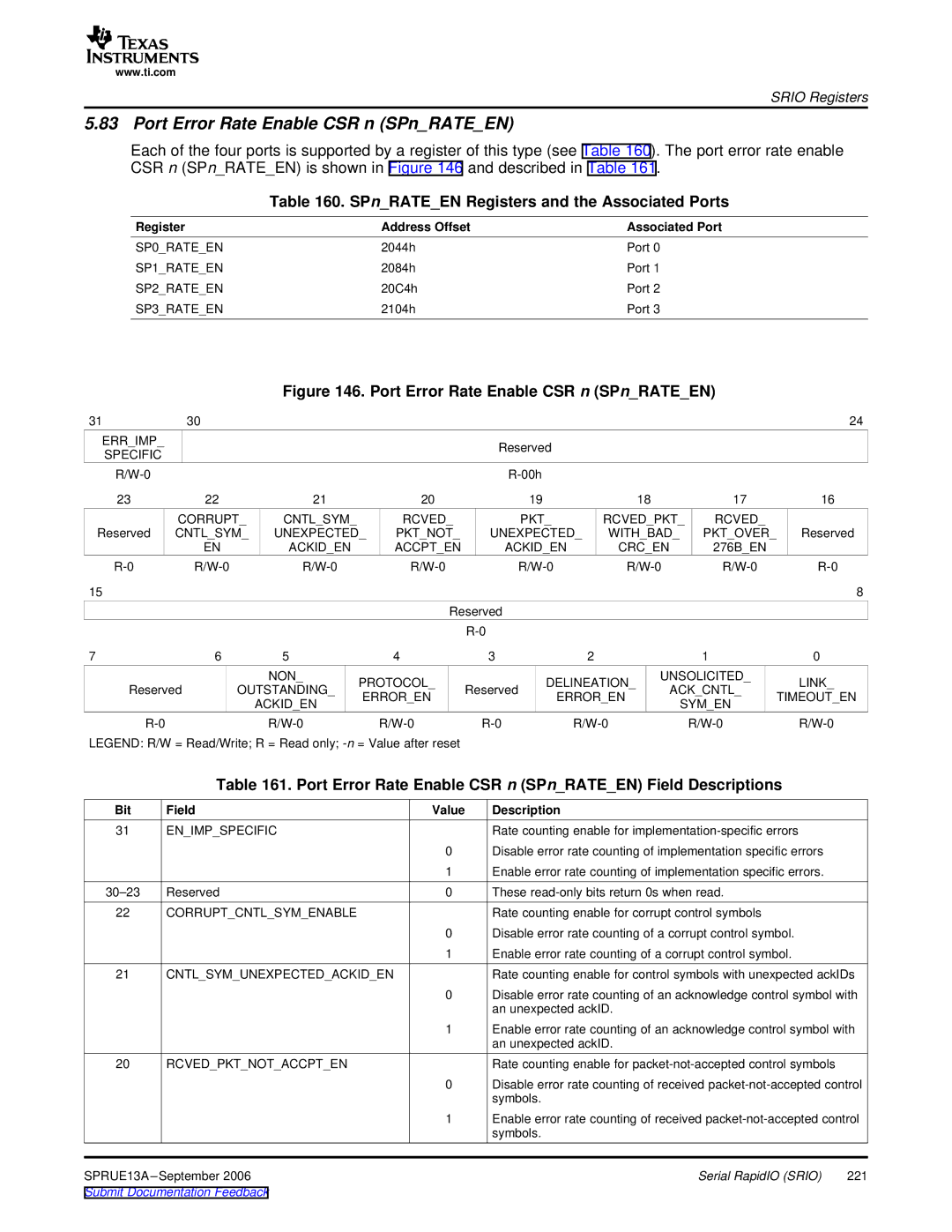

Each of the four ports is supported by a register of this type (see Table 160). The port error rate enable CSR n (SPn_RATE_EN) is shown in Figure 146 and described in Table 161.

Table 160. SPn_RATE_EN Registers and the Associated Ports

Register | Address Offset | Associated Port |

SP0_RATE_EN | 2044h | Port 0 |

SP1_RATE_EN | 2084h | Port 1 |

SP2_RATE_EN | 20C4h | Port 2 |

SP3_RATE_EN | 2104h | Port 3 |

|

| Figure 146. Port Error Rate Enable CSR n (SPn_RATE_EN) |

| ||||||||||

31 | 30 |

|

|

|

|

|

|

|

|

|

|

| 24 |

ERR_IMP_ |

|

|

|

| Reserved |

|

|

|

|

|

|

| |

SPECIFIC |

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| |||

23 | 22 | 21 |

| 20 |

| 19 |

|

|

| 18 |

| 17 | 16 |

CORRUPT_ | CNTL_SYM_ |

| RCVED_ |

| PKT_ |

|

| RCVED_PKT_ | RCVED_ |

| |||

Reserved CNTL_SYM_ | UNEXPECTED_ | PKT_NOT_ | UNEXPECTED_ | WITH_BAD_ | PKT_OVER_ Reserved | ||||||||

| EN | ACKID_EN |

| ACCPT_EN | ACKID_EN |

| CRC_EN |

| 276B_EN |

| |||

|

|

|

|

| |||||||||

15 |

|

|

|

|

|

|

|

|

|

|

|

| 8 |

|

|

|

| Reserved |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| |

7 | 6 | 5 |

| 4 | 3 |

|

|

| 2 |

|

| 1 | 0 |

|

| NON_ | PROTOCOL_ |

| DELINEATION_ | UNSOLICITED_ | LINK_ | ||||||

Reserved | OUTSTANDING_ | Reserved |

| ACK_CNTL_ | |||||||||

ERROR_EN |

| ERROR_EN |

| TIMEOUT_EN | |||||||||

|

| ACKID_EN |

|

|

| SYM_EN | |||||||

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

| ||||||||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

|

|

|

|

|

|

| ||||

Table 161. Port Error Rate Enable CSR n (SPn_RATE_EN) Field Descriptions

Bit | Field | Value | Description |

|

31 | EN_IMP_SPECIFIC |

| Rate counting enable for |

|

|

| 0 | Disable error rate counting of implementation specific errors |

|

|

| 1 | Enable error rate counting of implementation specific errors. |

|

Reserved | 0 | These |

| |

22 | CORRUPT_CNTL_SYM_ENABLE |

| Rate counting enable for corrupt control symbols |

|

|

| 0 | Disable error rate counting of a corrupt control symbol. |

|

|

| 1 | Enable error rate counting of a corrupt control symbol. |

|

21 | CNTL_SYM_UNEXPECTED_ACKID_EN |

| Rate counting enable for control symbols with unexpected ackIDs | |

|

| 0 | Disable error rate counting of an acknowledge control symbol with | |

|

|

| an unexpected ackID. |

|

|

| 1 | Enable error rate counting of an acknowledge control symbol with | |

|

|

| an unexpected ackID. |

|

20 | RCVED_PKT_NOT_ACCPT_EN |

| Rate counting enable for |

|

|

| 0 | Disable error rate counting of received | |

|

|

| symbols. |

|

|

| 1 | Enable error rate counting of received | |

|

|

| symbols. |

|

SPRUE13A |

| Serial RapidIO (SRIO) | 221 | |

Submit Documentation Feedback |

|

|

| |