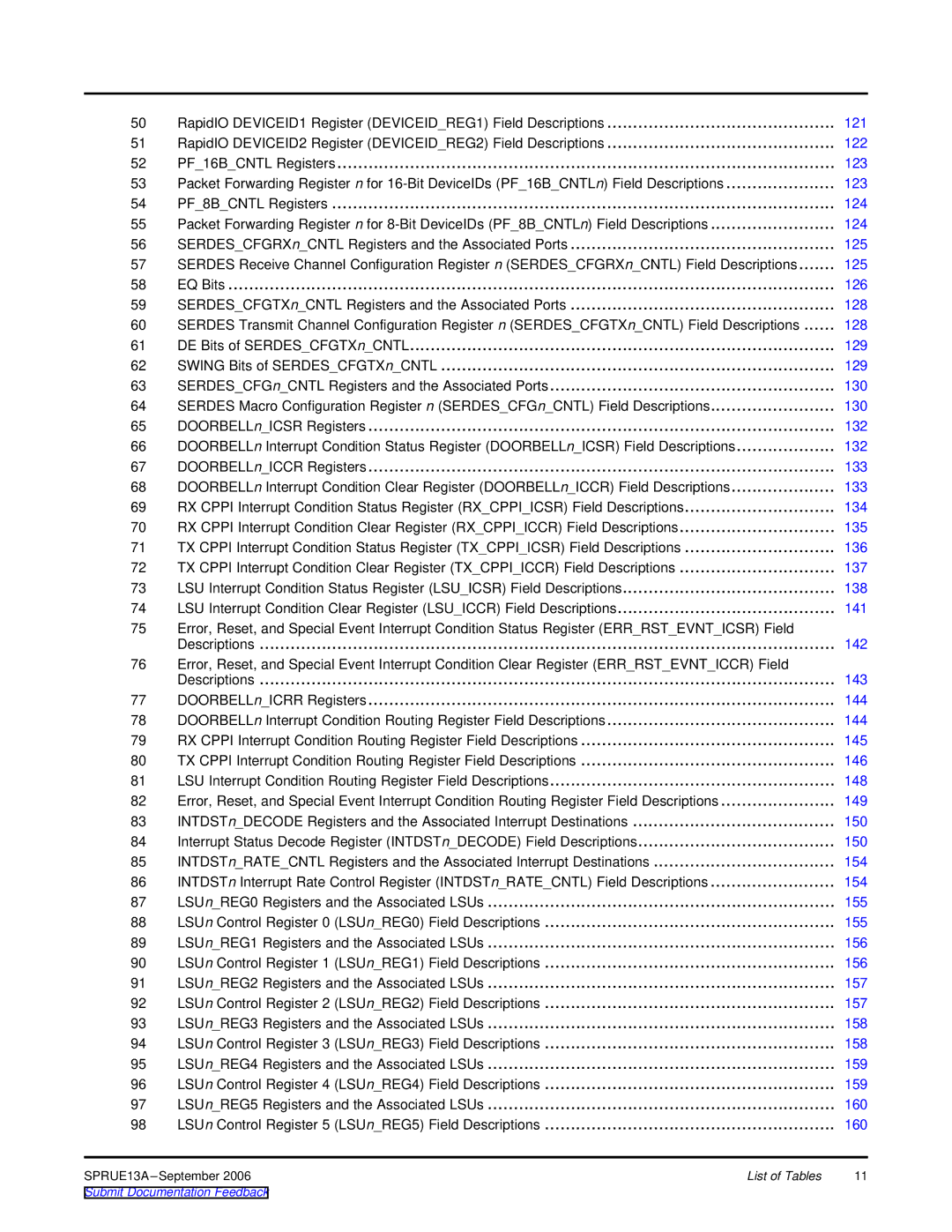

50 | RapidIO DEVICEID1 Register (DEVICEID_REG1) Field Descriptions | 121 | |

51 | RapidIO DEVICEID2 Register (DEVICEID_REG2) Field Descriptions | 122 | |

52 | PF_16B_CNTL Registers | 123 | |

53 | Packet Forwarding Register n for | 123 | |

54 | PF_8B_CNTL Registers | 124 | |

55 | Packet Forwarding Register n for | 124 | |

56 | SERDES_CFGRXn_CNTL Registers and the Associated Ports | 125 | |

57 | SERDES Receive Channel Configuration Register n (SERDES_CFGRXn_CNTL) Field Descriptions | 125 | |

58 | EQ Bits | 126 | |

59 | SERDES_CFGTXn_CNTL Registers and the Associated Ports | 128 | |

60 | SERDES Transmit Channel Configuration Register n (SERDES_CFGTXn_CNTL) Field Descriptions | 128 | |

61 | DE Bits of SERDES_CFGTXn_CNTL | 129 | |

62 | SWING Bits of SERDES_CFGTXn_CNTL | 129 | |

63 | SERDES_CFGn_CNTL Registers and the Associated Ports | 130 | |

64 | SERDES Macro Configuration Register n (SERDES_CFGn_CNTL) Field Descriptions | 130 | |

65 | DOORBELLn_ICSR Registers | 132 | |

66 | DOORBELLn Interrupt Condition Status Register (DOORBELLn_ICSR) Field Descriptions | 132 | |

67 | DOORBELLn_ICCR Registers | 133 | |

68 | DOORBELLn Interrupt Condition Clear Register (DOORBELLn_ICCR) Field Descriptions | 133 | |

69 | RX CPPI Interrupt Condition Status Register (RX_CPPI_ICSR) Field Descriptions | 134 | |

70 | RX CPPI Interrupt Condition Clear Register (RX_CPPI_ICCR) Field Descriptions | 135 | |

71 | TX CPPI Interrupt Condition Status Register (TX_CPPI_ICSR) Field Descriptions | 136 | |

72 | TX CPPI Interrupt Condition Clear Register (TX_CPPI_ICCR) Field Descriptions | 137 | |

73 | LSU Interrupt Condition Status Register (LSU_ICSR) Field Descriptions | 138 | |

74 | LSU Interrupt Condition Clear Register (LSU_ICCR) Field Descriptions | 141 | |

75 | Error, Reset, and Special Event Interrupt Condition Status Register (ERR_RST_EVNT_ICSR) Field |

| |

| Descriptions | 142 | |

76 | Error, Reset, and Special Event Interrupt Condition Clear Register (ERR_RST_EVNT_ICCR) Field |

| |

| Descriptions | 143 | |

77 | DOORBELLn_ICRR Registers | 144 | |

78 | DOORBELLn Interrupt Condition Routing Register Field Descriptions | 144 | |

79 | RX CPPI Interrupt Condition Routing Register Field Descriptions | 145 | |

80 | TX CPPI Interrupt Condition Routing Register Field Descriptions | 146 | |

81 | LSU Interrupt Condition Routing Register Field Descriptions | 148 | |

82 | Error, Reset, and Special Event Interrupt Condition Routing Register Field Descriptions | 149 | |

83 | INTDSTn_DECODE Registers and the Associated Interrupt Destinations | 150 | |

84 | Interrupt Status Decode Register (INTDSTn_DECODE) Field Descriptions | 150 | |

85 | INTDSTn_RATE_CNTL Registers and the Associated Interrupt Destinations | 154 | |

86 | INTDSTn Interrupt Rate Control Register (INTDSTn_RATE_CNTL) Field Descriptions | 154 | |

87 | LSUn_REG0 Registers and the Associated LSUs | 155 | |

88 | LSUn Control Register 0 (LSUn_REG0) Field Descriptions | 155 | |

89 | LSUn_REG1 Registers and the Associated LSUs | 156 | |

90 | LSUn Control Register 1 (LSUn_REG1) Field Descriptions | 156 | |

91 | LSUn_REG2 Registers and the Associated LSUs | 157 | |

92 | LSUn Control Register 2 (LSUn_REG2) Field Descriptions | 157 | |

93 | LSUn_REG3 Registers and the Associated LSUs | 158 | |

94 | LSUn Control Register 3 (LSUn_REG3) Field Descriptions | 158 | |

95 | LSUn_REG4 Registers and the Associated LSUs | 159 | |

96 | LSUn Control Register 4 (LSUn_REG4) Field Descriptions | 159 | |

97 | LSUn_REG5 Registers and the Associated LSUs | 160 | |

98 | LSUn Control Register 5 (LSUn_REG5) Field Descriptions | 160 | |

SPRUE13A | List of Tables | 11 | |