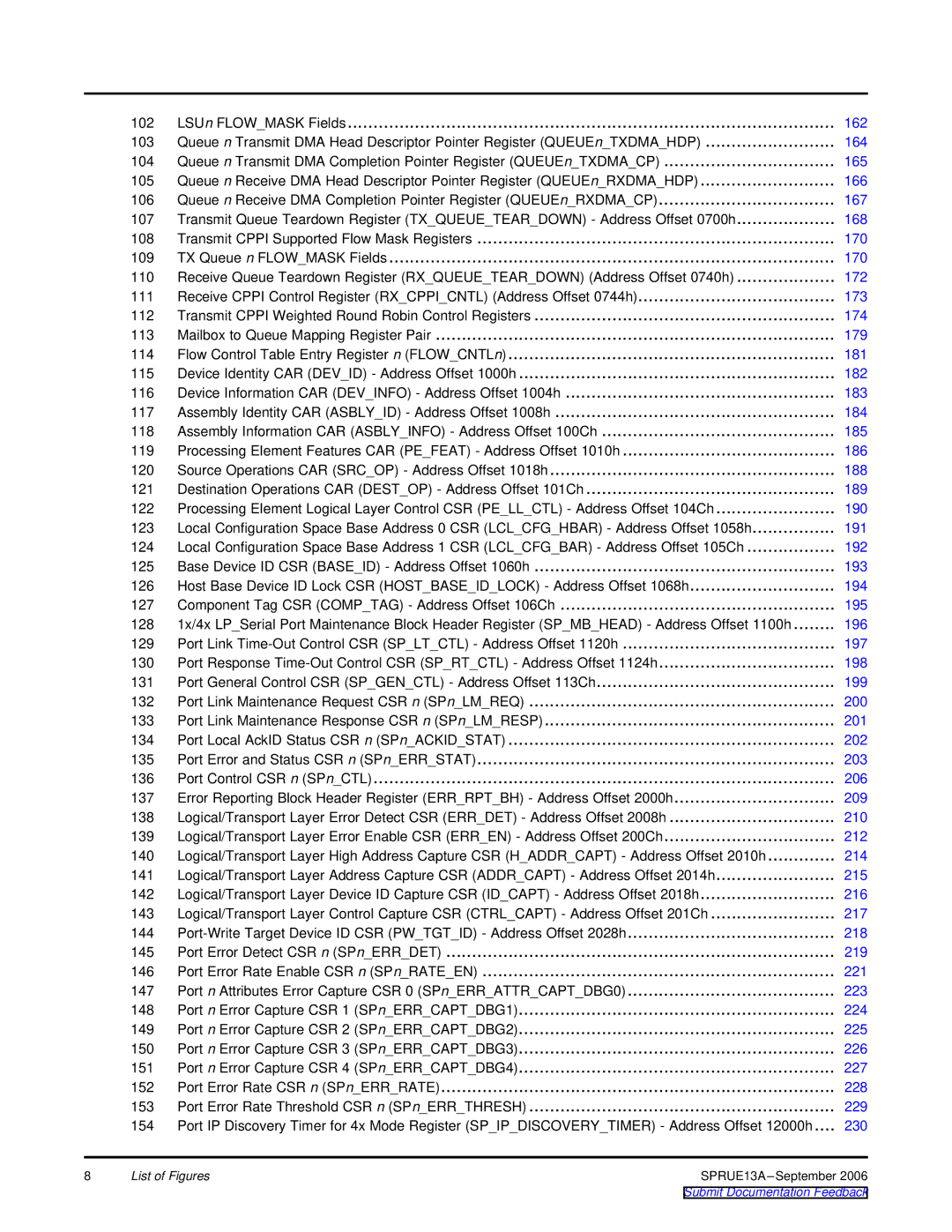

| 102 | LSUn FLOW_MASK Fields | 162 | |

| 103 | Queue n Transmit DMA Head Descriptor Pointer Register (QUEUEn_TXDMA_HDP) | ......................... | 164 |

| 104 | Queue n Transmit DMA Completion Pointer Register (QUEUEn_TXDMA_CP) | 165 | |

| 105 | Queue n Receive DMA Head Descriptor Pointer Register (QUEUEn_RXDMA_HDP) | 166 | |

| 106 | Queue n Receive DMA Completion Pointer Register (QUEUEn_RXDMA_CP) | 167 | |

| 107 | Transmit Queue Teardown Register (TX_QUEUE_TEAR_DOWN) - Address Offset 0700h | 168 | |

| 108 | Transmit CPPI Supported Flow Mask Registers | 170 | |

| 109 | TX Queue n FLOW_MASK Fields | 170 | |

| 110 | Receive Queue Teardown Register (RX_QUEUE_TEAR_DOWN) (Address Offset 0740h) | 172 | |

| 111 | Receive CPPI Control Register (RX_CPPI_CNTL) (Address Offset 0744h) | 173 | |

| 112 | Transmit CPPI Weighted Round Robin Control Registers | 174 | |

| 113 | Mailbox to Queue Mapping Register Pair | 179 | |

| 114 | Flow Control Table Entry Register n (FLOW_CNTLn) | 181 | |

| 115 | Device Identity CAR (DEV_ID) - Address Offset 1000h | 182 | |

| 116 | Device Information CAR (DEV_INFO) - Address Offset 1004h | 183 | |

| 117 | Assembly Identity CAR (ASBLY_ID) - Address Offset 1008h | 184 | |

| 118 | Assembly Information CAR (ASBLY_INFO) - Address Offset 100Ch | 185 | |

| 119 | Processing Element Features CAR (PE_FEAT) - Address Offset 1010h | 186 | |

| 120 | Source Operations CAR (SRC_OP) - Address Offset 1018h | 188 | |

| 121 | Destination Operations CAR (DEST_OP) - Address Offset 101Ch | 189 | |

| 122 | Processing Element Logical Layer Control CSR (PE_LL_CTL) - Address Offset 104Ch | 190 | |

| 123 | Local Configuration Space Base Address 0 CSR (LCL_CFG_HBAR) - Address Offset 1058h | 191 | |

| 124 | Local Configuration Space Base Address 1 CSR (LCL_CFG_BAR) - Address Offset 105Ch | 192 | |

| 125 | Base Device ID CSR (BASE_ID) - Address Offset 1060h | 193 | |

| 126 | Host Base Device ID Lock CSR (HOST_BASE_ID_LOCK) - Address Offset 1068h | 194 | |

| 127 | Component Tag CSR (COMP_TAG) - Address Offset 106Ch | 195 | |

| 128 | 1x/4x LP_Serial Port Maintenance Block Header Register (SP_MB_HEAD) - Address Offset 1100h | 196 | |

| 129 | Port Link | 197 | |

| 130 | Port Response | 198 | |

| 131 | Port General Control CSR (SP_GEN_CTL) - Address Offset 113Ch | 199 | |

| 132 | Port Link Maintenance Request CSR n (SPn_LM_REQ) | 200 | |

| 133 | Port Link Maintenance Response CSR n (SPn_LM_RESP) | 201 | |

| 134 | Port Local AckID Status CSR n (SPn_ACKID_STAT) | 202 | |

| 135 | Port Error and Status CSR n (SPn_ERR_STAT) | 203 | |

| 136 | Port Control CSR n (SPn_CTL) | 206 | |

| 137 | Error Reporting Block Header Register (ERR_RPT_BH) - Address Offset 2000h | 209 | |

| 138 | Logical/Transport Layer Error Detect CSR (ERR_DET) - Address Offset 2008h | 210 | |

| 139 | Logical/Transport Layer Error Enable CSR (ERR_EN) - Address Offset 200Ch | 212 | |

| 140 | Logical/Transport Layer High Address Capture CSR (H_ADDR_CAPT) - Address Offset 2010h | 214 | |

| 141 | Logical/Transport Layer Address Capture CSR (ADDR_CAPT) - Address Offset 2014h | 215 | |

| 142 | Logical/Transport Layer Device ID Capture CSR (ID_CAPT) - Address Offset 2018h | 216 | |

| 143 | Logical/Transport Layer Control Capture CSR (CTRL_CAPT) - Address Offset 201Ch | 217 | |

| 144 | 218 | ||

| 145 | Port Error Detect CSR n (SPn_ERR_DET) | 219 | |

| 146 | Port Error Rate Enable CSR n (SPn_RATE_EN) | 221 | |

| 147 | Port n Attributes Error Capture CSR 0 (SPn_ERR_ATTR_CAPT_DBG0) | 223 | |

| 148 | Port n Error Capture CSR 1 (SPn_ERR_CAPT_DBG1) | 224 | |

| 149 | Port n Error Capture CSR 2 (SPn_ERR_CAPT_DBG2) | 225 | |

| 150 | Port n Error Capture CSR 3 (SPn_ERR_CAPT_DBG3) | 226 | |

| 151 | Port n Error Capture CSR 4 (SPn_ERR_CAPT_DBG4) | 227 | |

| 152 | Port Error Rate CSR n (SPn_ERR_RATE) | 228 | |

| 153 | Port Error Rate Threshold CSR n (SPn_ERR_THRESH) | 229 | |

| 154 | Port IP Discovery Timer for 4x Mode Register (SP_IP_DISCOVERY_TIMER) - Address Offset 12000h .... | 230 | |

8 | List of Figures | SPRUE13A | ||