www.ti.com

SRIO Registers

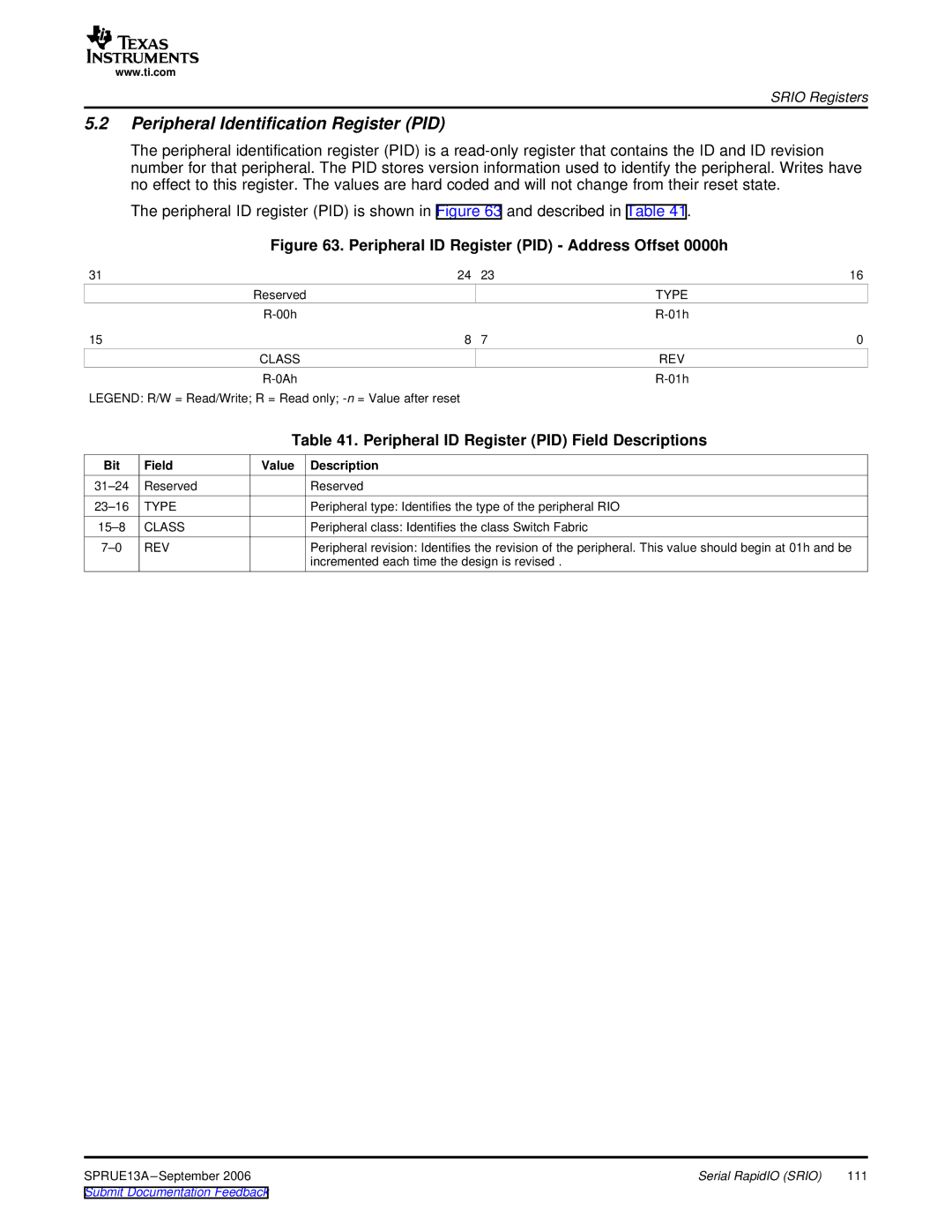

5.2Peripheral Identification Register (PID)

The peripheral identification register (PID) is a

The peripheral ID register (PID) is shown in Figure 63 and described in Table 41.

Figure 63. Peripheral ID Register (PID) - Address Offset 0000h

31 | 24 | 23 | 16 |

| Reserved |

| TYPE |

|

| ||

15 | 8 | 7 | 0 |

| CLASS |

| REV |

|

| ||

LEGEND: R/W = Read/Write; R = Read only; |

|

| |

|

| Table 41. Peripheral ID Register (PID) Field Descriptions |

Bit | Field | Value Description |

Reserved | Reserved | |

TYPE | Peripheral type: Identifies the type of the peripheral RIO | |

CLASS | Peripheral class: Identifies the class Switch Fabric | |

REV | Peripheral revision: Identifies the revision of the peripheral. This value should begin at 01h and be | |

|

| incremented each time the design is revised . |

SPRUE13A | Serial RapidIO (SRIO) | 111 |

Submit Documentation Feedback |

|

|