www.ti.com

SRIO Functional Description

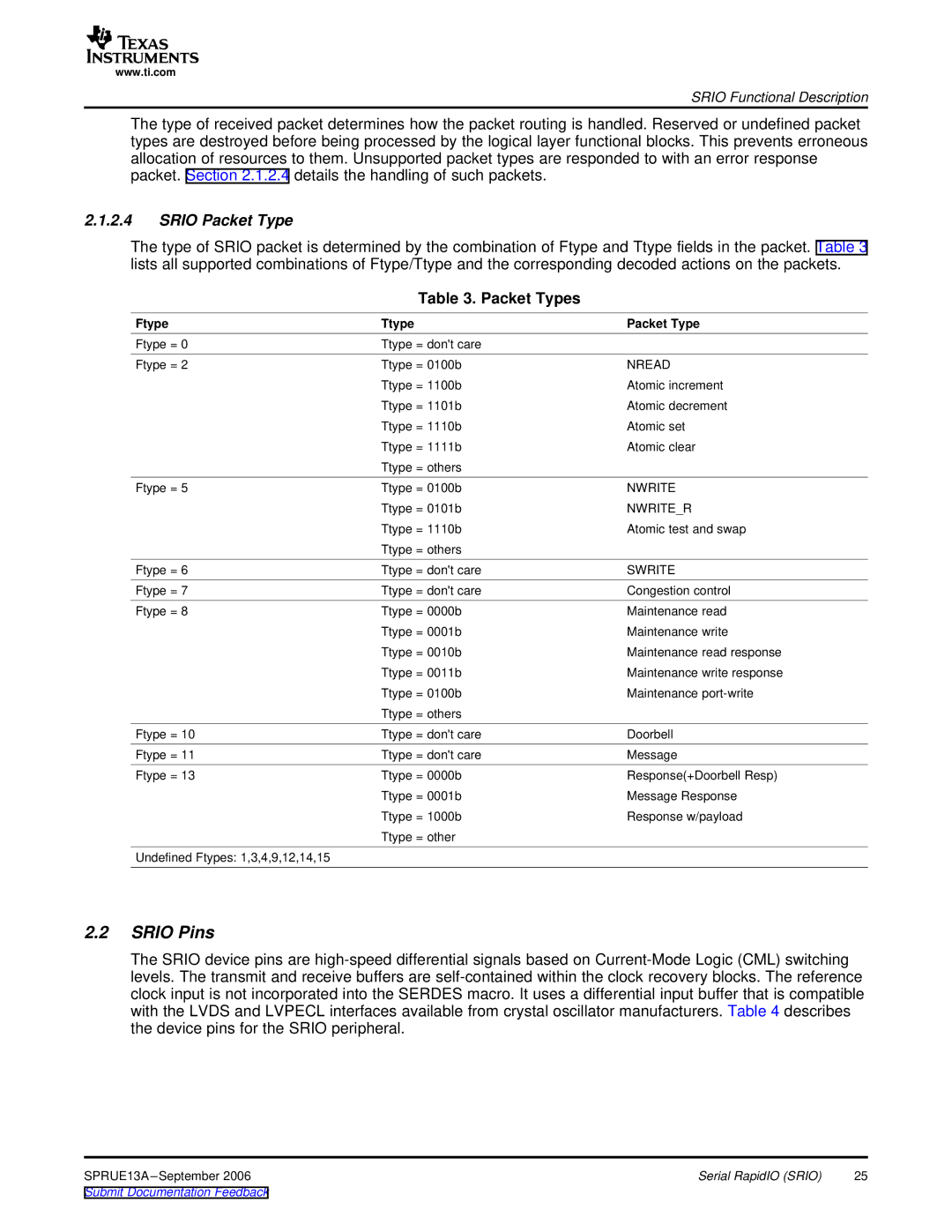

The type of received packet determines how the packet routing is handled. Reserved or undefined packet types are destroyed before being processed by the logical layer functional blocks. This prevents erroneous allocation of resources to them. Unsupported packet types are responded to with an error response packet. Section 2.1.2.4 details the handling of such packets.

2.1.2.4SRIO Packet Type

The type of SRIO packet is determined by the combination of Ftype and Ttype fields in the packet. Table 3 lists all supported combinations of Ftype/Ttype and the corresponding decoded actions on the packets.

Table 3. Packet Types

Ftype | Ttype | Packet Type |

Ftype = 0 | Ttype = don'tcare |

|

Ftype = 2 | Ttype = 0100b | NREAD |

| Ttype = 1100b | Atomic increment |

| Ttype = 1101b | Atomic decrement |

| Ttype = 1110b | Atomic set |

| Ttype = 1111b | Atomic clear |

| Ttype = others |

|

Ftype = 5 | Ttype = 0100b | NWRITE |

| Ttype = 0101b | NWRITE_R |

| Ttype = 1110b | Atomic test and swap |

| Ttype = others |

|

Ftype = 6 | Ttype = don'tcare | SWRITE |

Ftype = 7 | Ttype = don'tcare | Congestion control |

Ftype = 8 | Ttype = 0000b | Maintenance read |

| Ttype = 0001b | Maintenance write |

| Ttype = 0010b | Maintenance read response |

| Ttype = 0011b | Maintenance write response |

| Ttype = 0100b | Maintenance |

| Ttype = others |

|

Ftype = 10 | Ttype = don'tcare | Doorbell |

Ftype = 11 | Ttype = don'tcare | Message |

Ftype = 13 | Ttype = 0000b | Response(+Doorbell Resp) |

| Ttype = 0001b | Message Response |

| Ttype = 1000b | Response w/payload |

| Ttype = other |

|

Undefined Ftypes: 1,3,4,9,12,14,15 |

|

|

2.2SRIO Pins

The SRIO device pins are

SPRUE13A | Serial RapidIO (SRIO) | 25 |