www.ti.com

Interrupt Conditions

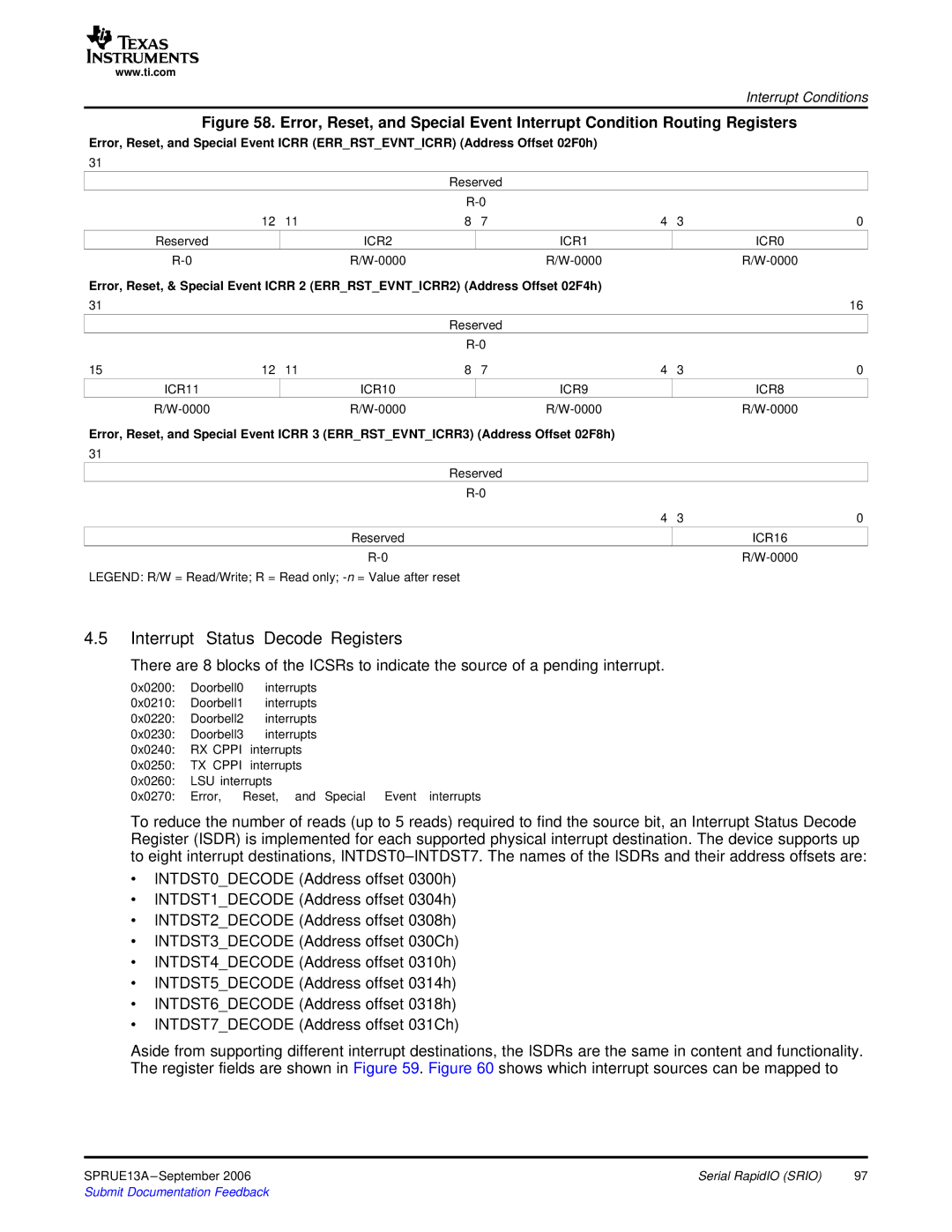

Figure 58. Error, Reset, and Special Event Interrupt Condition Routing Registers

Error, Reset, and Special Event ICRR (ERR_RST_EVNT_ICRR) (Address Offset 02F0h)

31 |

|

|

|

|

|

|

|

|

|

| Reserved |

|

|

| |

|

|

|

|

|

| ||

| 12 | 11 | 8 | 7 | 4 | 3 | 0 |

| Reserved |

| ICR2 |

| ICR1 |

| ICR0 |

|

|

|

| ||||

Error, Reset, & Special Event ICRR 2 (ERR_RST_EVNT_ICRR2) (Address Offset 02F4h) |

|

| |||||

31 |

|

|

|

|

|

| 16 |

|

|

| Reserved |

|

|

| |

|

|

|

|

|

| ||

15 | 12 | 11 | 8 | 7 | 4 | 3 | 0 |

| ICR11 |

| ICR10 |

| ICR9 |

| ICR8 |

|

|

|

| ||||

Error, Reset, and Special Event ICRR 3 (ERR_RST_EVNT_ICRR3) (Address Offset 02F8h) |

|

| |||||

31 |

|

|

|

|

|

|

|

|

|

| Reserved |

|

|

| |

|

|

|

|

|

| ||

|

|

|

|

| 4 | 3 | 0 |

|

|

| Reserved |

|

|

| ICR16 |

|

|

|

|

|

| ||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

|

| |||

4.5Interrupt Status Decode Registers

There are 8 blocks of the ICSRs to indicate the source of a pending interrupt.

0x0200: Doorbell0 interrupts

0x0210: Doorbell1 interrupts

0x0220: Doorbell2 interrupts

0x0230: Doorbell3 interrupts

0x0240: RX CPPI interrupts

0x0250: TX CPPI interrupts

0x0260: LSU interrupts

0x0270: Error, Reset, and Special Event interrupts

To reduce the number of reads (up to 5 reads) required to find the source bit, an Interrupt Status Decode Register (ISDR) is implemented for each supported physical interrupt destination. The device supports up to eight interrupt destinations,

∙INTDST0_DECODE (Address offset 0300h)

∙INTDST1_DECODE (Address offset 0304h)

∙INTDST2_DECODE (Address offset 0308h)

∙INTDST3_DECODE (Address offset 030Ch)

∙INTDST4_DECODE (Address offset 0310h)

∙INTDST5_DECODE (Address offset 0314h)

∙INTDST6_DECODE (Address offset 0318h)

∙INTDST7_DECODE (Address offset 031Ch)

Aside from supporting different interrupt destinations, the ISDRs are the same in content and functionality. The register fields are shown in Figure 59. Figure 60 shows which interrupt sources can be mapped to

SPRUE13A | Serial RapidIO (SRIO) | 97 |