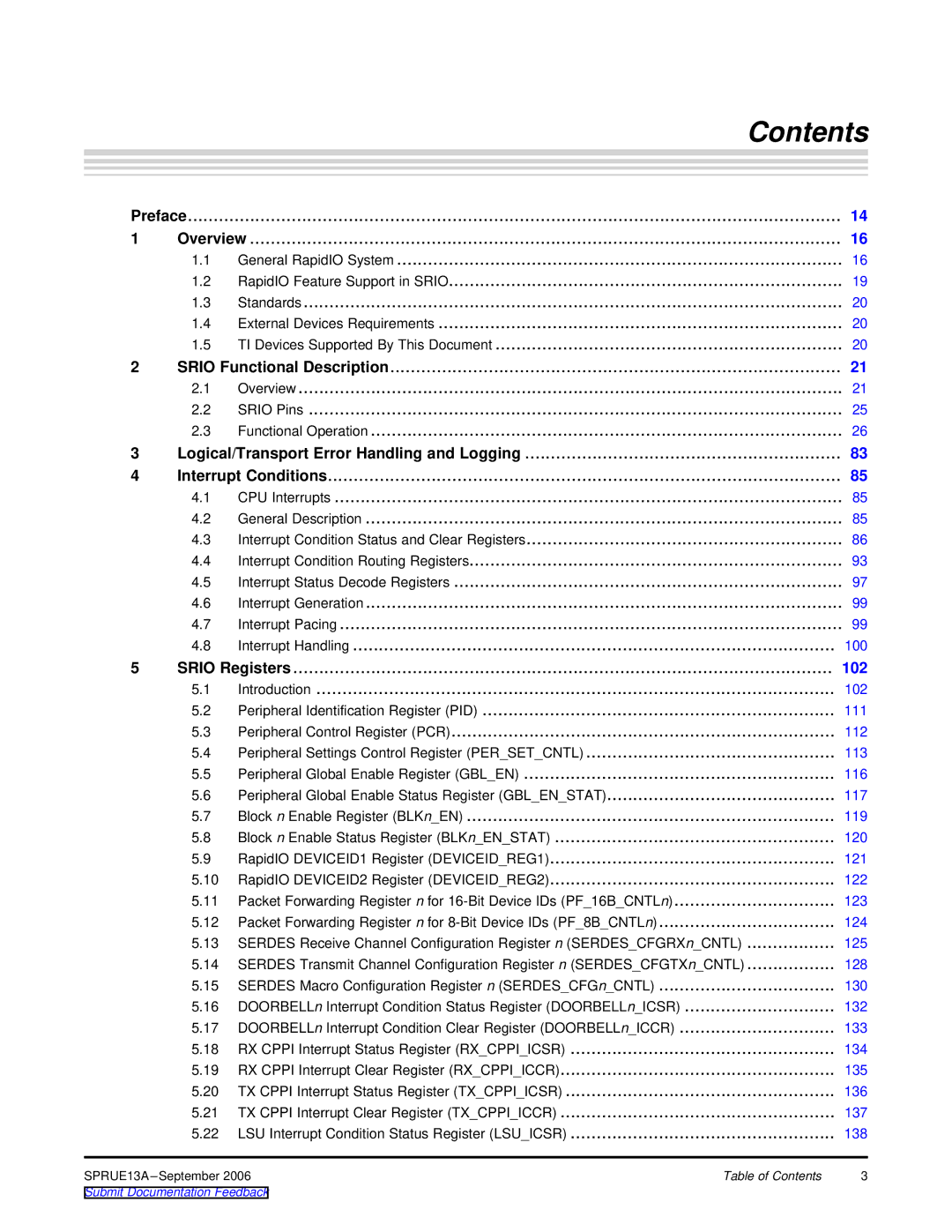

Contents

Preface | 14 | ||

1 | Overview | 16 | |

| 1.1 | General RapidIO System | 16 |

| 1.2 | RapidIO Feature Support in SRIO | 19 |

| 1.3 | Standards | 20 |

| 1.4 | External Devices Requirements | 20 |

| 1.5 | TI Devices Supported By This Document | 20 |

2 | SRIO Functional Description | 21 | |

| 2.1 | Overview | 21 |

| 2.2 | SRIO Pins | 25 |

| 2.3 | Functional Operation | 26 |

3 | Logical/Transport Error Handling and Logging | 83 | |

4 | Interrupt Conditions | 85 | |

| 4.1 | CPU Interrupts | 85 |

| 4.2 | General Description | 85 |

| 4.3 | Interrupt Condition Status and Clear Registers | 86 |

| 4.4 | Interrupt Condition Routing Registers | 93 |

| 4.5 | Interrupt Status Decode Registers | 97 |

| 4.6 | Interrupt Generation | 99 |

| 4.7 | Interrupt Pacing | 99 |

| 4.8 | Interrupt Handling | 100 |

5 | SRIO Registers | 102 | ||

| 5.1 | Introduction | 102 | |

| 5.2 | Peripheral Identification Register (PID) | 111 | |

| 5.3 | Peripheral Control Register (PCR) | 112 | |

| 5.4 | Peripheral Settings Control Register (PER_SET_CNTL) | 113 | |

| 5.5 | Peripheral Global Enable Register (GBL_EN) | 116 | |

| 5.6 | Peripheral Global Enable Status Register (GBL_EN_STAT) | 117 | |

| 5.7 | Block n Enable Register (BLKn_EN) | 119 | |

| 5.8 | Block n Enable Status Register (BLKn_EN_STAT) | 120 | |

| 5.9 | RapidIO DEVICEID1 Register (DEVICEID_REG1) | 121 | |

| 5.10 | RapidIO DEVICEID2 Register (DEVICEID_REG2) | 122 | |

| 5.11 | Packet Forwarding Register n for | 123 | |

| 5.12 | Packet Forwarding Register n for | 124 | |

| 5.13 | SERDES Receive Channel Configuration Register n (SERDES_CFGRXn_CNTL) | 125 | |

| 5.14 | SERDES Transmit Channel Configuration Register n (SERDES_CFGTXn_CNTL) | 128 | |

| 5.15 | SERDES Macro Configuration Register n (SERDES_CFGn_CNTL) | 130 | |

| 5.16 | DOORBELLn Interrupt Condition Status Register (DOORBELLn_ICSR) | 132 | |

| 5.17 | DOORBELLn Interrupt Condition Clear Register (DOORBELLn_ICCR) | 133 | |

| 5.18 | RX CPPI Interrupt Status Register (RX_CPPI_ICSR) | 134 | |

| 5.19 | RX CPPI Interrupt Clear Register (RX_CPPI_ICCR) | 135 | |

| 5.20 | TX CPPI Interrupt Status Register (TX_CPPI_ICSR) | 136 | |

| 5.21 | TX CPPI Interrupt Clear Register (TX_CPPI_ICCR) | 137 | |

| 5.22 | LSU Interrupt Condition Status Register (LSU_ICSR) | 138 | |

SPRUE13A | Table of Contents | 3 | ||