www.ti.com

SRIO Registers

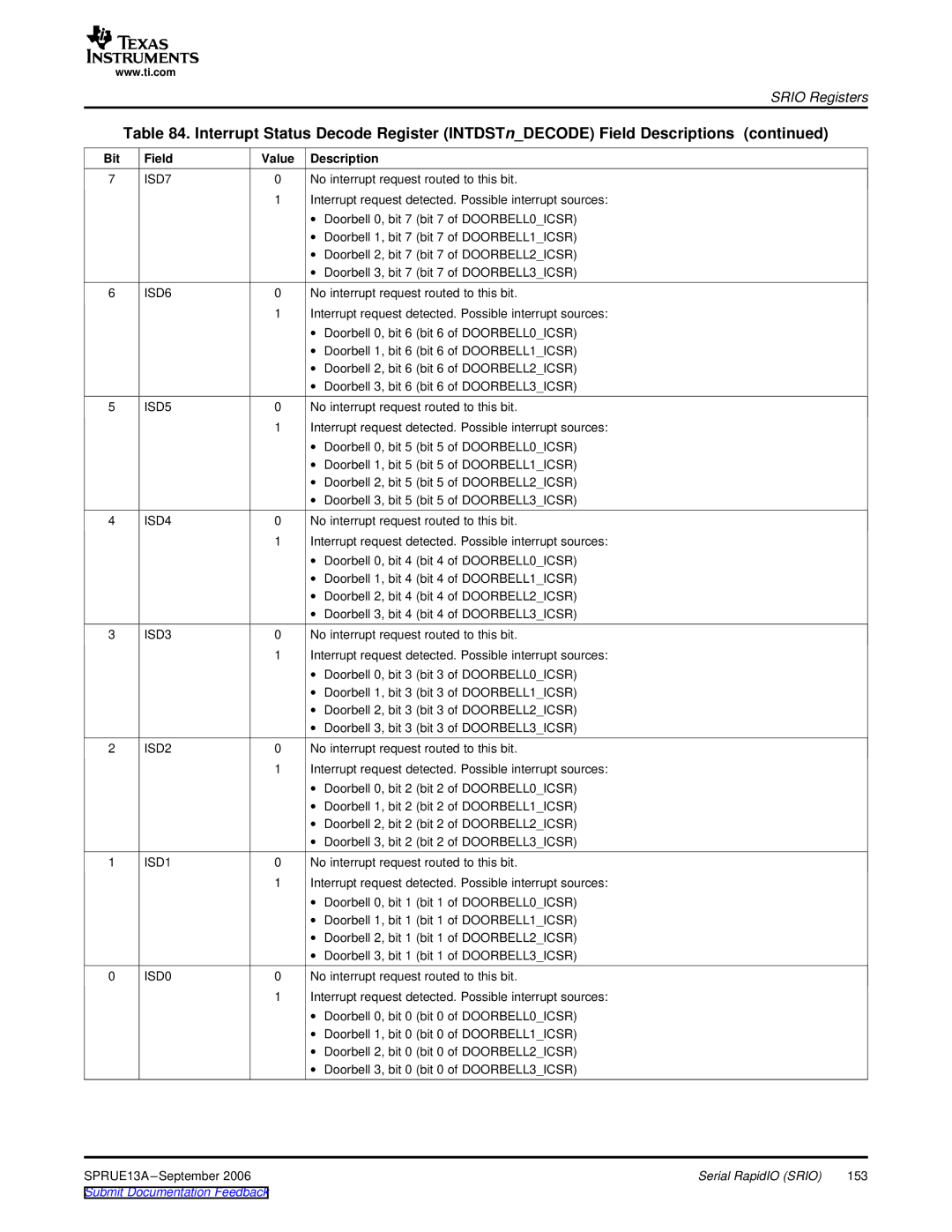

Table 84. Interrupt Status Decode Register (INTDSTn_DECODE) Field Descriptions (continued)

Bit | Field | Value | Description |

7 | ISD7 | 0 | No interrupt request routed to this bit. |

|

| 1 | Interrupt request detected. Possible interrupt sources: |

|

|

| ∙ Doorbell 0, bit 7 (bit 7 of DOORBELL0_ICSR) |

|

|

| ∙ Doorbell 1, bit 7 (bit 7 of DOORBELL1_ICSR) |

|

|

| ∙ Doorbell 2, bit 7 (bit 7 of DOORBELL2_ICSR) |

|

|

| ∙ Doorbell 3, bit 7 (bit 7 of DOORBELL3_ICSR) |

6 | ISD6 | 0 | No interrupt request routed to this bit. |

|

| 1 | Interrupt request detected. Possible interrupt sources: |

|

|

| ∙ Doorbell 0, bit 6 (bit 6 of DOORBELL0_ICSR) |

|

|

| ∙ Doorbell 1, bit 6 (bit 6 of DOORBELL1_ICSR) |

|

|

| ∙ Doorbell 2, bit 6 (bit 6 of DOORBELL2_ICSR) |

|

|

| ∙ Doorbell 3, bit 6 (bit 6 of DOORBELL3_ICSR) |

5 | ISD5 | 0 | No interrupt request routed to this bit. |

|

| 1 | Interrupt request detected. Possible interrupt sources: |

|

|

| ∙ Doorbell 0, bit 5 (bit 5 of DOORBELL0_ICSR) |

|

|

| ∙ Doorbell 1, bit 5 (bit 5 of DOORBELL1_ICSR) |

|

|

| ∙ Doorbell 2, bit 5 (bit 5 of DOORBELL2_ICSR) |

|

|

| ∙ Doorbell 3, bit 5 (bit 5 of DOORBELL3_ICSR) |

4 | ISD4 | 0 | No interrupt request routed to this bit. |

|

| 1 | Interrupt request detected. Possible interrupt sources: |

|

|

| ∙ Doorbell 0, bit 4 (bit 4 of DOORBELL0_ICSR) |

|

|

| ∙ Doorbell 1, bit 4 (bit 4 of DOORBELL1_ICSR) |

|

|

| ∙ Doorbell 2, bit 4 (bit 4 of DOORBELL2_ICSR) |

|

|

| ∙ Doorbell 3, bit 4 (bit 4 of DOORBELL3_ICSR) |

3 | ISD3 | 0 | No interrupt request routed to this bit. |

|

| 1 | Interrupt request detected. Possible interrupt sources: |

|

|

| ∙ Doorbell 0, bit 3 (bit 3 of DOORBELL0_ICSR) |

|

|

| ∙ Doorbell 1, bit 3 (bit 3 of DOORBELL1_ICSR) |

|

|

| ∙ Doorbell 2, bit 3 (bit 3 of DOORBELL2_ICSR) |

|

|

| ∙ Doorbell 3, bit 3 (bit 3 of DOORBELL3_ICSR) |

2 | ISD2 | 0 | No interrupt request routed to this bit. |

|

| 1 | Interrupt request detected. Possible interrupt sources: |

|

|

| ∙ Doorbell 0, bit 2 (bit 2 of DOORBELL0_ICSR) |

|

|

| ∙ Doorbell 1, bit 2 (bit 2 of DOORBELL1_ICSR) |

|

|

| ∙ Doorbell 2, bit 2 (bit 2 of DOORBELL2_ICSR) |

|

|

| ∙ Doorbell 3, bit 2 (bit 2 of DOORBELL3_ICSR) |

1 | ISD1 | 0 | No interrupt request routed to this bit. |

|

| 1 | Interrupt request detected. Possible interrupt sources: |

|

|

| ∙ Doorbell 0, bit 1 (bit 1 of DOORBELL0_ICSR) |

|

|

| ∙ Doorbell 1, bit 1 (bit 1 of DOORBELL1_ICSR) |

|

|

| ∙ Doorbell 2, bit 1 (bit 1 of DOORBELL2_ICSR) |

|

|

| ∙ Doorbell 3, bit 1 (bit 1 of DOORBELL3_ICSR) |

0 | ISD0 | 0 | No interrupt request routed to this bit. |

|

| 1 | Interrupt request detected. Possible interrupt sources: |

|

|

| ∙ Doorbell 0, bit 0 (bit 0 of DOORBELL0_ICSR) |

∙ Doorbell 1, bit 0 | (bit 0 of DOORBELL1_ICSR) | |

∙ | Doorbell 2, bit 0 | (bit 0 of DOORBELL2_ICSR) |

∙ | Doorbell 3, bit 0 | (bit 0 of DOORBELL3_ICSR) |

SPRUE13A | Serial RapidIO (SRIO) | 153 |

Submit Documentation Feedback |

|

|