www.ti.com

Interrupt Conditions

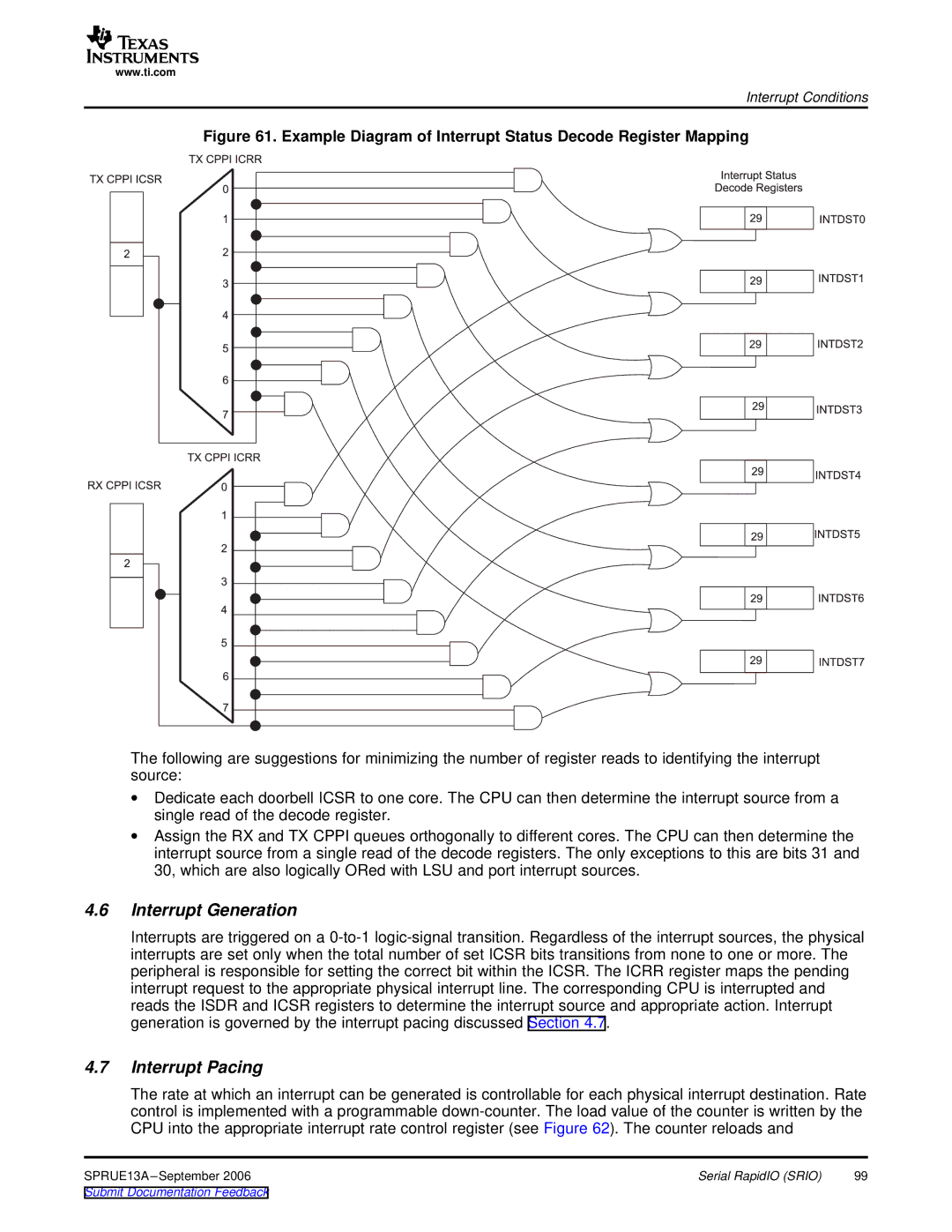

Figure 61. Example Diagram of Interrupt Status Decode Register Mapping

The following are suggestions for minimizing the number of register reads to identifying the interrupt source:

∙Dedicate each doorbell ICSR to one core. The CPU can then determine the interrupt source from a single read of the decode register.

∙Assign the RX and TX CPPI queues orthogonally to different cores. The CPU can then determine the interrupt source from a single read of the decode registers. The only exceptions to this are bits 31 and 30, which are also logically ORed with LSU and port interrupt sources.

4.6Interrupt Generation

Interrupts are triggered on a

4.7Interrupt Pacing

The rate at which an interrupt can be generated is controllable for each physical interrupt destination. Rate control is implemented with a programmable

SPRUE13A | Serial RapidIO (SRIO) | 99 |