www.ti.com

SRIO Registers

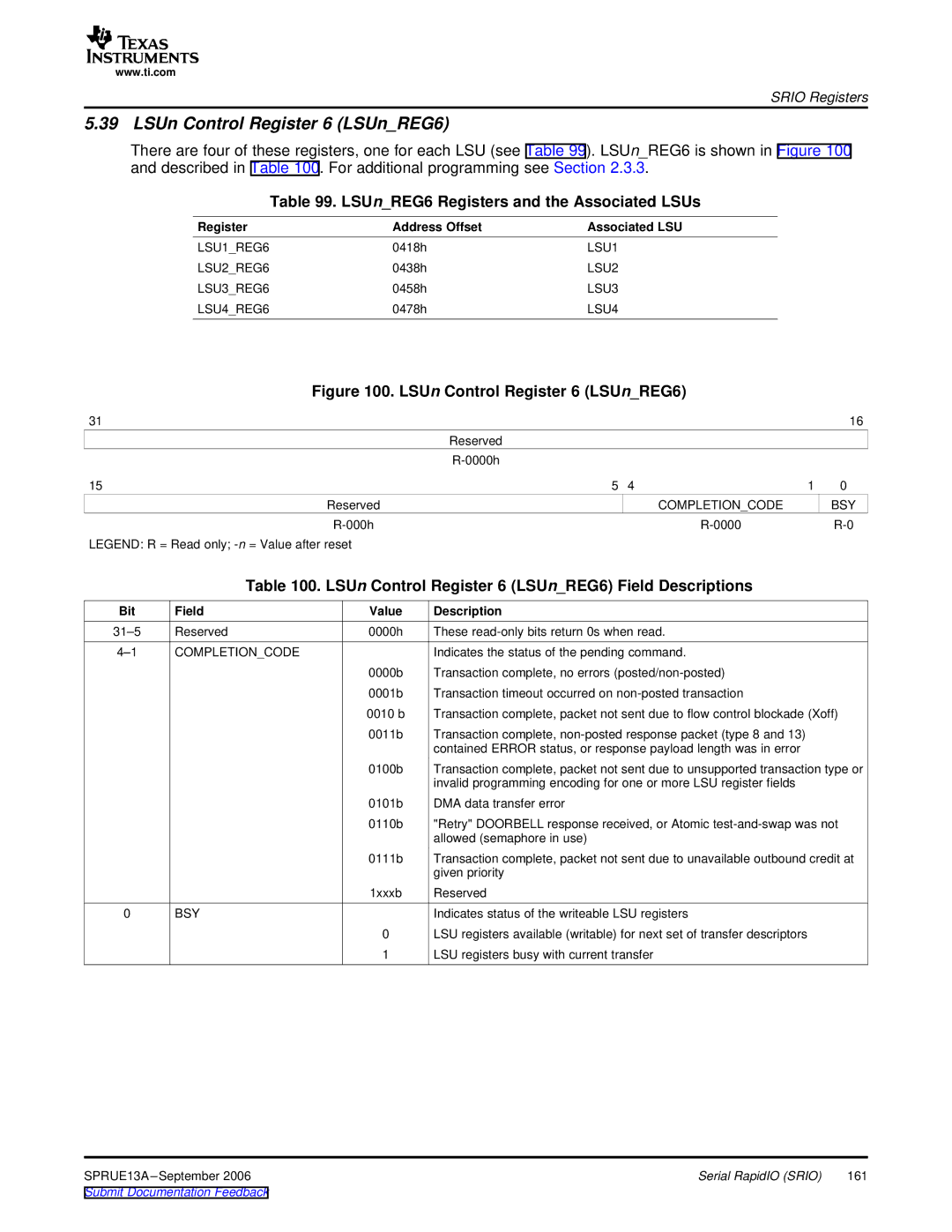

5.39 LSUn Control Register 6 (LSUn_REG6)

There are four of these registers, one for each LSU (see Table 99). LSUn_REG6 is shown in Figure 100 and described in Table 100. For additional programming see Section 2.3.3.

Table 99. LSUn_REG6 Registers and the Associated LSUs

Register | Address Offset | Associated LSU |

LSU1_REG6 | 0418h | LSU1 |

LSU2_REG6 | 0438h | LSU2 |

LSU3_REG6 | 0458h | LSU3 |

LSU4_REG6 | 0478h | LSU4 |

Figure 100. LSUn Control Register 6 (LSUn_REG6)

31 |

|

|

| 16 |

| Reserved |

|

|

|

|

|

|

| |

15 | 5 | 4 | 1 | 0 |

Reserved |

| COMPLETION_CODE |

| BSY |

|

| |||

LEGEND: R = Read only; |

|

|

|

|

Table 100. LSUn Control Register 6 (LSUn_REG6) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0000h | These | |

COMPLETION_CODE |

| Indicates the status of the pending command. | |

|

| 0000b | Transaction complete, no errors |

|

| 0001b | Transaction timeout occurred on |

|

| 0010 b | Transaction complete, packet not sent due to flow control blockade (Xoff) |

|

| 0011b | Transaction complete, |

|

|

| contained ERROR status, or response payload length was in error |

|

| 0100b | Transaction complete, packet not sent due to unsupported transaction type or |

|

|

| invalid programming encoding for one or more LSU register fields |

|

| 0101b | DMA data transfer error |

|

| 0110b | "Retry" DOORBELL response received, or Atomic |

|

|

| allowed (semaphore in use) |

|

| 0111b | Transaction complete, packet not sent due to unavailable outbound credit at |

|

|

| given priority |

|

| 1xxxb | Reserved |

0 | BSY |

| Indicates status of the writeable LSU registers |

|

| 0 | LSU registers available (writable) for next set of transfer descriptors |

|

| 1 | LSU registers busy with current transfer |

SPRUE13A | Serial RapidIO (SRIO) | 161 |

Submit Documentation Feedback |

|

|