www.ti.com

SRIO Registers

5 SRIO Registers

5.1Introduction

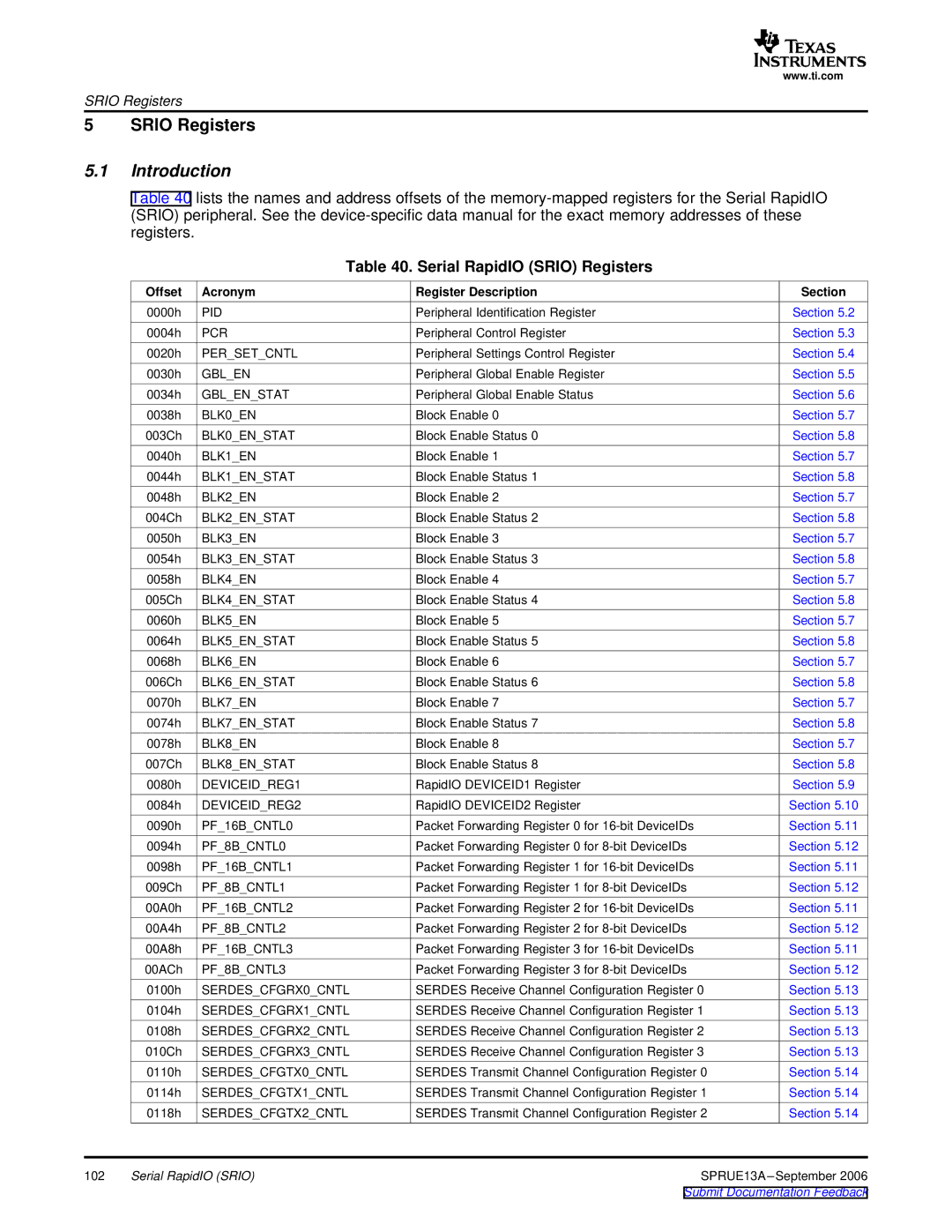

Table 40 lists the names and address offsets of the

Table 40. Serial RapidIO (SRIO) Registers

| Offset | Acronym | Register Description | Section |

| 0000h | PID | Peripheral Identification Register | Section 5.2 |

| 0004h | PCR | Peripheral Control Register | Section 5.3 |

| 0020h | PER_SET_CNTL | Peripheral Settings Control Register | Section 5.4 |

| 0030h | GBL_EN | Peripheral Global Enable Register | Section 5.5 |

| 0034h | GBL_EN_STAT | Peripheral Global Enable Status | Section 5.6 |

| 0038h | BLK0_EN | Block Enable 0 | Section 5.7 |

| 003Ch | BLK0_EN_STAT | Block Enable Status 0 | Section 5.8 |

| 0040h | BLK1_EN | Block Enable 1 | Section 5.7 |

| 0044h | BLK1_EN_STAT | Block Enable Status 1 | Section 5.8 |

| 0048h | BLK2_EN | Block Enable 2 | Section 5.7 |

| 004Ch | BLK2_EN_STAT | Block Enable Status 2 | Section 5.8 |

| 0050h | BLK3_EN | Block Enable 3 | Section 5.7 |

| 0054h | BLK3_EN_STAT | Block Enable Status 3 | Section 5.8 |

| 0058h | BLK4_EN | Block Enable 4 | Section 5.7 |

| 005Ch | BLK4_EN_STAT | Block Enable Status 4 | Section 5.8 |

| 0060h | BLK5_EN | Block Enable 5 | Section 5.7 |

| 0064h | BLK5_EN_STAT | Block Enable Status 5 | Section 5.8 |

| 0068h | BLK6_EN | Block Enable 6 | Section 5.7 |

| 006Ch | BLK6_EN_STAT | Block Enable Status 6 | Section 5.8 |

| 0070h | BLK7_EN | Block Enable 7 | Section 5.7 |

| 0074h | BLK7_EN_STAT | Block Enable Status 7 | Section 5.8 |

| 0078h | BLK8_EN | Block Enable 8 | Section 5.7 |

| 007Ch | BLK8_EN_STAT | Block Enable Status 8 | Section 5.8 |

| 0080h | DEVICEID_REG1 | RapidIO DEVICEID1 Register | Section 5.9 |

| 0084h | DEVICEID_REG2 | RapidIO DEVICEID2 Register | Section 5.10 |

| 0090h | PF_16B_CNTL0 | Packet Forwarding Register 0 for | Section 5.11 |

| 0094h | PF_8B_CNTL0 | Packet Forwarding Register 0 for | Section 5.12 |

| 0098h | PF_16B_CNTL1 | Packet Forwarding Register 1 for | Section 5.11 |

| 009Ch | PF_8B_CNTL1 | Packet Forwarding Register 1 for | Section 5.12 |

| 00A0h | PF_16B_CNTL2 | Packet Forwarding Register 2 for | Section 5.11 |

| 00A4h | PF_8B_CNTL2 | Packet Forwarding Register 2 for | Section 5.12 |

| 00A8h | PF_16B_CNTL3 | Packet Forwarding Register 3 for | Section 5.11 |

| 00ACh | PF_8B_CNTL3 | Packet Forwarding Register 3 for | Section 5.12 |

| 0100h | SERDES_CFGRX0_CNTL | SERDES Receive Channel Configuration Register 0 | Section 5.13 |

| 0104h | SERDES_CFGRX1_CNTL | SERDES Receive Channel Configuration Register 1 | Section 5.13 |

| 0108h | SERDES_CFGRX2_CNTL | SERDES Receive Channel Configuration Register 2 | Section 5.13 |

| 010Ch | SERDES_CFGRX3_CNTL | SERDES Receive Channel Configuration Register 3 | Section 5.13 |

| 0110h | SERDES_CFGTX0_CNTL | SERDES Transmit Channel Configuration Register 0 | Section 5.14 |

| 0114h | SERDES_CFGTX1_CNTL | SERDES Transmit Channel Configuration Register 1 | Section 5.14 |

| 0118h | SERDES_CFGTX2_CNTL | SERDES Transmit Channel Configuration Register 2 | Section 5.14 |

102 | Serial RapidIO (SRIO) | SPRUE13A | ||

|

|

| Submit Documentation Feedback | |