www.ti.com

SRIO Registers

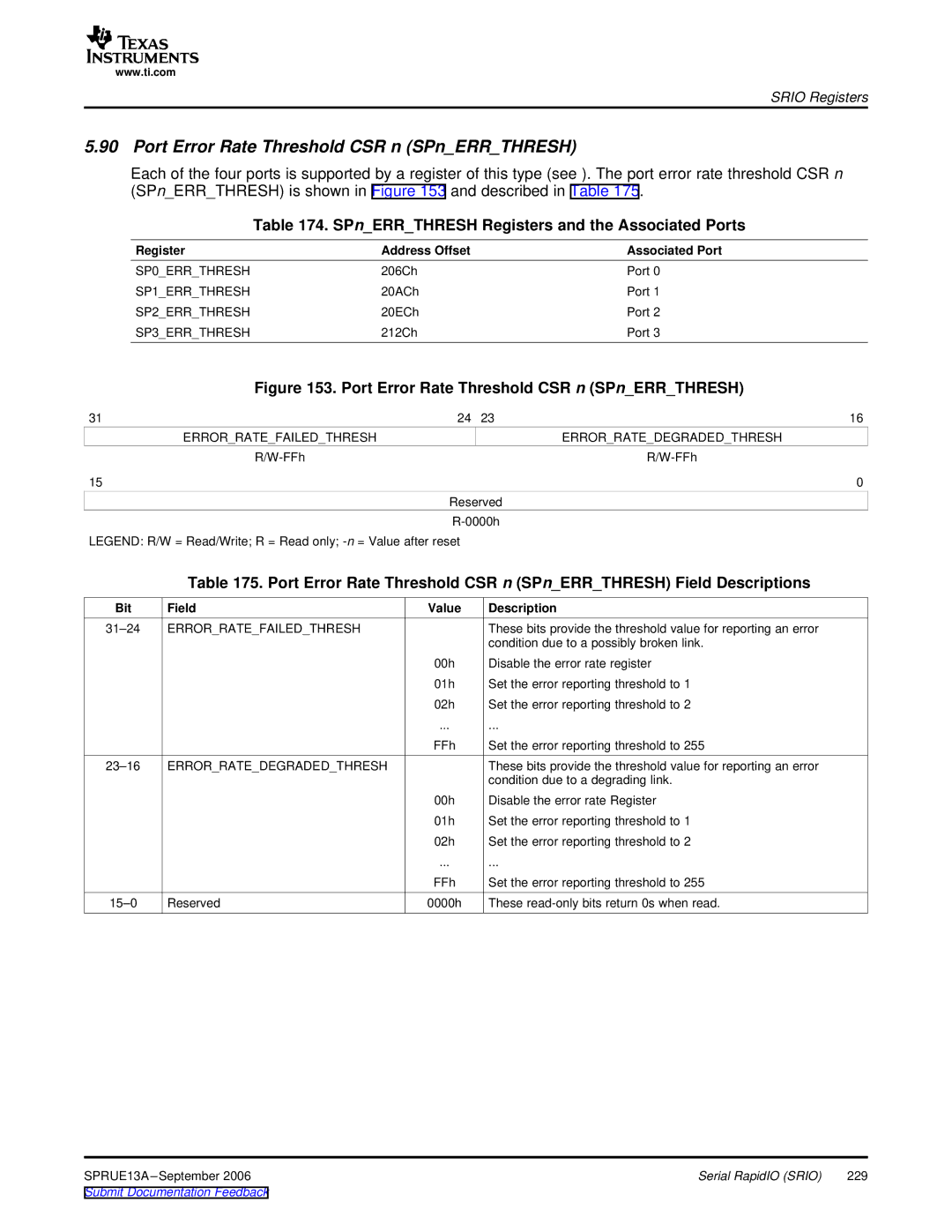

5.90 Port Error Rate Threshold CSR n (SPn_ERR_THRESH)

Each of the four ports is supported by a register of this type (see ). The port error rate threshold CSR n (SPn_ERR_THRESH) is shown in Figure 153 and described in Table 175.

Table 174. SPn_ERR_THRESH Registers and the Associated Ports

Register | Address Offset | Associated Port |

SP0_ERR_THRESH | 206Ch | Port 0 |

SP1_ERR_THRESH | 20ACh | Port 1 |

SP2_ERR_THRESH | 20ECh | Port 2 |

SP3_ERR_THRESH | 212Ch | Port 3 |

Figure 153. Port Error Rate Threshold CSR n (SPn_ERR_THRESH)

31 | 24 | 23 | 16 |

ERROR_RATE_FAILED_THRESH |

|

| ERROR_RATE_DEGRADED_THRESH |

|

| ||

15 |

|

| 0 |

| Reserved |

| |

LEGEND: R/W = Read/Write; R = Read only;

Table 175. Port Error Rate Threshold CSR n (SPn_ERR_THRESH) Field Descriptions

Bit | Field | Value | Description |

ERROR_RATE_FAILED_THRESH |

| These bits provide the threshold value for reporting an error | |

|

|

| condition due to a possibly broken link. |

|

| 00h | Disable the error rate register |

|

| 01h | Set the error reporting threshold to 1 |

|

| 02h | Set the error reporting threshold to 2 |

|

| ... | ... |

|

| FFh | Set the error reporting threshold to 255 |

ERROR_RATE_DEGRADED_THRESH |

| These bits provide the threshold value for reporting an error | |

|

|

| condition due to a degrading link. |

|

| 00h | Disable the error rate Register |

|

| 01h | Set the error reporting threshold to 1 |

|

| 02h | Set the error reporting threshold to 2 |

|

| ... | ... |

|

| FFh | Set the error reporting threshold to 255 |

Reserved | 0000h | These |

SPRUE13A | Serial RapidIO (SRIO) | 229 |

Submit Documentation Feedback |

|

|